Patents

Literature

168results about How to "Improve product yield" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

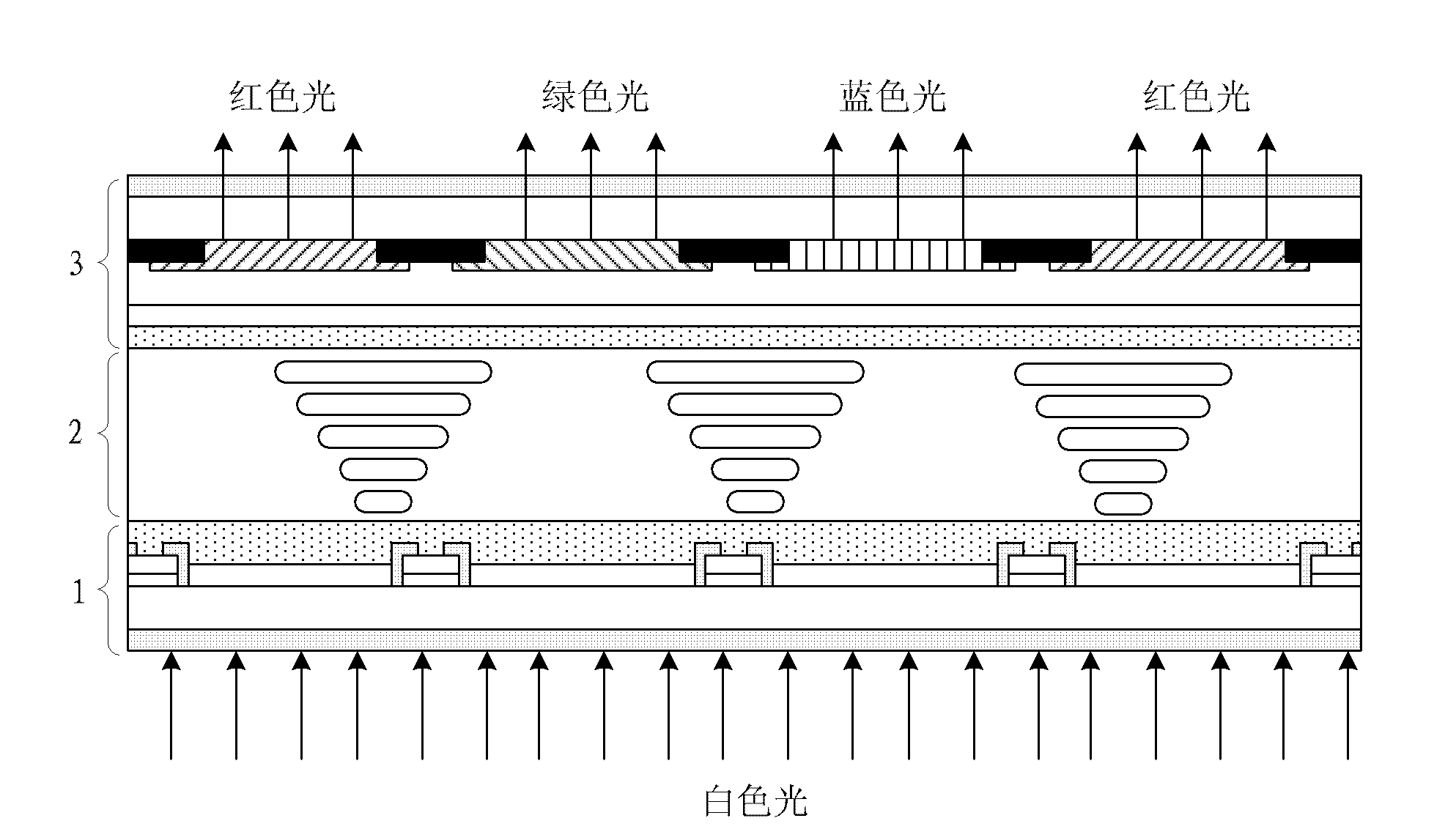

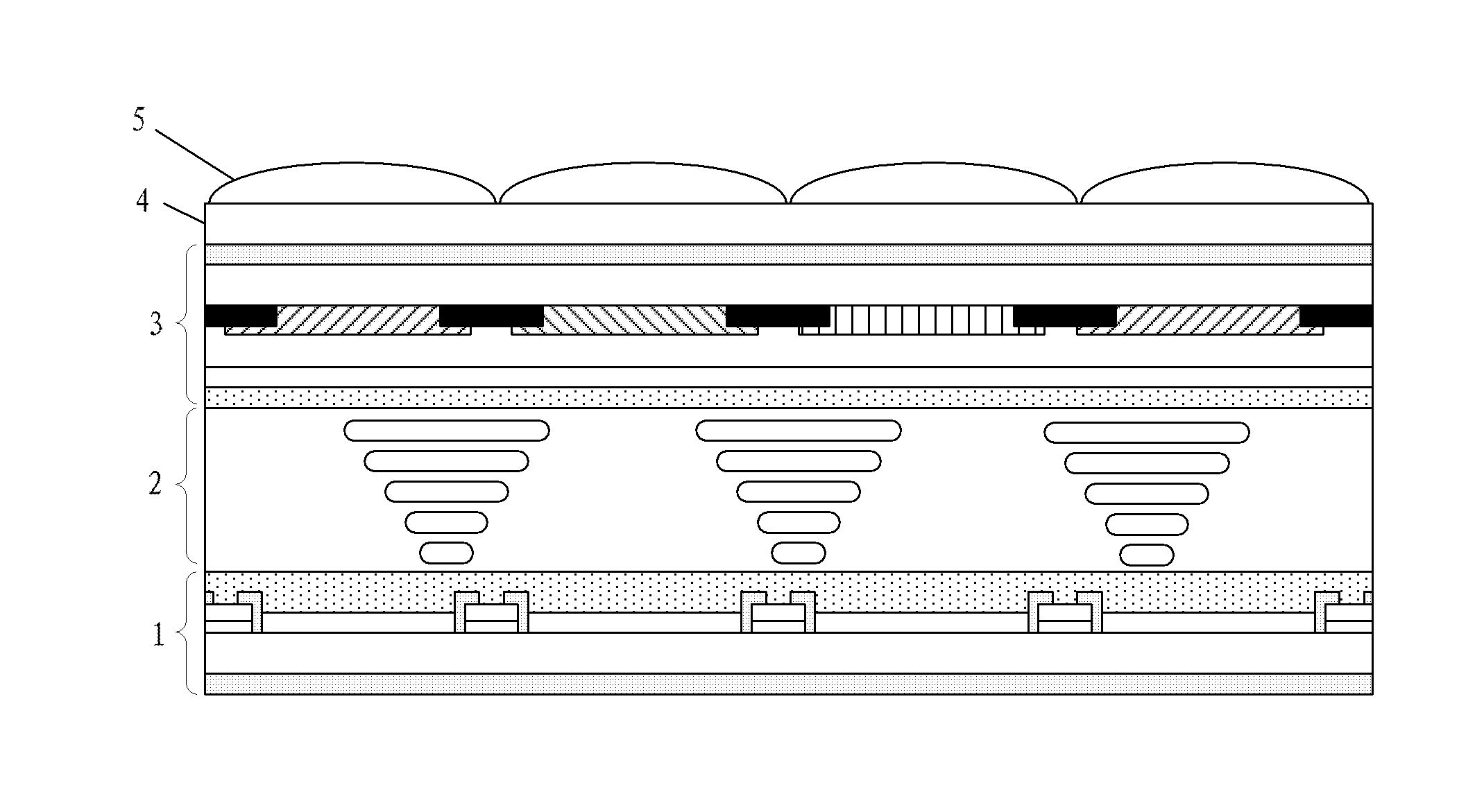

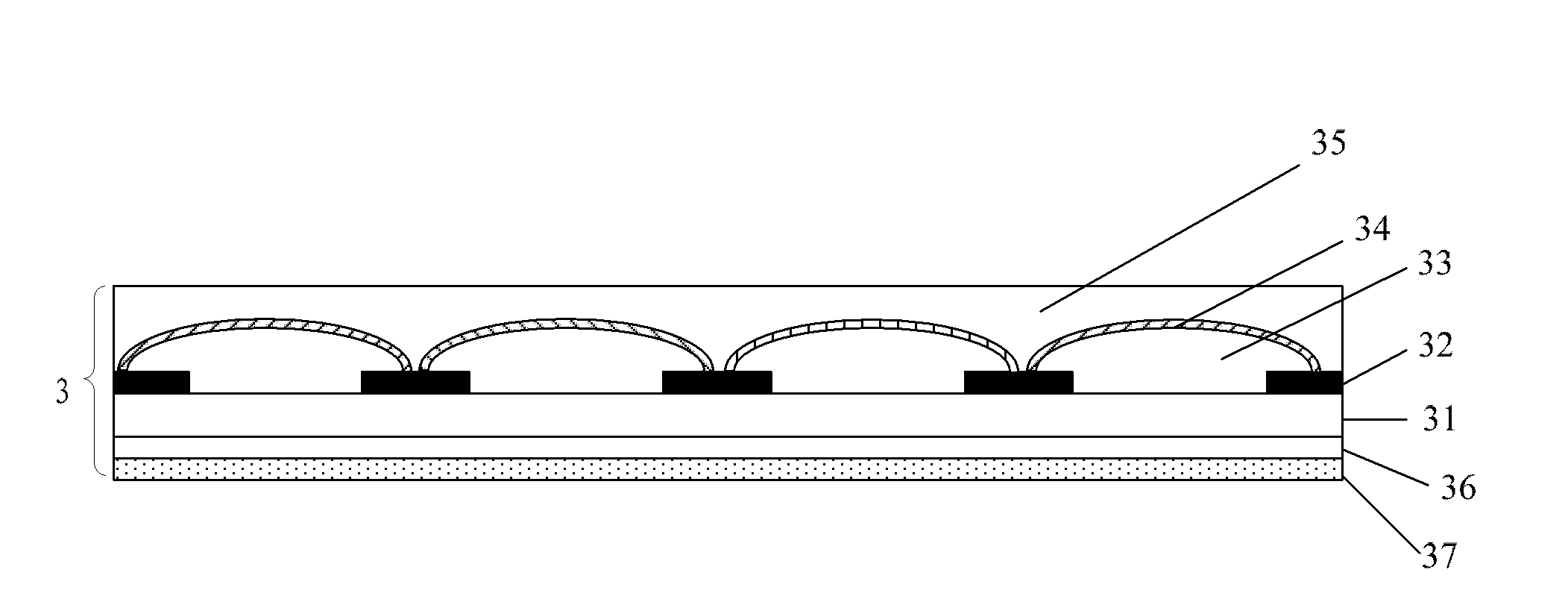

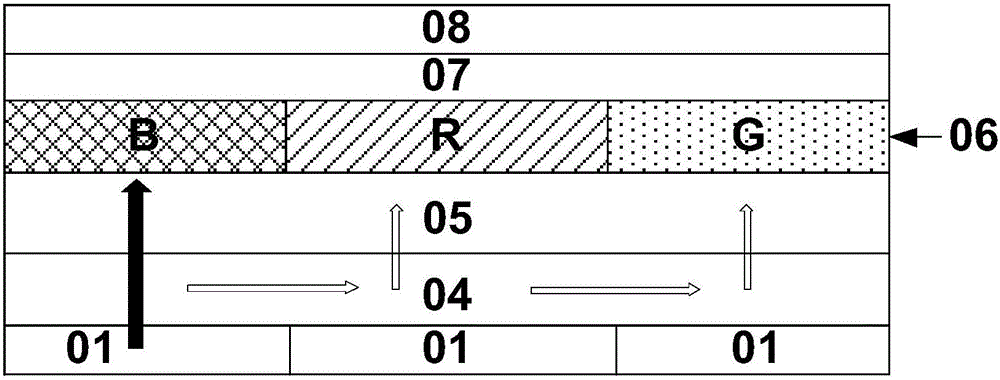

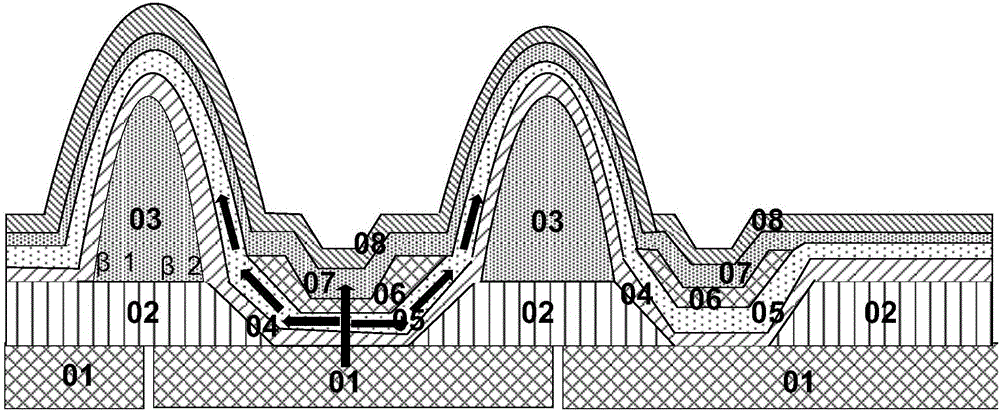

Display device, liquid crystal panel, color filter and manufacturing method thereof

InactiveCN102289016ASmooth productionImprove product yieldOptical filtersNon-linear opticsColor filter arrayLiquid crystal

The invention provides a display device, a liquid crystal panel, a color filter and a manufacturing method thereof. The color filter includes: a substrate; a black matrix formed on one side of the substrate; and a colored lenticular lens formed between the black matrices. By directly forming a lenticular lens in the color filter, the present invention can integrate the production process of naked-eye 3D display products, reduce process difficulty, and improve product quality.

Owner:SHENZHEN SUPER PERFECT OPTICS LTD

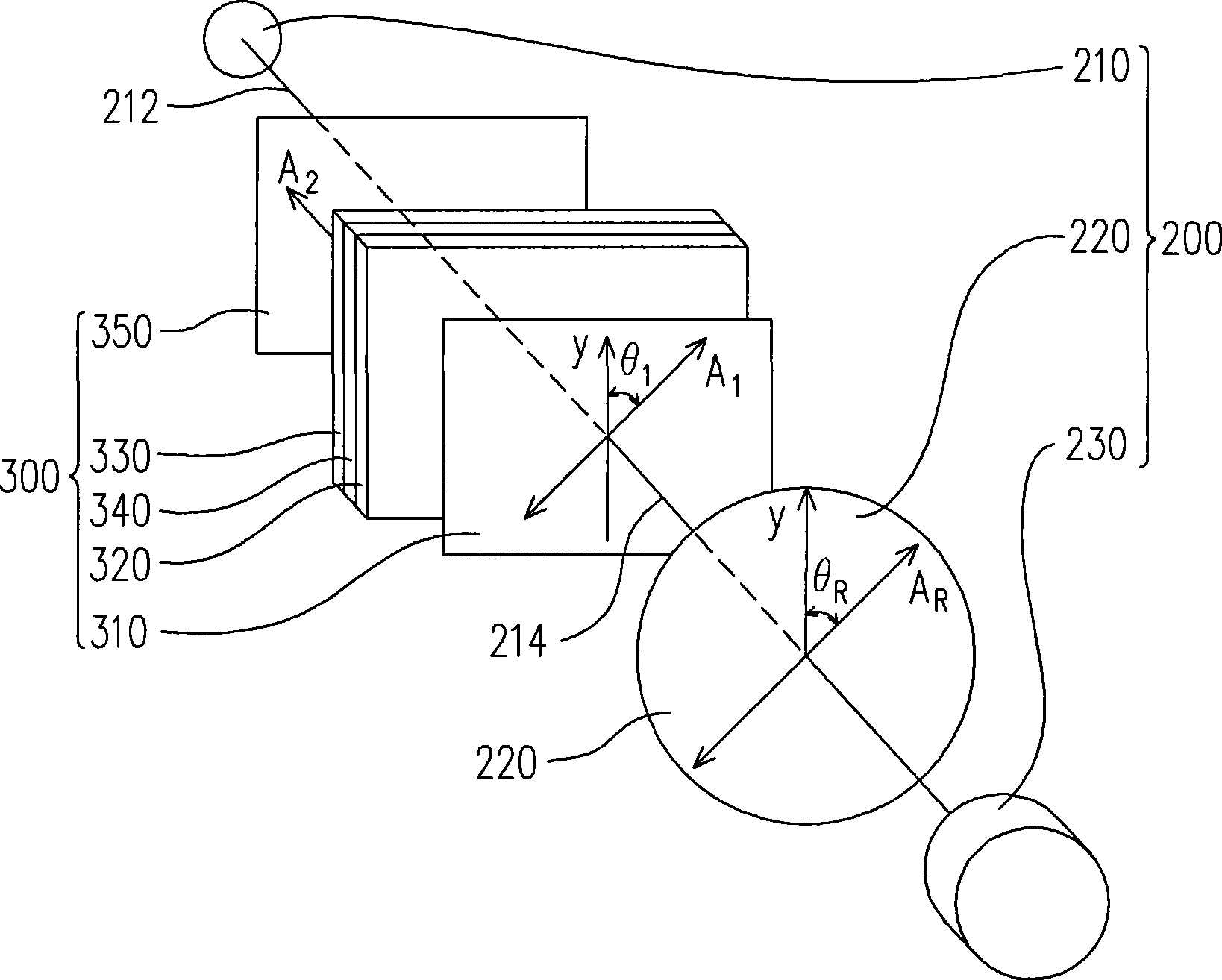

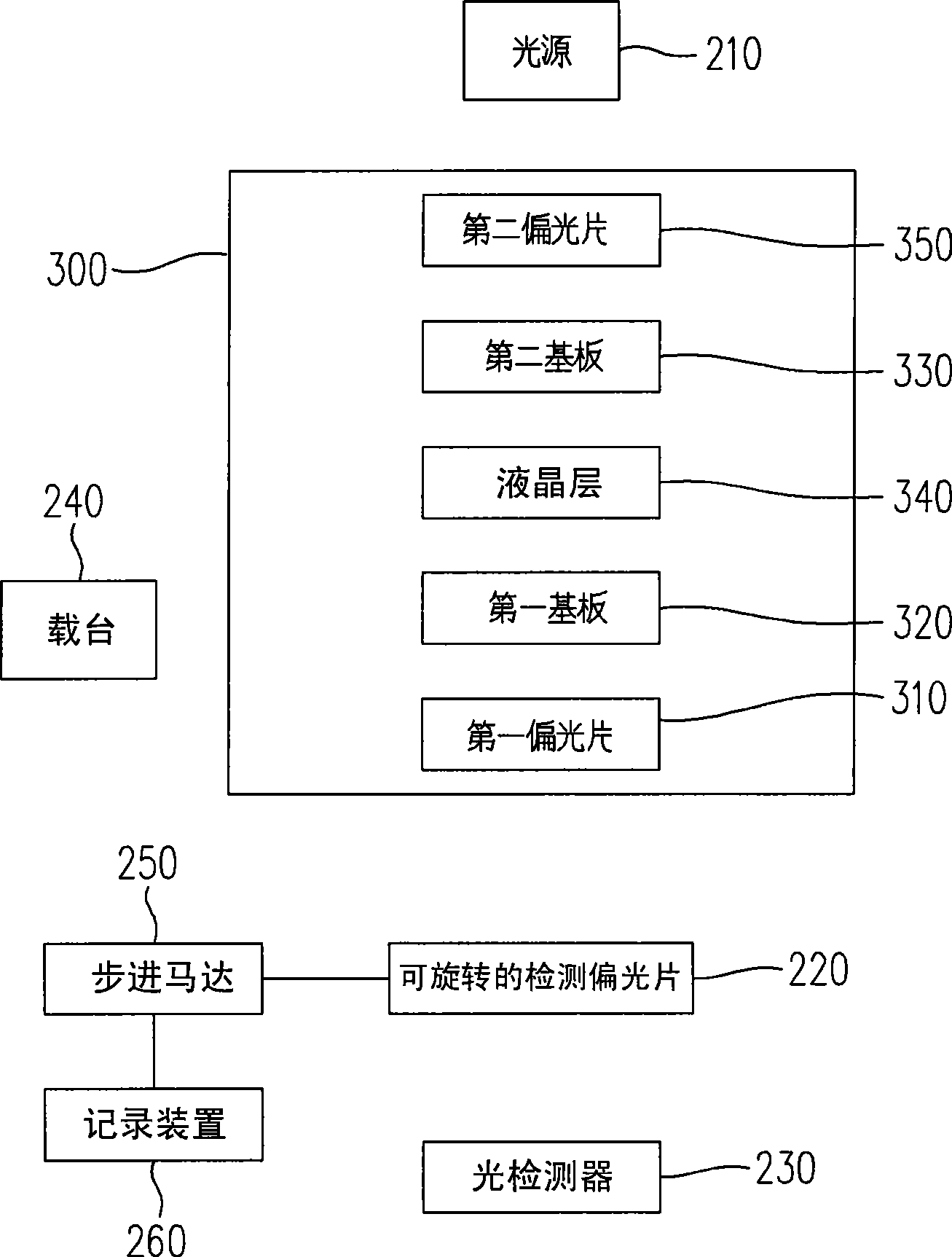

Detection apparatus and detection method

InactiveCN101369059AFast detection methodImprove product yieldOptical apparatus testingNon-linear opticsOptical pathPolarizer

The invention relates to a detecting device, which is suitable for detecting the angle of a light absorption axis of a first polarizer of a liquid crystal panel, and the liquid crystal panel comprises a first baseplate, a second baseplate and a liquid layer. The detecting device includes a light source, a rotatable detecting polarizer and a light detector. The light source is arranged at one side of the liquid crystal panel, and the liquid crystal panel is arranged on the optical path of the light source. The rotatable detecting polarizer is arranged at the other side of the liquid crystal panel and is arranged on the optical path of the light source, and the first polarizer is arranged between the baseplate and the rotatable detecting polarizer. The optical detector is arranged on the optical path of the light source, and the optical detector and the first polarizer are respectively arranged at two sides of the rotatable detecting polarizer; so using the detecting device can rapidly detect the angle of the light absorption axis of the first polarizer.

Owner:CHUNGHWA PICTURE TUBES LTD

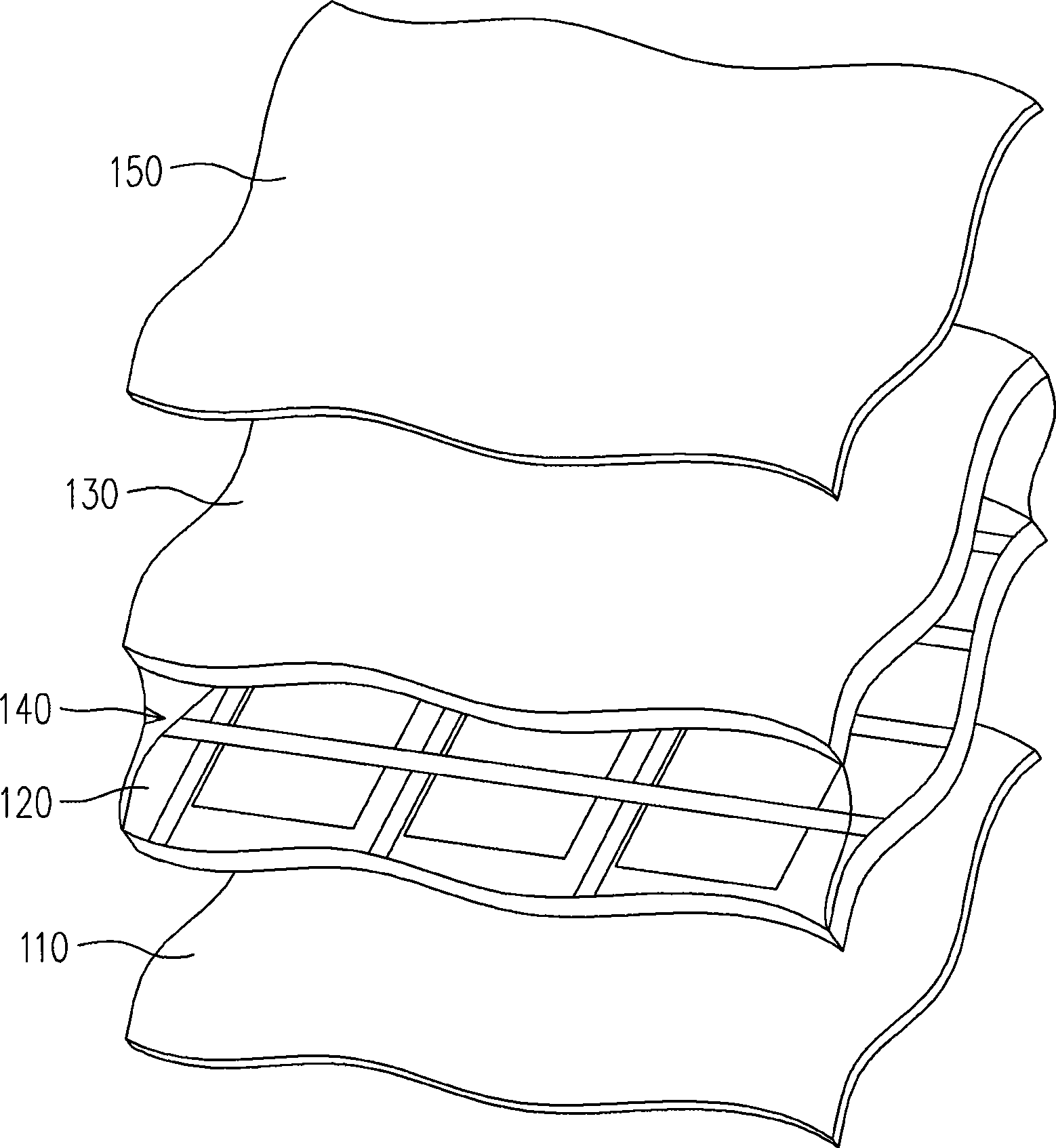

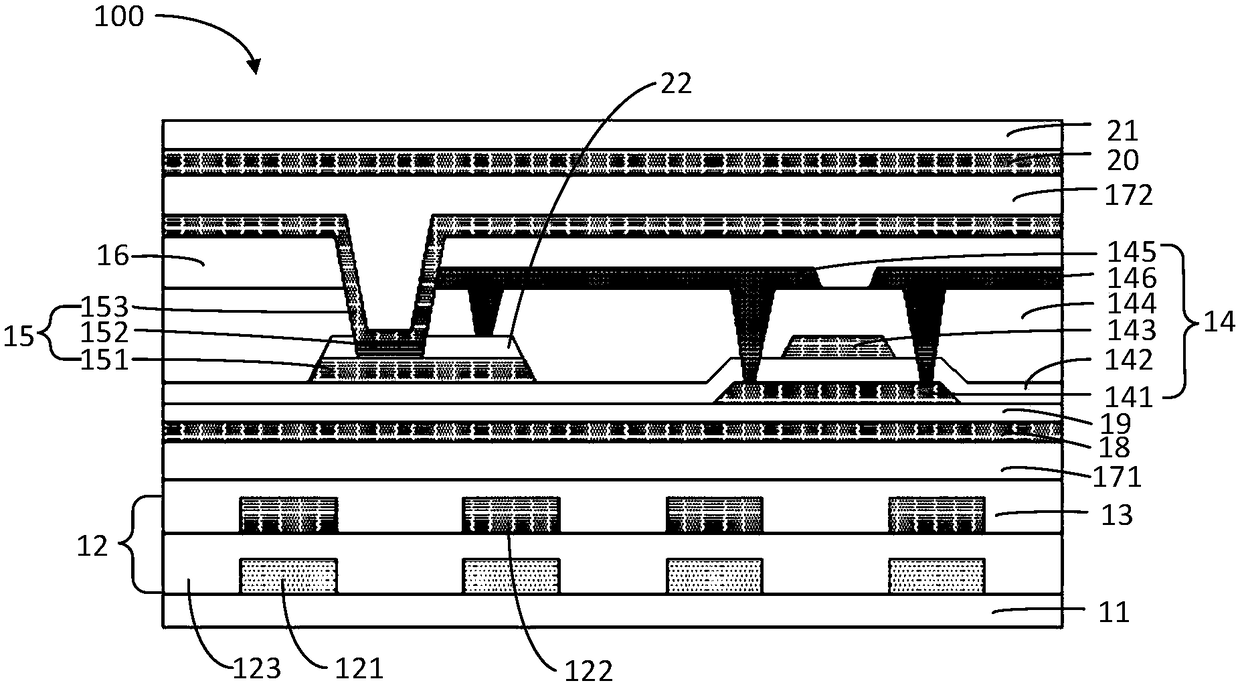

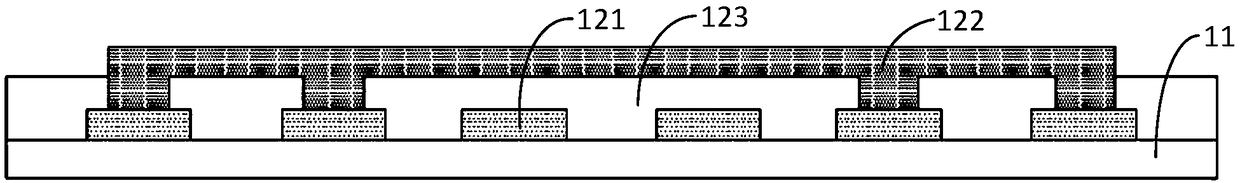

A touch display panel and a manufacturing method thereof

ActiveCN109407893AImprove product yieldProcess impactInput/output processes for data processingOrganic light emitting deviceLight-emitting diode

The invention provides a touch display panel and a manufacturing method. The touch display panel comprises a substrate, a touch layer, a protective layer, an array substrate and an organic light-emitting device. The touch layer comprises a touch pattern layer, a first insulating layer and a bridging layer. The organic light emitting device includes an anode, a cathode, and a light emitting layer disposed between the anode and the cathode. The touch layer is arranged between the substrate and the organic light-emitting device, and the touch layer is prepared first and then the organic light-emitting device is prepared, so that the process of the touch layer is not affected by the organic light-emitting device, and the product yield is improved.

Owner:WUHAN CHINA STAR OPTOELECTRONICS SEMICON DISPLAY TECH CO LTD

Method for cleaning sapphire substrate

InactiveCN102632055AImprove product yieldWon't catchCleaning processes and apparatusChemistryNitrogen

The invention relates to a method for cleaning a sapphire substrate. The surface of a sapphire epitaxial substrate has a larger quality difference of the substrate surface and has a difference in defects of an oxidation layer and a subsurface after being cleaned by organic impurities and inorganic metal impurities due to chemical-mechanical polishing (CMP). The sapphire substrate is generally classified according to the cleaning conditions of the substrate surface. And when an imaging (PSS (Poly(sodium-p-styrenesulfonate))) substrate is prepared or heteroepitaxy is directly carried out, the product uniformity is different so that the final yield of the product is decreased. The method provided by the invention is characterized in that the sapphire substrate is cleaned with the organic impurities and the inorganic metal impurities and then is cleaned with hydrogen-nitrogen plasmas. After the cleaning method provided by the invention is carried out, the surface of the sapphire substrate has no oxidation impurities, defection layers and no subsurface defection layers. The surface quality of the substrate is good in consistency. The cleaning method provided by the invention has high yield of the PSS substrate or high crystallization quality of a GaN layer subjected to the heteroepitaxy.

Owner:CHANGZHOU TONGTAI PHOTOELECTRIC

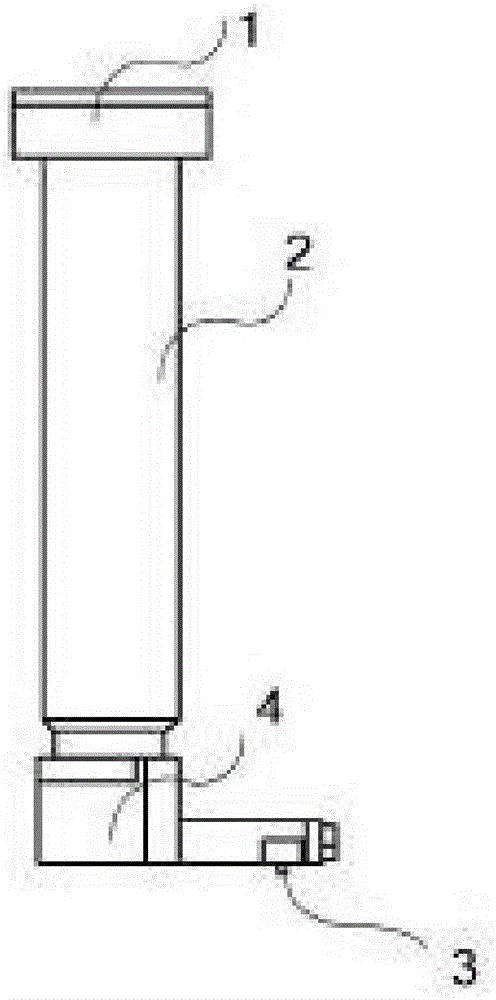

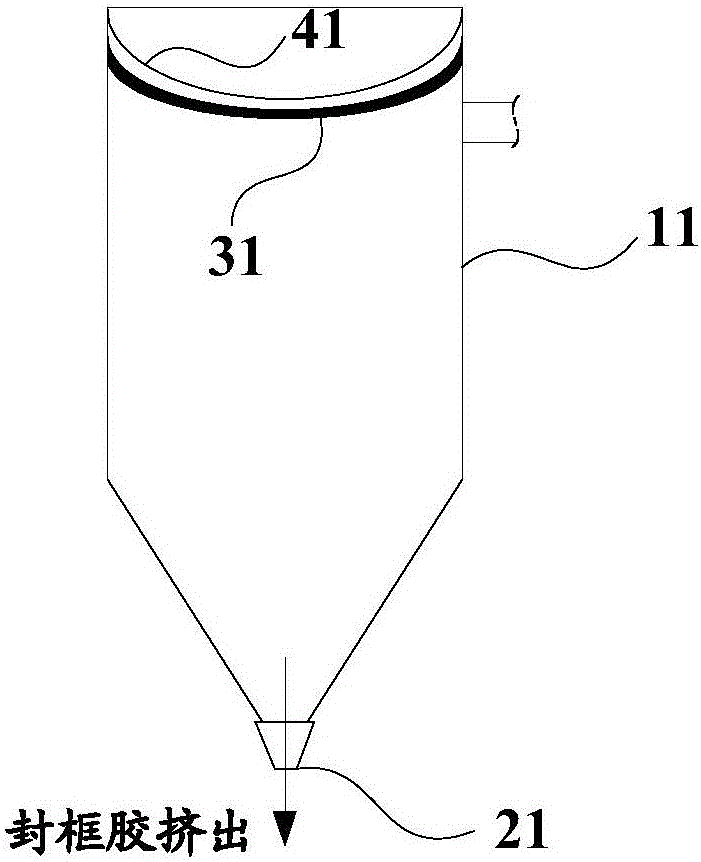

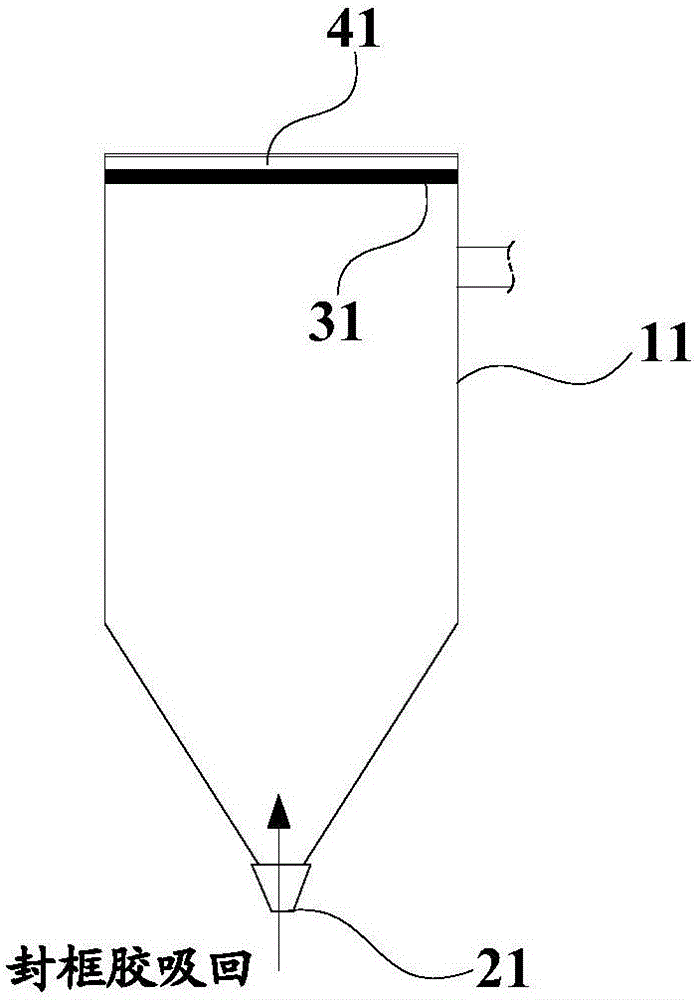

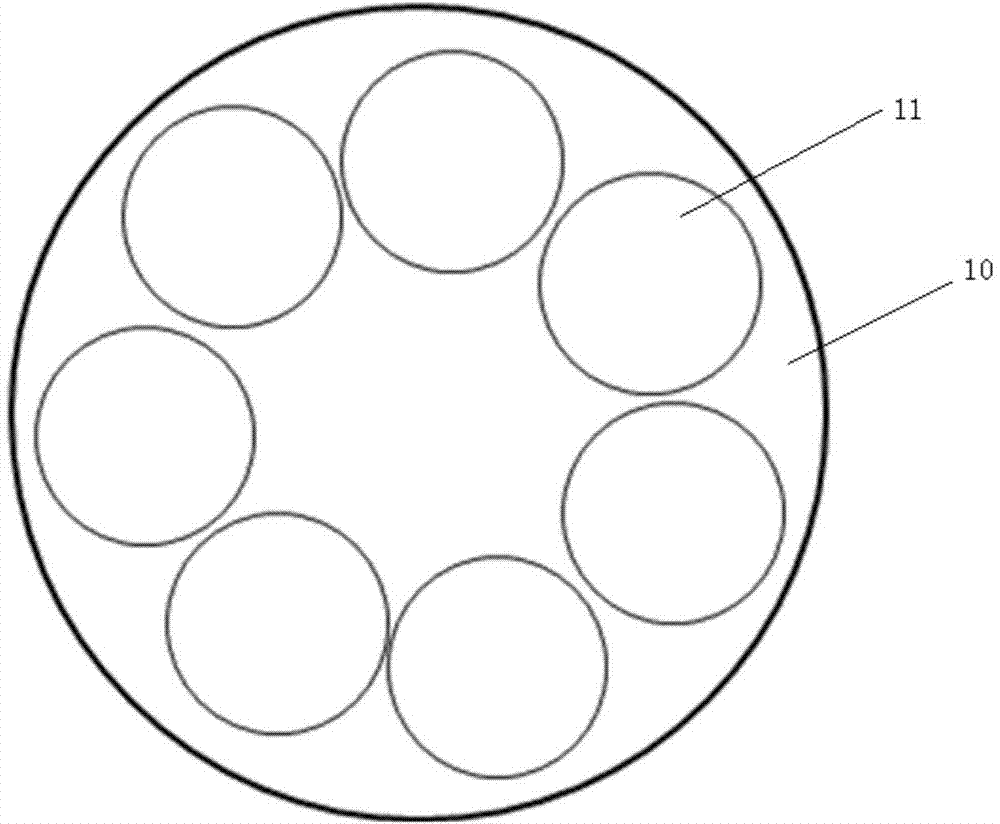

Frame-sealing-glue coating nozzle and frame-sealing-glue coating device

InactiveCN105032717AAvoid glue throwingImprove product yieldLiquid surface applicatorsSingle-unit apparatusDisplay deviceNozzle

The invention relates to the technical field of display device manufacturing, discloses a frame-sealing-glue coating nozzle and a frame-sealing-glue coating device and aims at avoiding the glue spinning phenomenon in the frame-sealing-glue application process and improving the good product rate of products. The frame-sealing-glue coating nozzle comprises a nozzle cavity, a nozzle opening communicated with the nozzle cavity, an extending-and-contracting inner membrane located in the nozzle cavity and a driving device which drives the extending-and-contracting inner membrane to be deformed in the nozzle cavity, when the extending-and-contracting inner membrane is in the first deformation state, the volume of the nozzle cavity is decreased, frame-sealing glue in the nozzle cavity is extruded, when the extending-and-contracting inner membrane is in the second deformation state, the volume of the nozzle cavity is increased, and the frame-sealing glue at the nozzle opening is sucked into the nozzle cavity.

Owner:BOE TECH GRP CO LTD +1

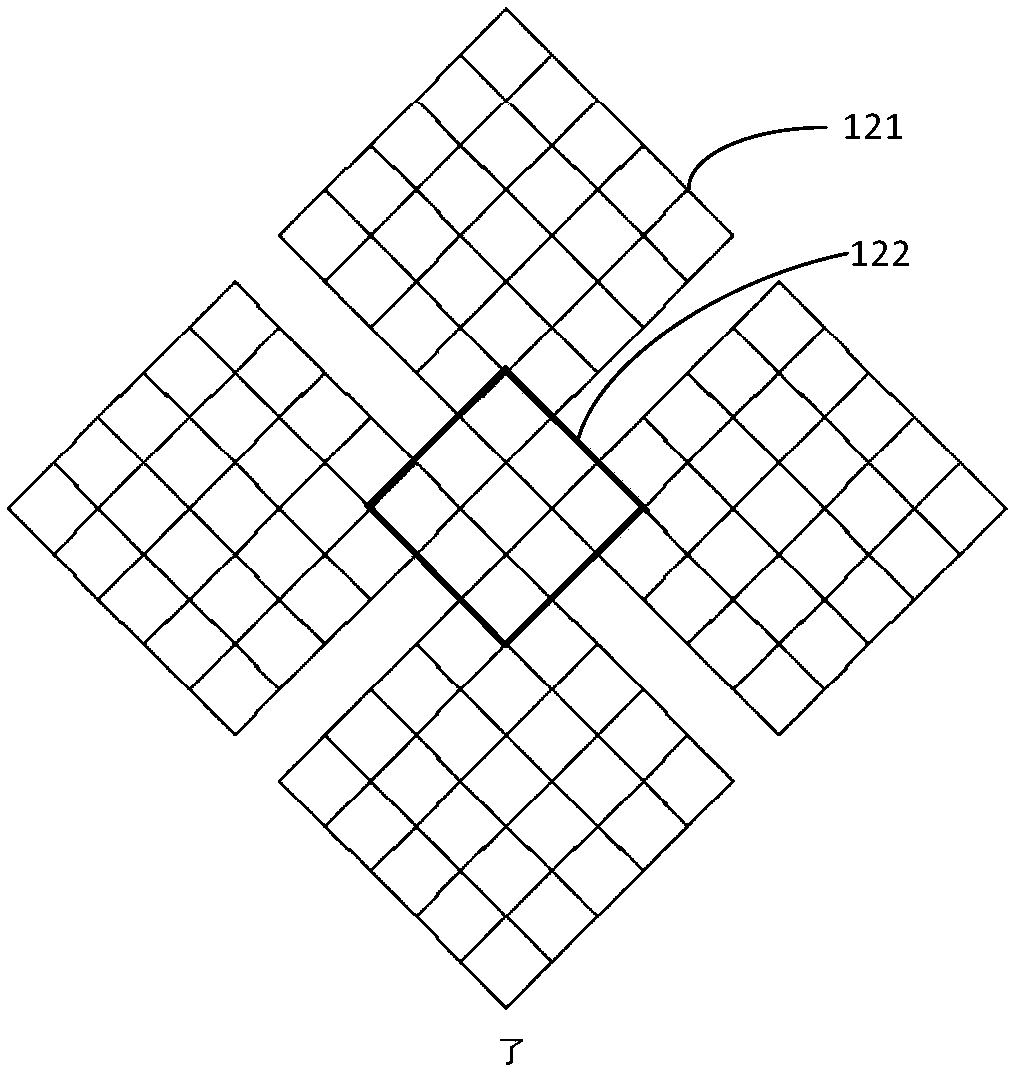

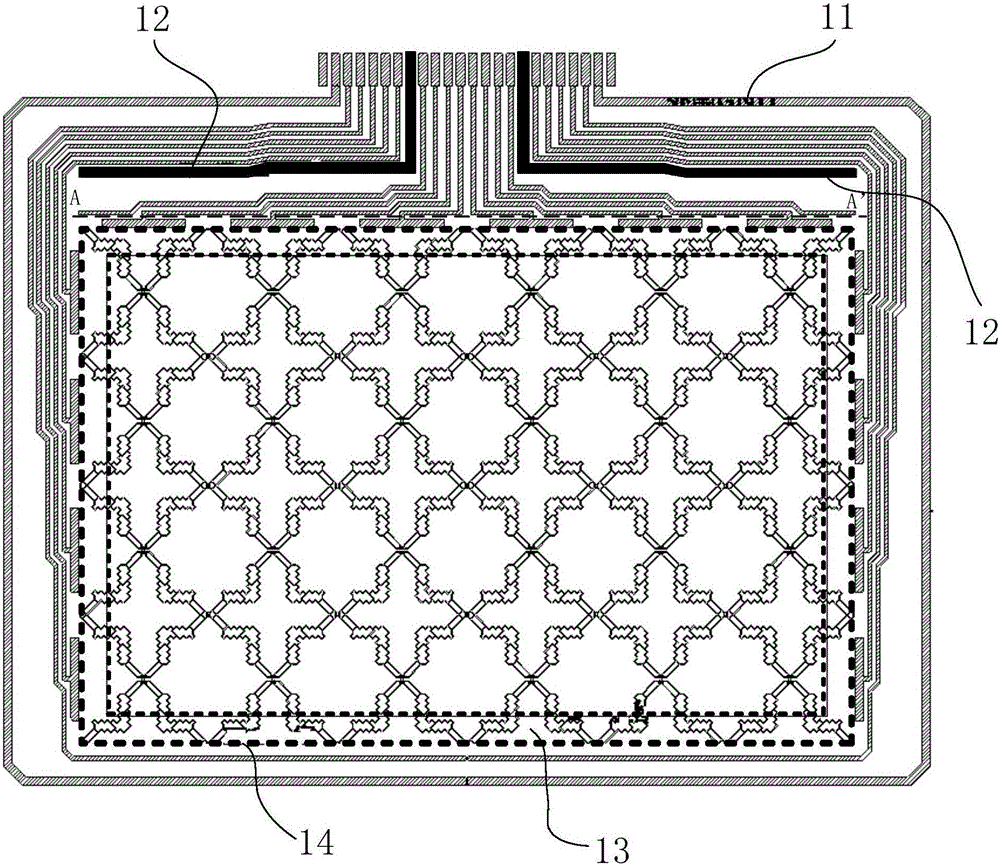

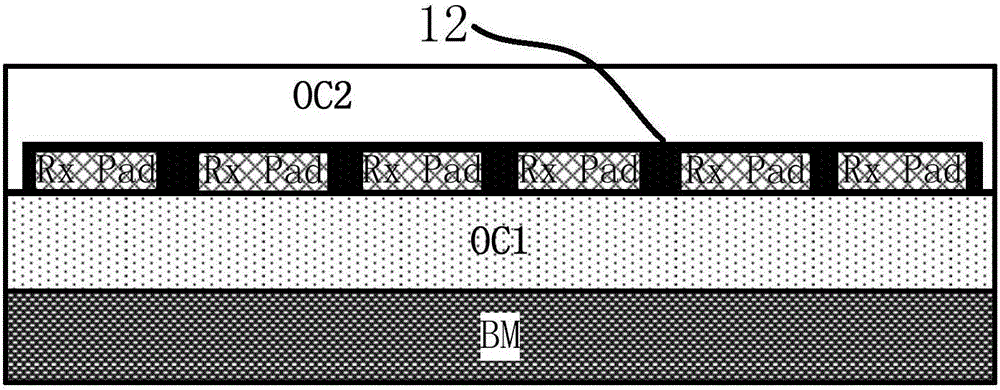

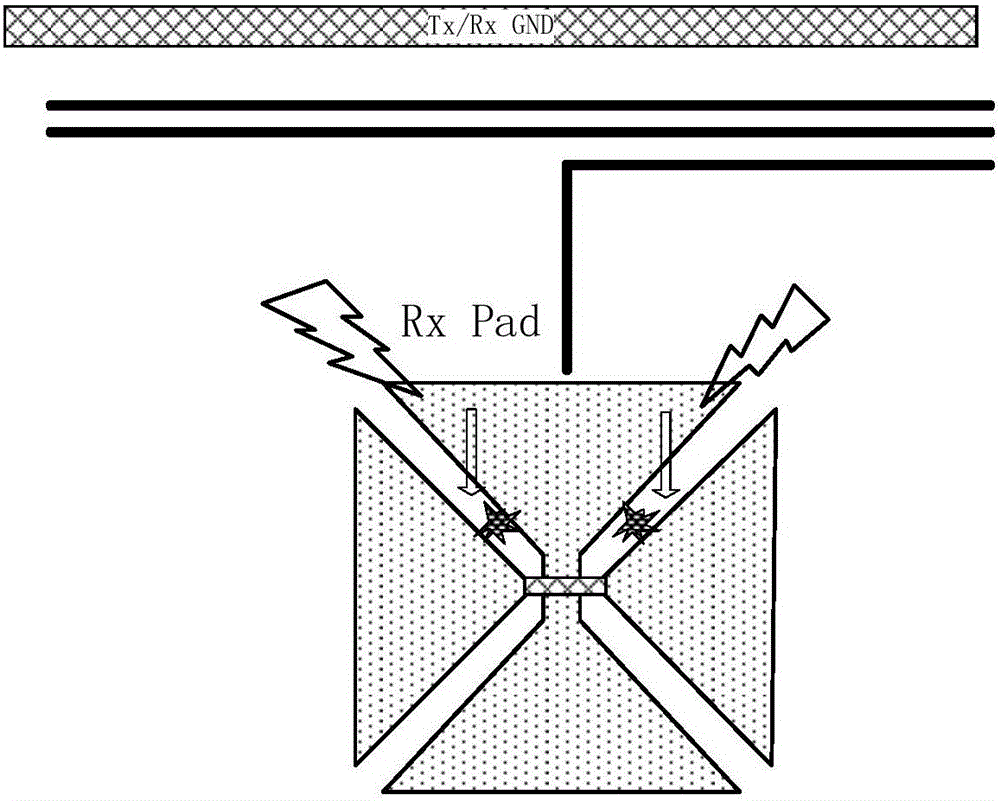

Touch panel and manufacturing method thereof, and touch display device

InactiveCN106201084AImprove ESD resistanceImprove product yieldPrinted circuit aspectsHigh voltage circuit adaptationsTouch panelDisplay device

The invention discloses a touch panel and a manufacturing method thereof, and a touch display device. The touch panel comprises a touch area and a routing area, wherein the routing area surrounds the touch area; the routing area comprises a drive electrode routing and an induction electrode routing; a first ground routing in a loop state surrounds the induction electrode routing, and has an overlapping area with the induction electrode routing; and the first ground routing can lead static electricity generated by the touch panel to the outside. Through the touch panel and the manufacturing method thereof, and the touch display device disclosed by the invention, the static electricity gathered at the edges of a black matrix and a position of an induction electrode can be led out; and thus, the effect of preventing the static electricity from breaking through the BM to cause product badness is achieved.

Owner:BOE TECH GRP CO LTD +1

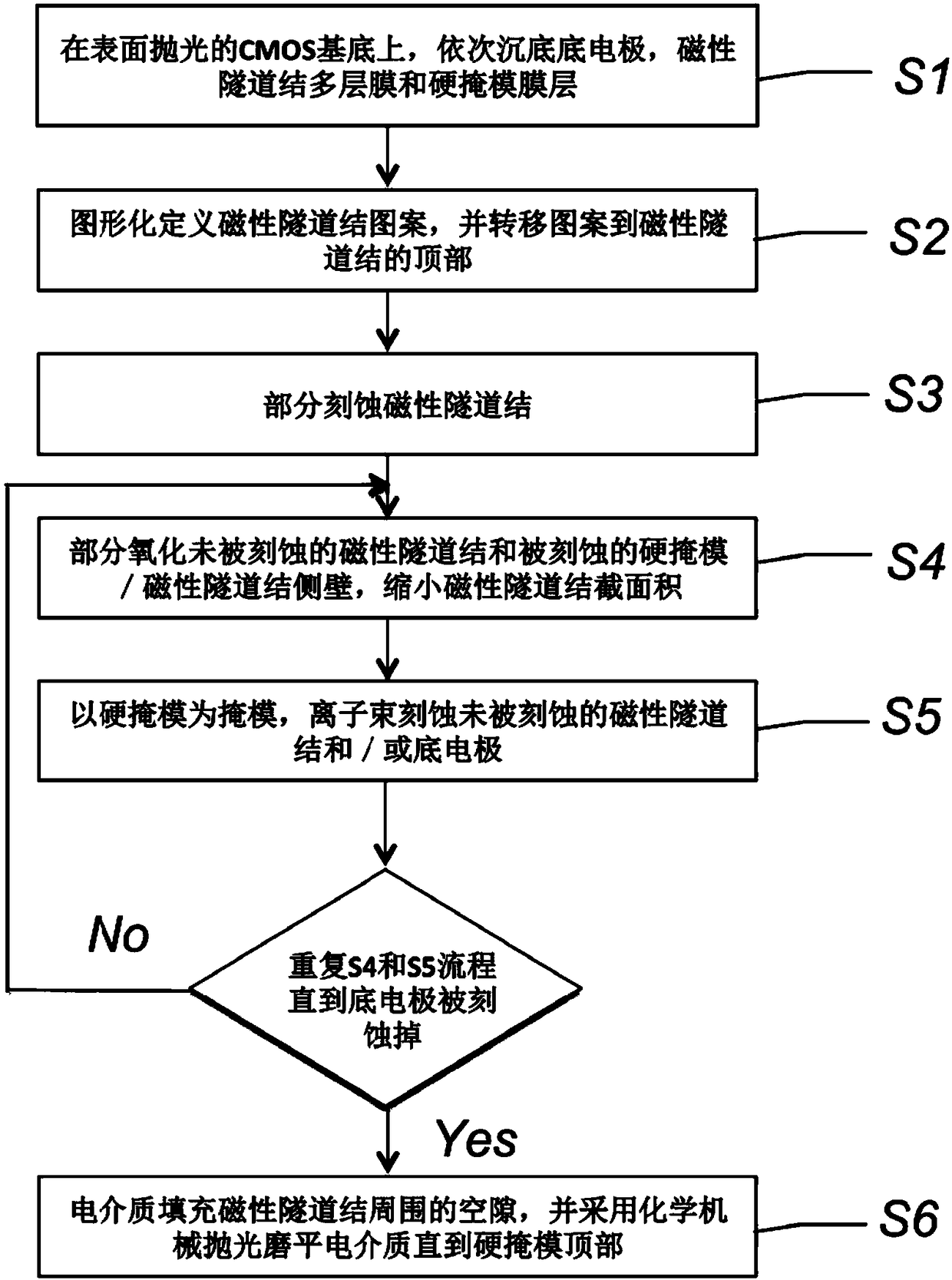

Method of manufacturing magnetic tunnel junction

ActiveCN108242502AImprove electrical performanceImprove product yieldGalvano-magnetic device manufacture/treatmentIon beam etchingStructural unit

The invention provides a method of manufacturing a magnetic tunnel junction. A multiple oxidation and ion beam etching process is adopted, formation of a short circuit passage between a memory layer and a reference layer of a magnetic random access memory (MRAM) is completely eliminated, enhancement of the magnetic properties, the electrical properties and the product yield of the MRAM loop is facilitated, and the method can be used for manufacturing a structural unit of a super small magnetic random access memory.

Owner:SHANGHAI CIYU INFORMATION TECH

High-heat-conductivity graphene membrane and preparing method thereof

ActiveCN109650892AImprove thermal conductivityImprove product yieldModifications by conduction heat transferCvd graphenePolyamide

The invention provides a high-heat-conductivity graphene membrane and a preparing method thereof. The method includes the following steps of A, sequentially coating the surface of a base material withpolyamide acid resin and a graphene oxide solution, and conducting drying to obtain a graphene oxide compound membrane; B, stripping off the graphene oxide compound membrane from the base material toobtain a continuous graphene oxide compound membrane coiled material; C, conducting thermal treatment on the continuous graphene oxide compound membrane coiled material to obtain a carbonized continuous graphene oxide compound membrane; D, conducting graphitization treatment on the carbonized continuous graphene oxide compound membrane to obtain the high-heat-conductivity graphene membrane. The polyamide acid resin and the graphene oxide solution are sequentially formed into membranes, the structure of overlapping the graphene oxide membrane and the polyamide acid membrane is formed, the highheat conductivity of graphene can be more sufficiently realized, meanwhile the thicker graphene membrane can be obtained through stripping, the special requirements in the aerospace field can be met,and meanwhile the product yield of the stripped graphene is improved.

Owner:CHONGQING YUNTIANHUA HIGH END NEW MATERIALS DEV CO LTD

Method for forming non-load-effect large size groove

ActiveCN102779780AAvoid connection failureImprove product yieldSemiconductor/solid-state device manufacturingPhysicsComposite material

The invention relates to the field of semiconductor manufacture, in particular to a method for forming a non-load-effect large size groove. Large size and small size contact hole grooves are filled in a deposition medium layer after the metal hard mask etching process, the grinding process is utilized to form a dish recessed area on the large size grooves, load effect formed in etching of the grooves with large size difference is removed, and connection efficacy lose caused by residue caused by the load effect in the large size grooves is effectively avoided. The method improves product yield, further expands an etching process window and further improves etching process performance.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

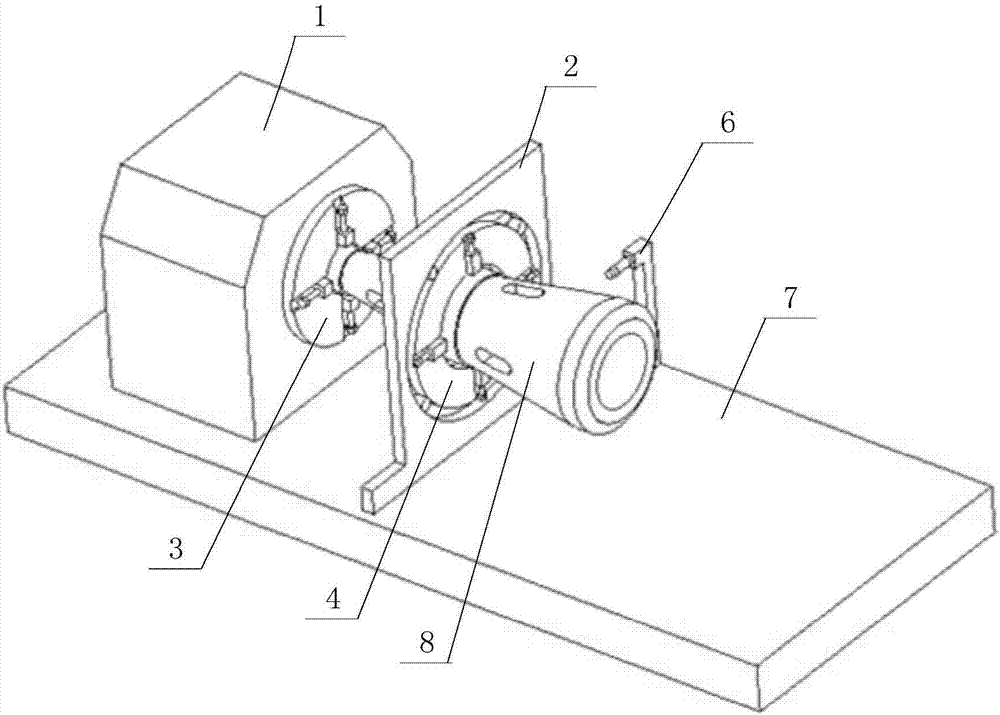

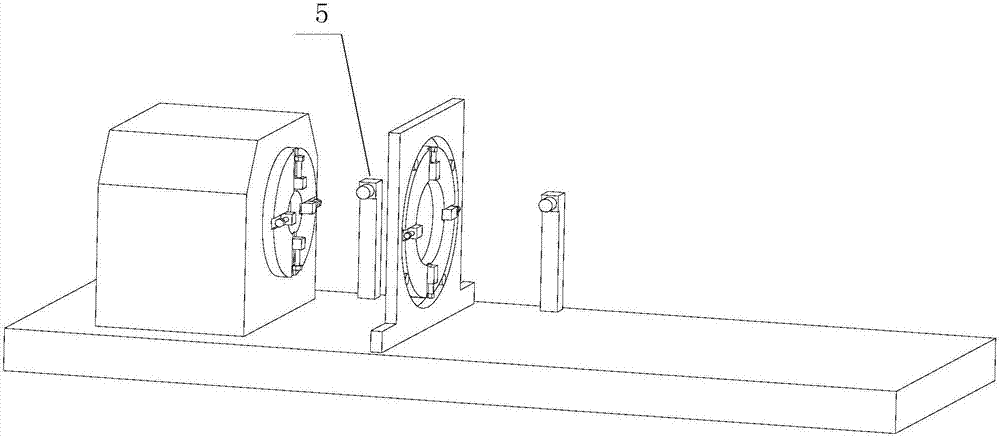

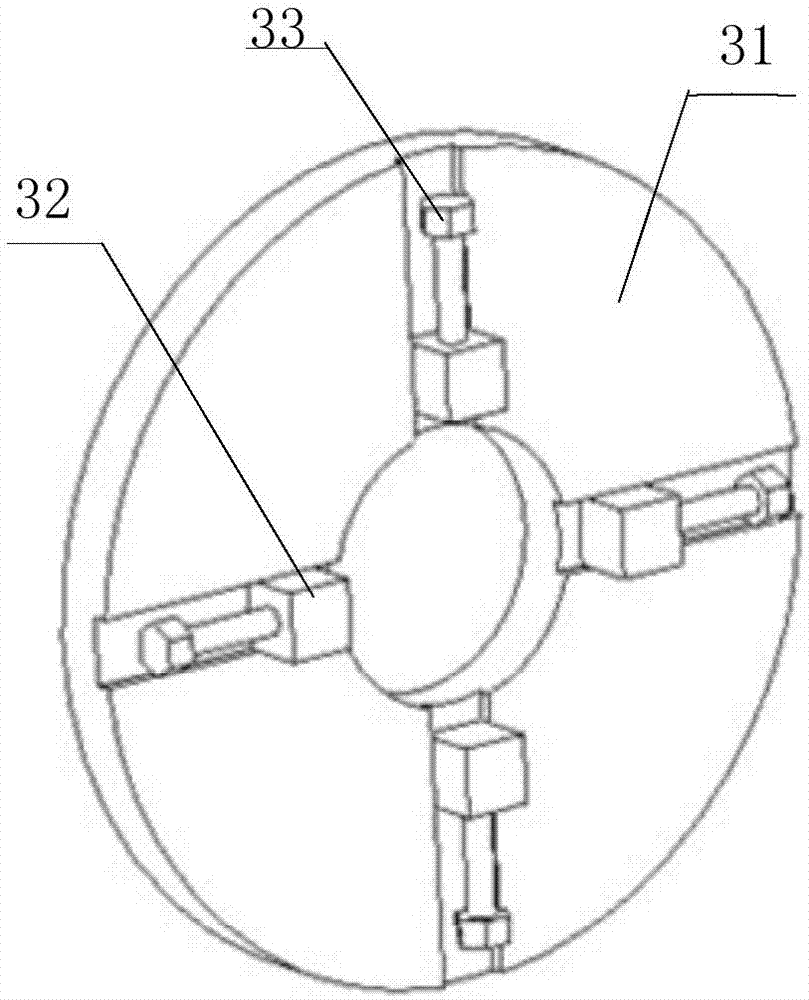

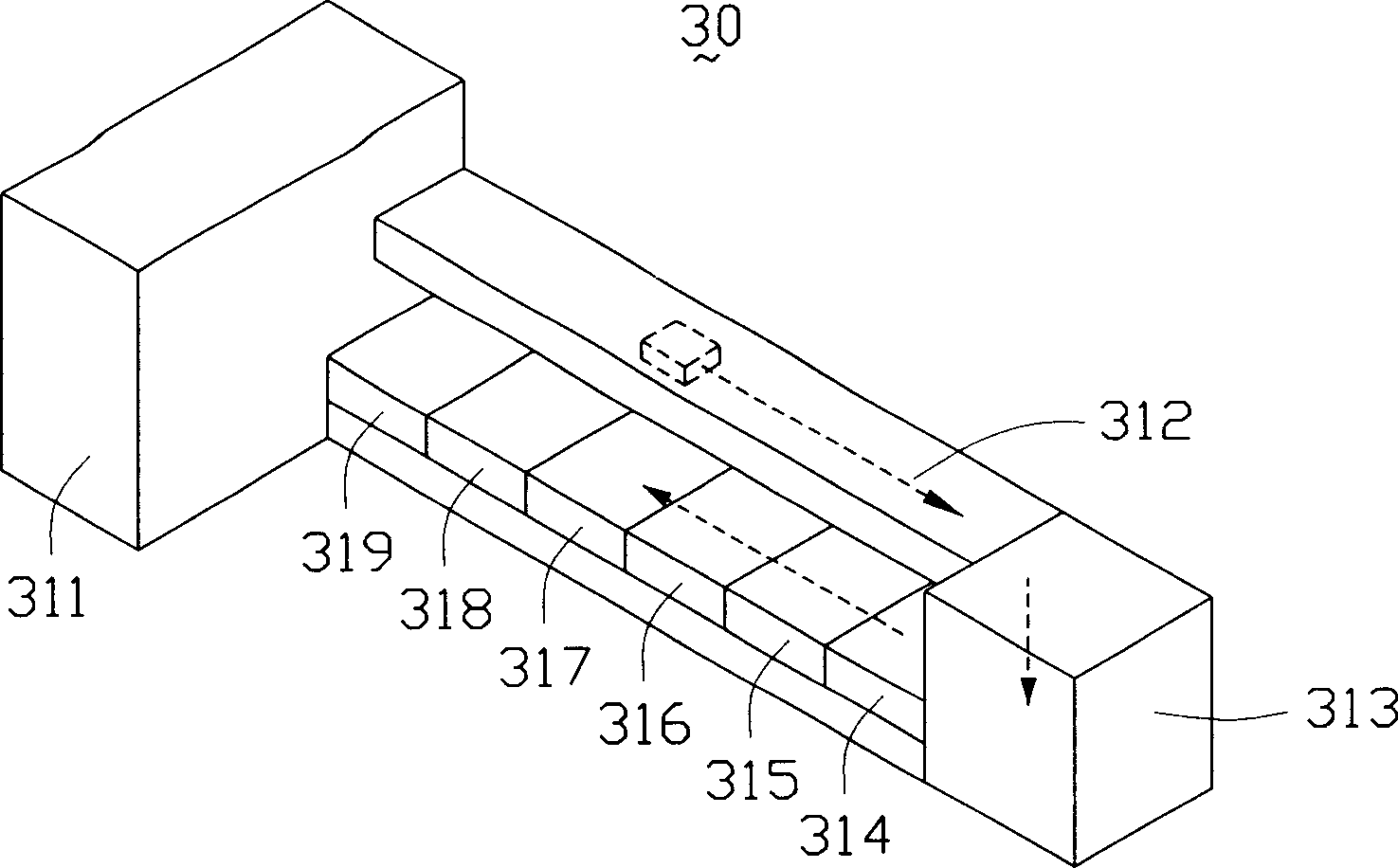

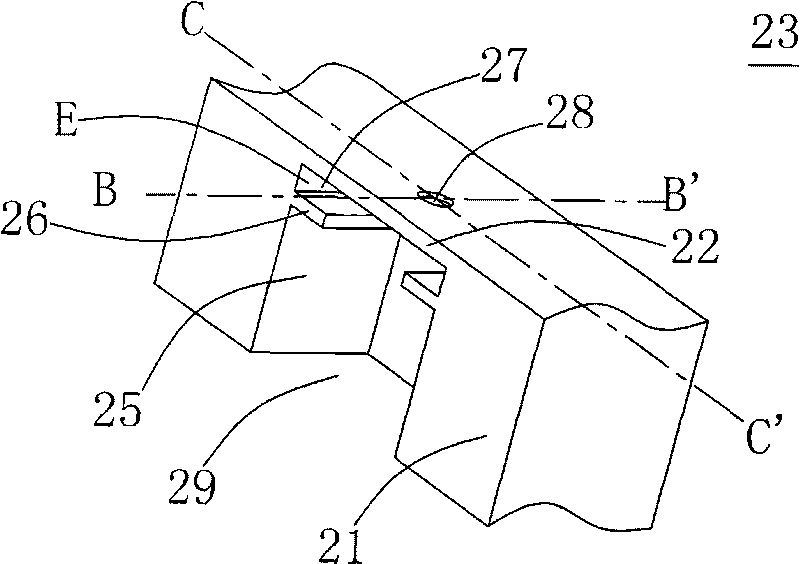

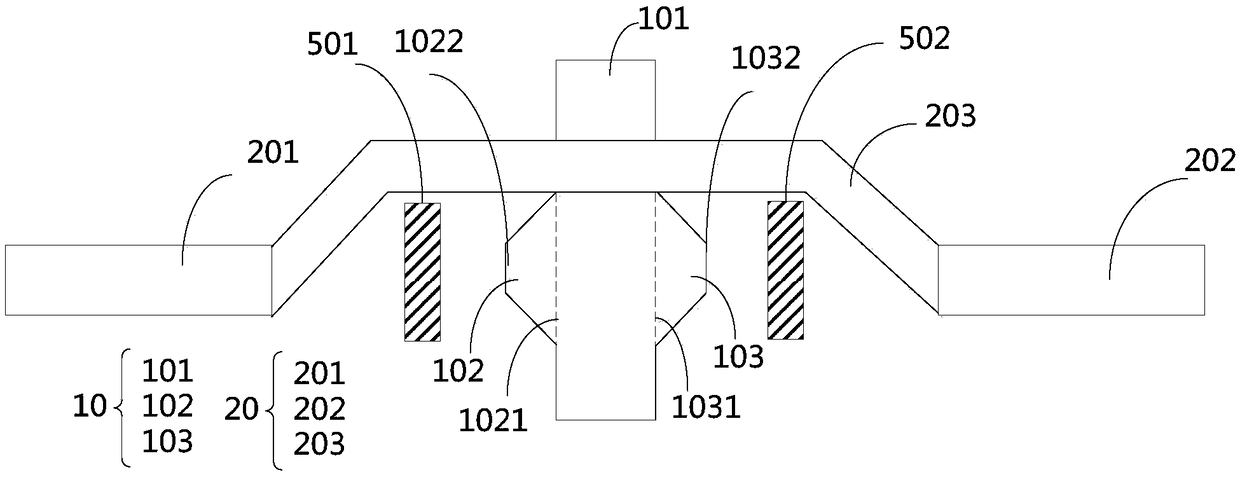

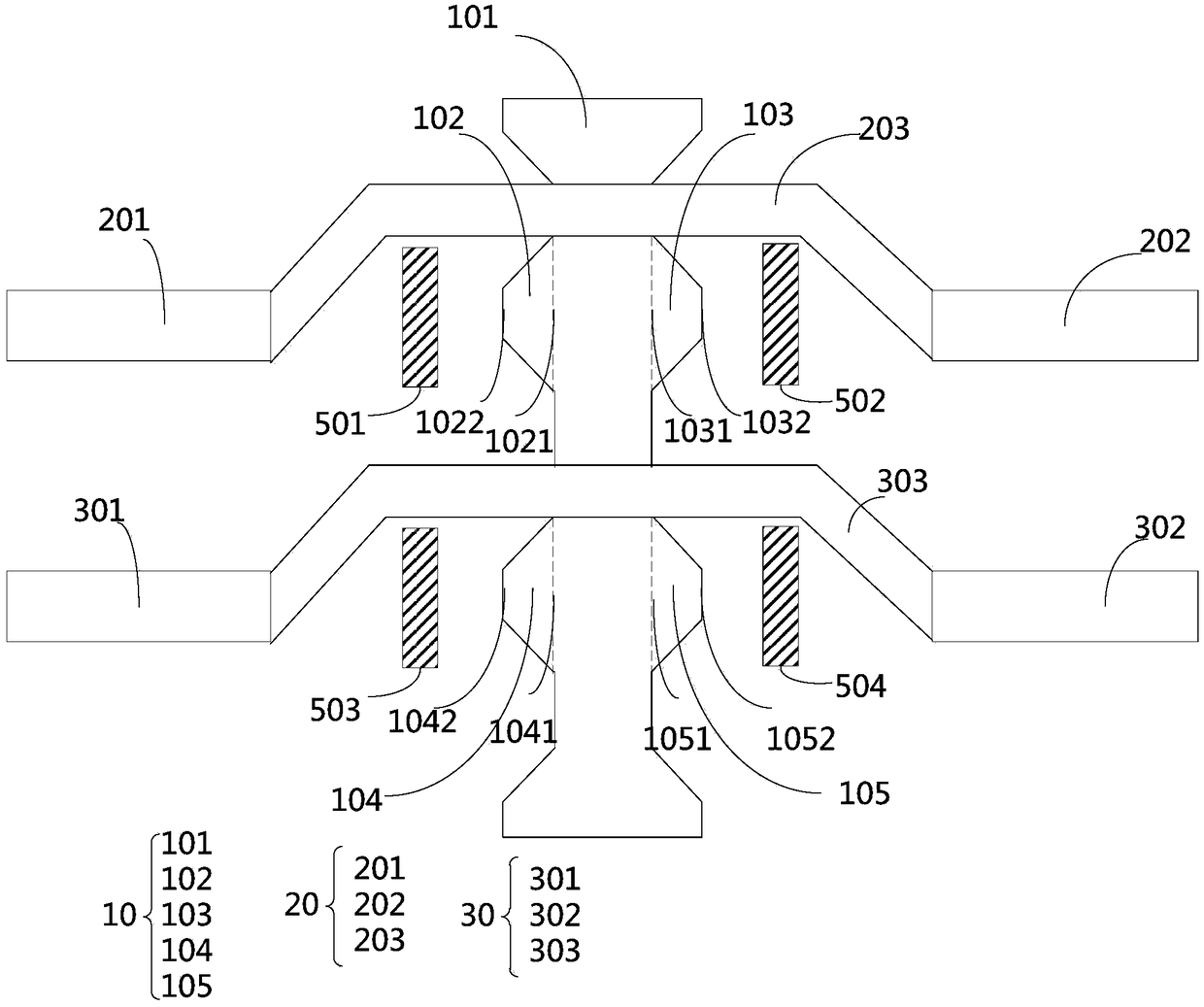

Alignment method and device for machining of inner cavity of taper workpiece

ActiveCN107470979AHigh card loading accuracyImprove product yieldAutomatic control devicesFeeding apparatusEngineeringMachine tool

The invention discloses an alignment method and device for machining of an inner cavity of a taper workpiece. The device comprises a machine tool cabinet, a center frame, a first chuck, a second chuck, a first distance detecting device, a second distance detecting device and a machine tool body, wherein the machine tool cabinet, the first distance detecting device, the center frame and the second distance detecting device are sequentially arranged on the machine tool body; the first chuck is connected with the machine tool cabinet and can rotate around the center of the first chuck; the second chuck is connected with the center frame and can rotate around the center of the second chuck; and one end of the taper workpiece is embedded in the first chuck, and the other end of the taper workpiece is embedded in the second chuck. By means of the alignment method and device, the taper workpiece can be automatically aligned after being clamped to a machine tool, the precision requirement is met, and the problem that secondary clamping restrains workpiece coaxiality and consequently the precision requirement is not met is solved.

Owner:AEROSPACE RES INST OF MATERIAL & PROCESSING TECH +1

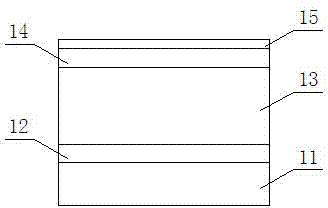

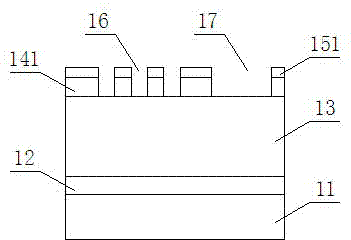

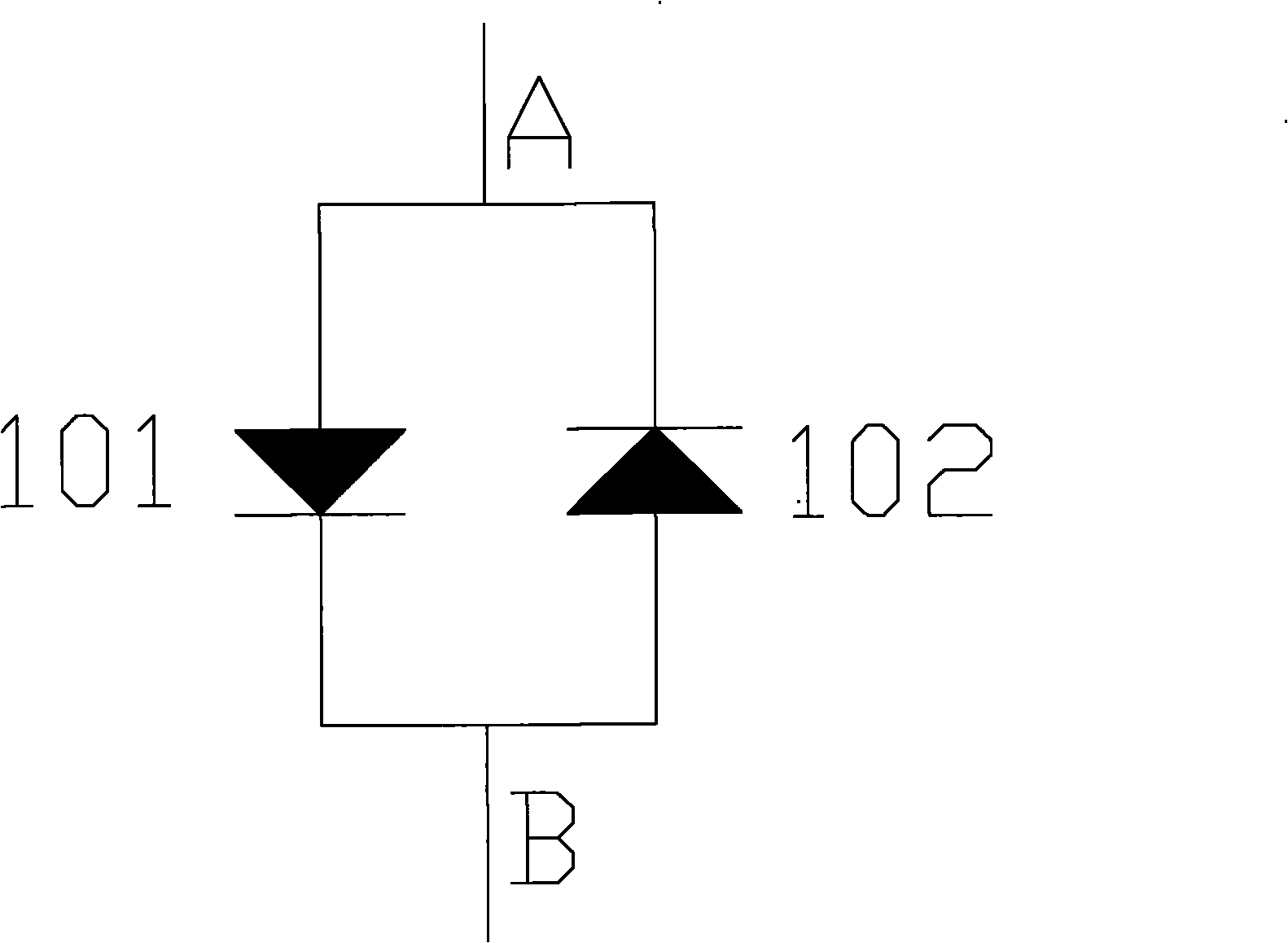

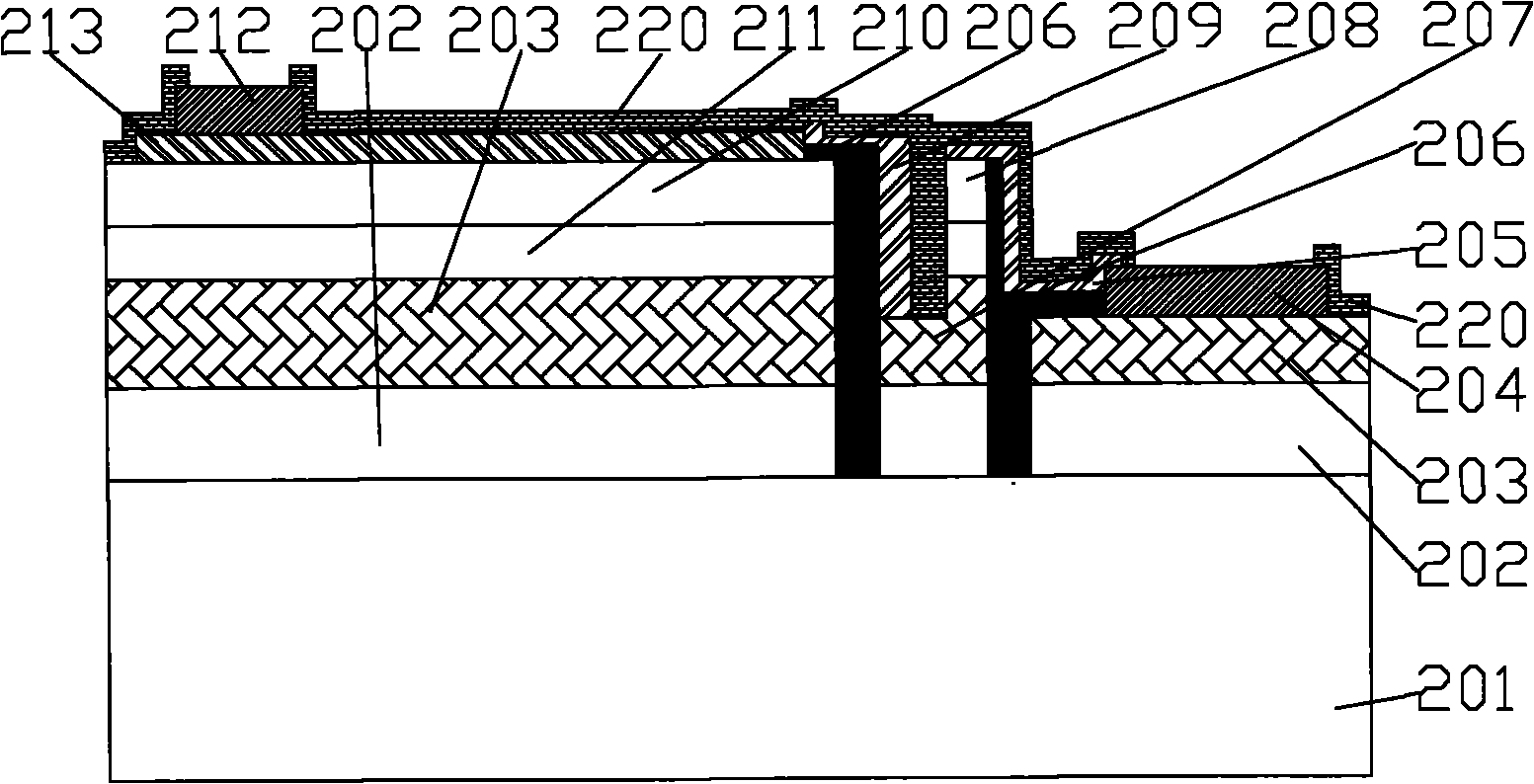

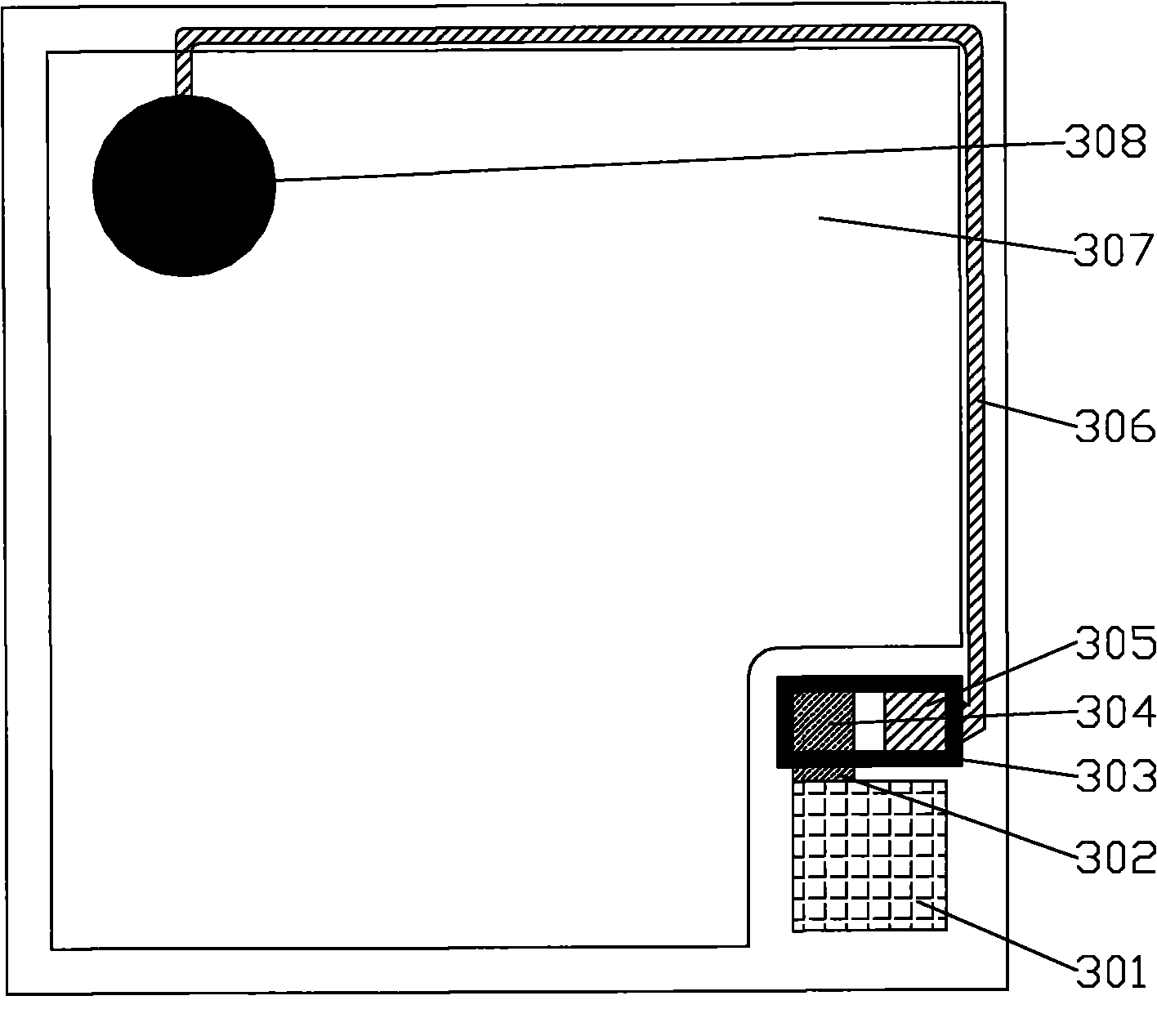

Antistatic gallium nitride based luminescent device and manufacturing method thereof

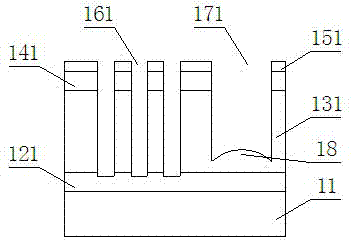

InactiveCN101916769ASimplify the production processImprove product yieldSolid-state devicesSemiconductor/solid-state device manufacturingMultiple quantumGallium nitride

The invention discloses an antistatic light-emitting diode device structure and a manufacturing method thereof. The method comprises the following steps: growing a buffer layer, an N-shaped gallium nitride layer, a luminescent layer multiple quantum well (MQW) structure and a P-shaped gallium nitride layer on a sapphire substrate in sequence; etching an epitaxial layer between a light-emitting diode and a protection diode on the substrate; manufacturing the P electrode and the N electrode of the light-emitting diode; respectively connecting the P electrode and N electrode of the light-emitting diode with the N electrode and P electrode of the protection diode; and integrating the protection diode and the light-emitting diode in a light-emitting diode device on the basis of not changing the existing gallium nitride base epitaxial structure, thus improving antistatic capacity of products, reducing parallel protected diodes in packaging subsequent products, reducing working procedures, and lowering product cost.

Owner:HC SEMITEK CORP

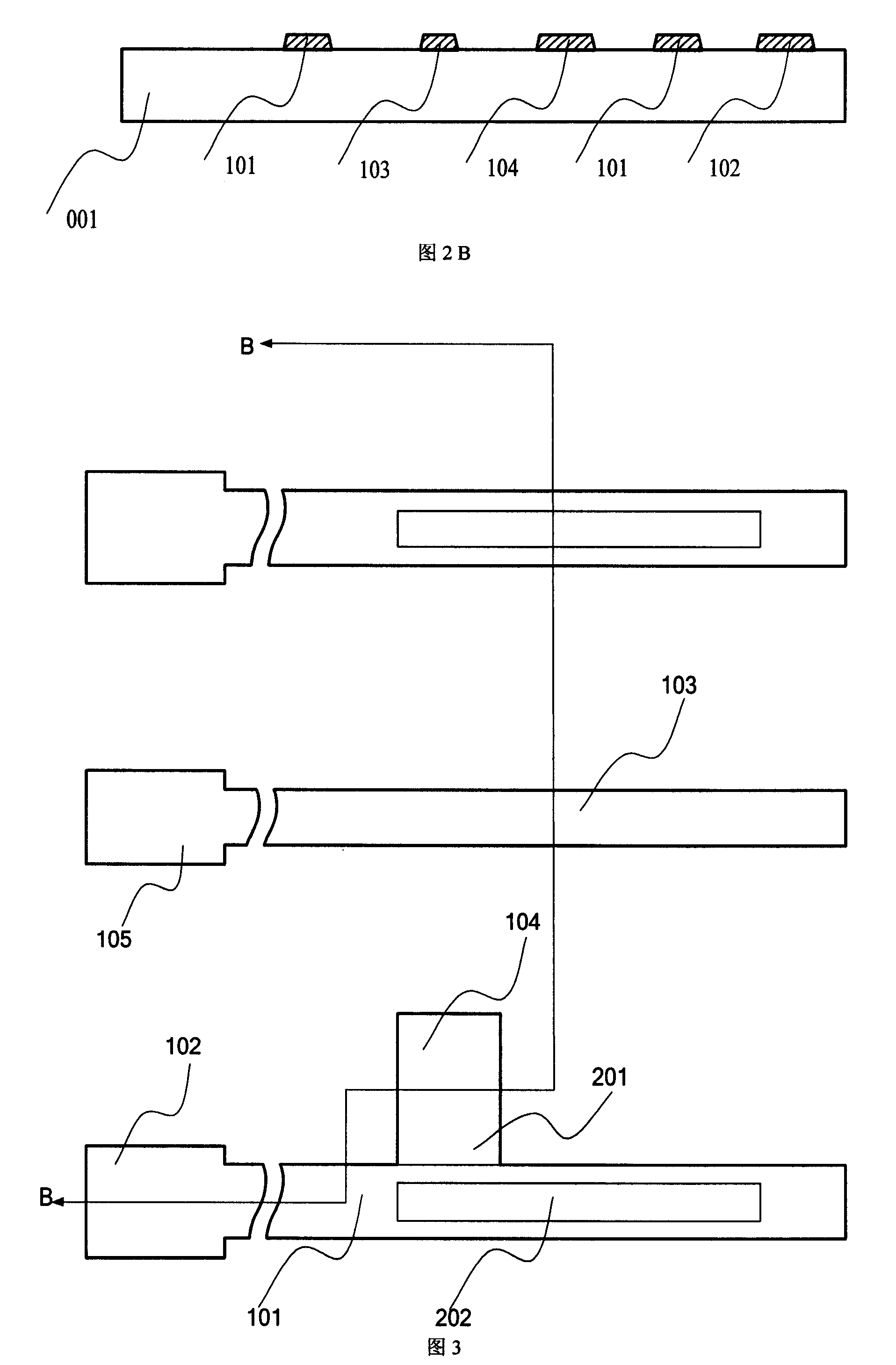

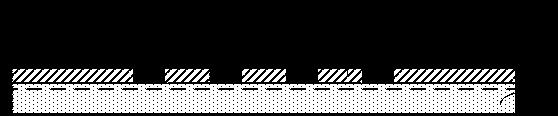

Thin film transistor array base plate and its making method

InactiveCN101236953ALower impedanceReduce signal delaySemiconductor/solid-state device detailsSolid-state devicesInsulation layerEngineering

The invention discloses a thin film transistor array substrate and a method for manufacturing the same. The thin film transistor array substrate is provided with a scanning wiring conductive layer, an insulation layer, a data conductive layer, a passivation insulation layer and a transparent conducive layer in sequence. The scanning wiring conductive layer is provided with a scanning wiring and a common electrode line; the insulation layer comprises a gate insulating film; the scanning wiring is at least partially exposed and is in direct electric contact with the data conductive layer above; the array substrate of the structure can reduce signal delay of the scanning wiring and can also realize self-repair when the scanning wire breaks without a special repairing line being arranged.

Owner:NANJING CEC PANDA LCD TECH

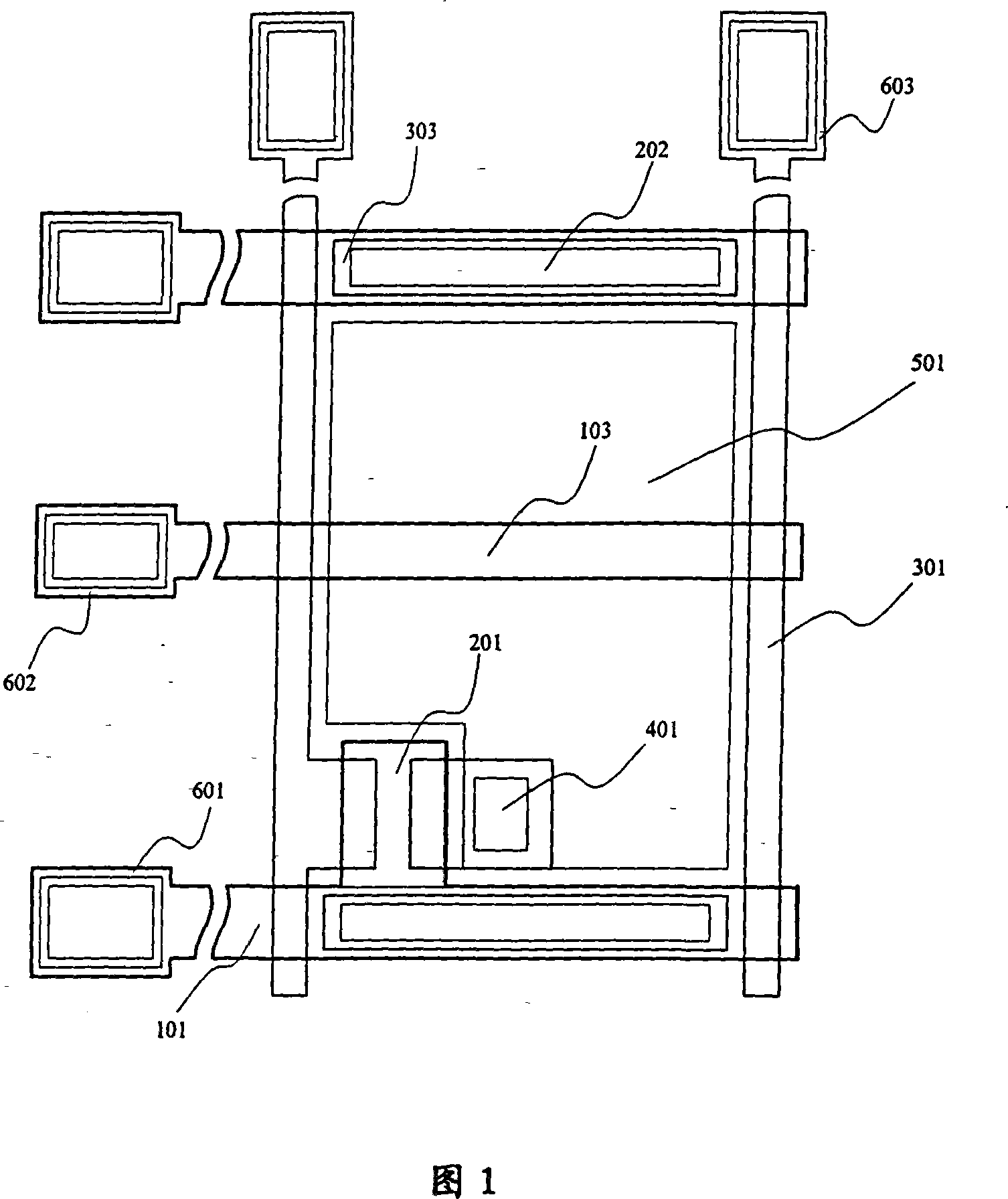

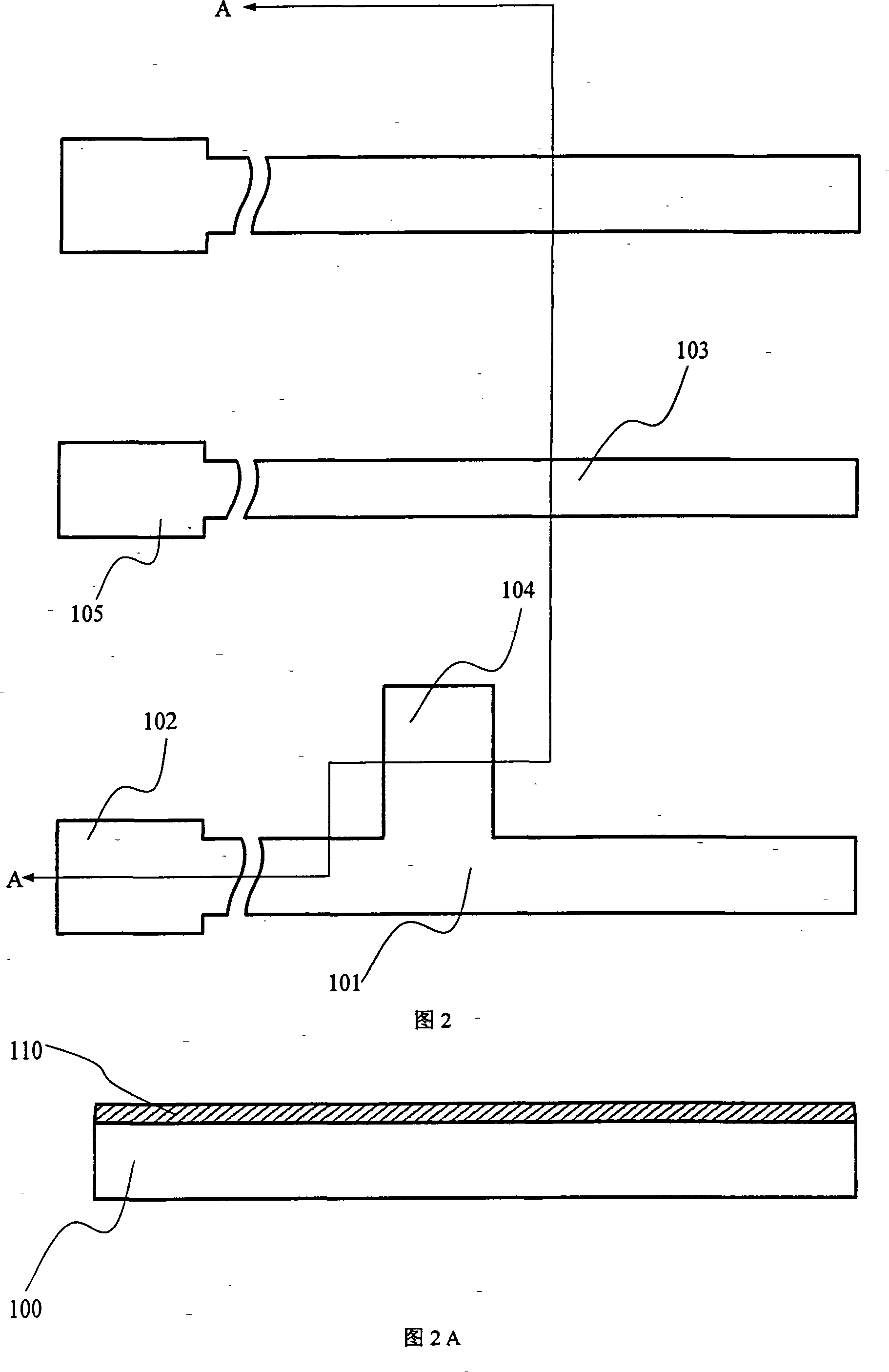

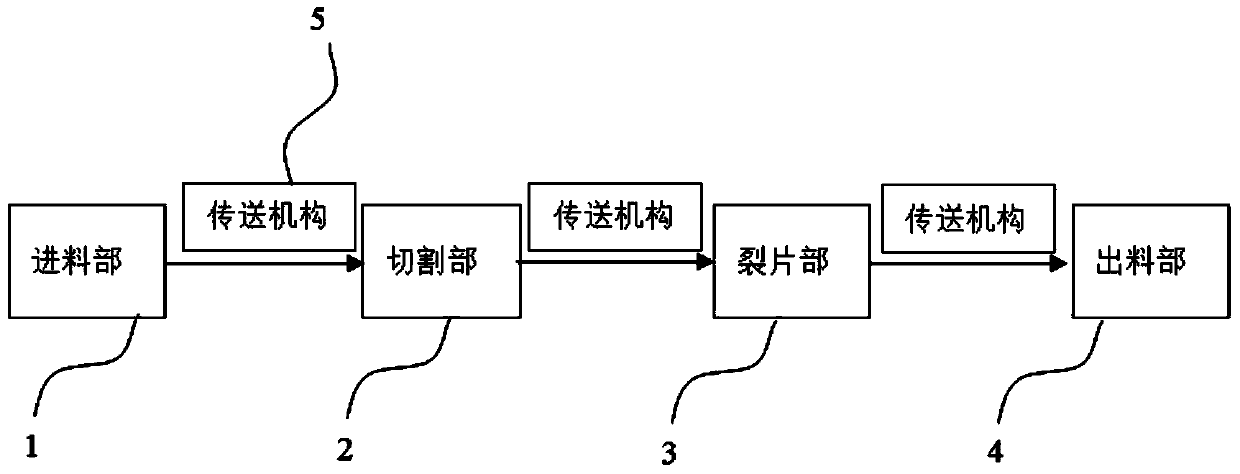

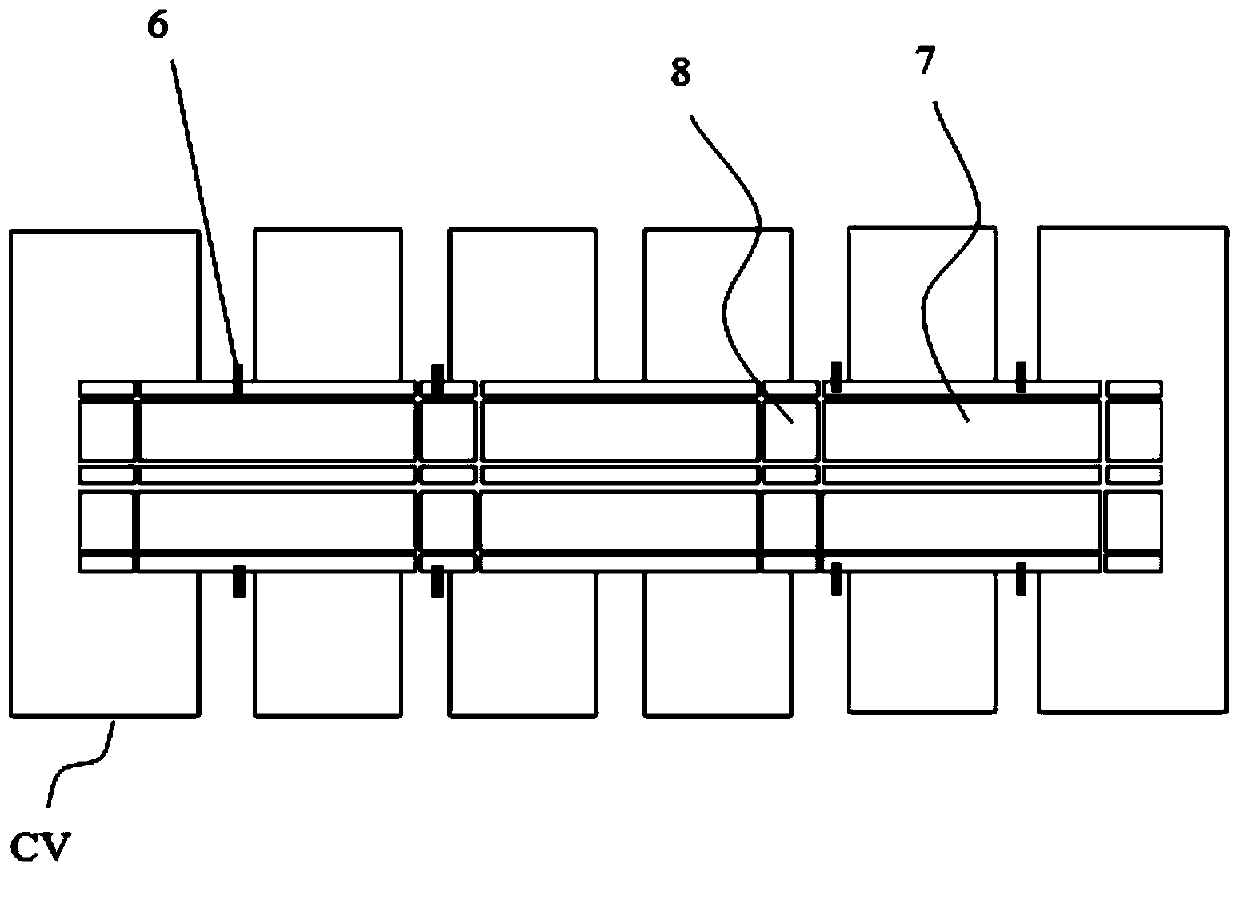

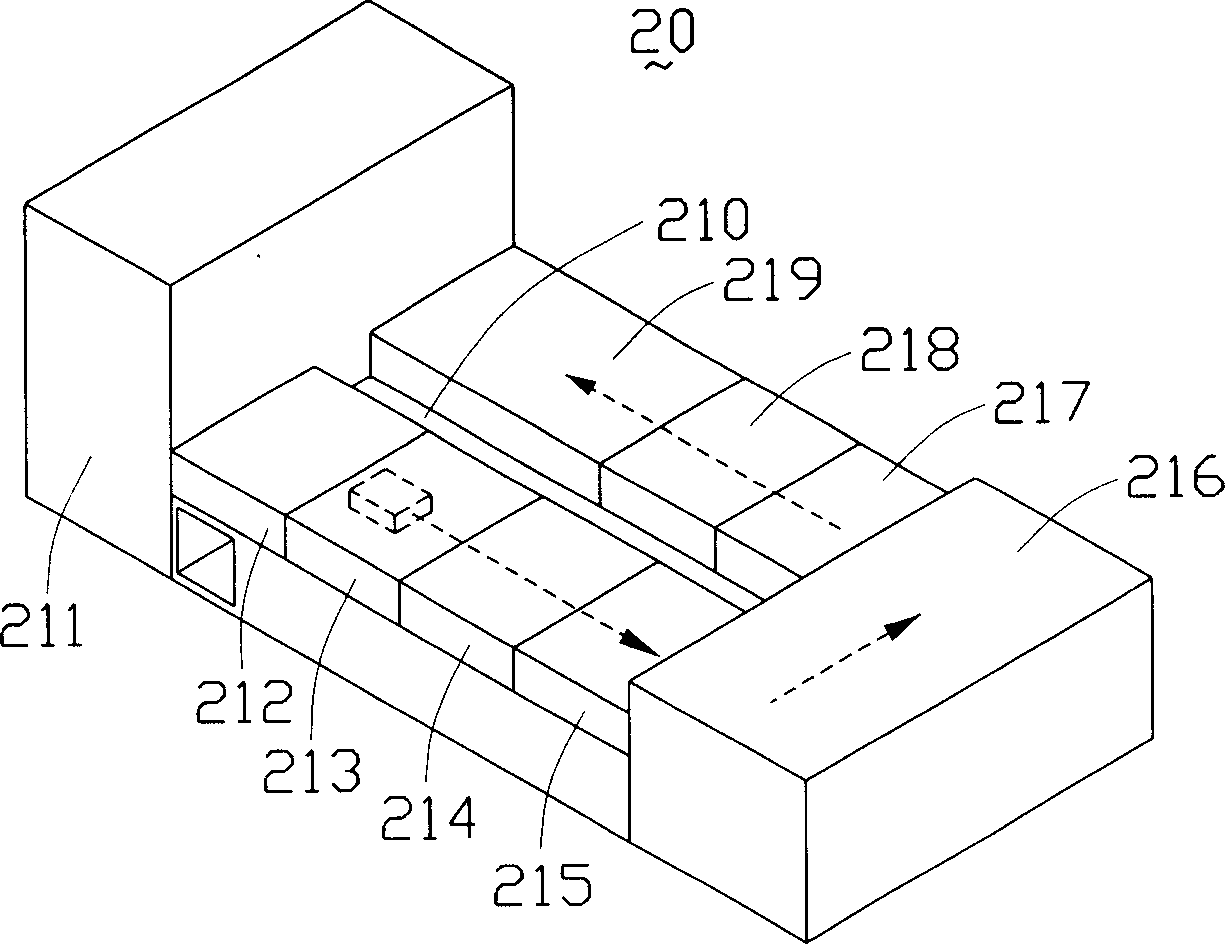

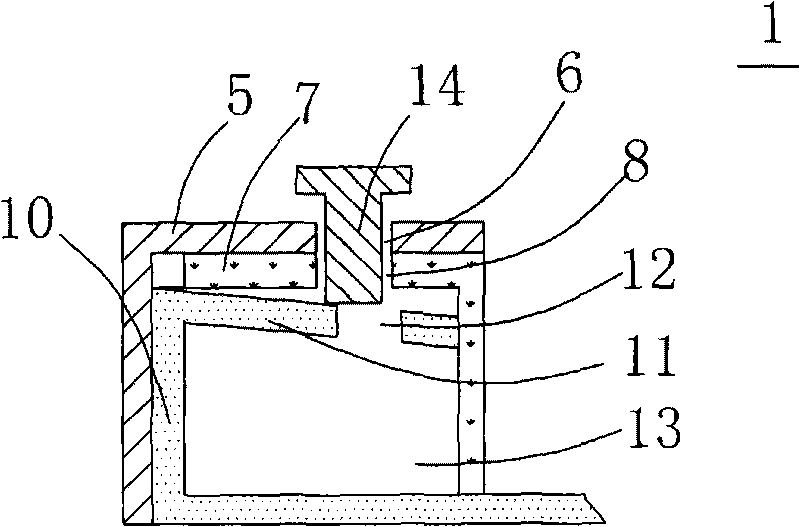

Liquid crystal panel cutter and fixing device

ActiveCN103466929AImprove product yieldLow costConveyorsSemiconductor/solid-state device manufacturingRelative displacementLiquid crystal

The invention discloses a liquid crystal panel cutter which comprises a cutting part, a shredding part and conveying mechanisms for conveying a liquid crystal panel, wherein the conveying mechanisms comprise complete integral belts and fixing devices; the complete integral belts are used for bearing and conveying the liquid crystal panel; and the fixing devices are used for fixing the liquid crystal panel and preventing the liquid crystal panel from rock in a cutting technology and a shredding technology. The invention further provides a fixing device for fixing the liquid crystal panel in the liquid crystal panel cutter. The device is used for fixing the liquid crystal panel from above the liquid crystal panel in an adhesion or adsorption connecting manner. The liquid crystal panel cutter effectively prevents panel effective zones and residue zones from relative displacement, solves the problem of collision between the panel effective zones and the residue zones on the conveying mechanisms, increases a product yield and lowers the cost.

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

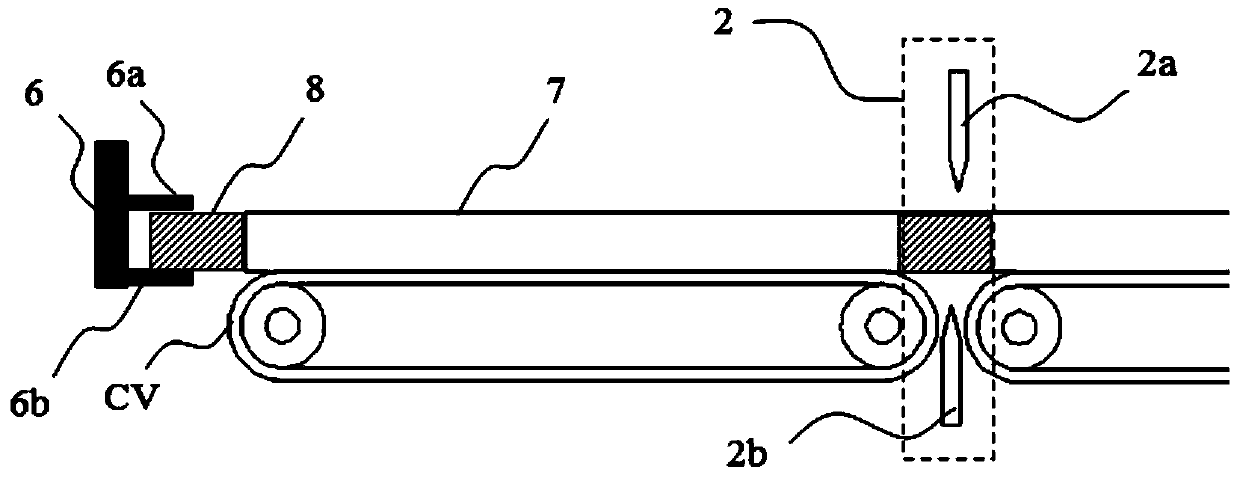

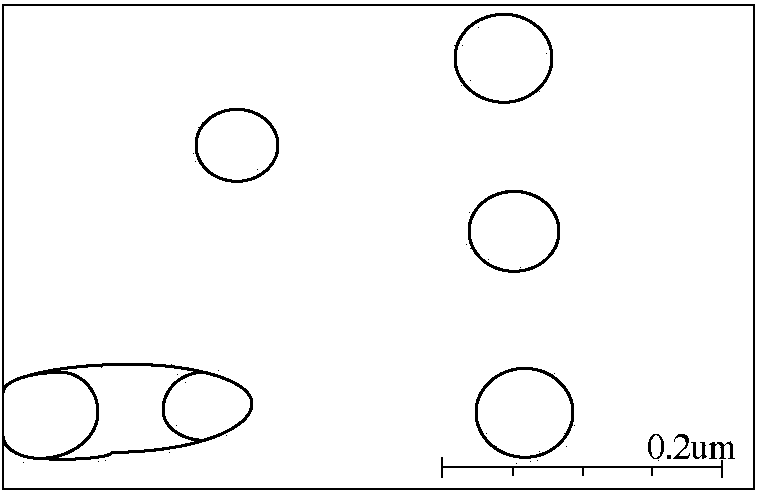

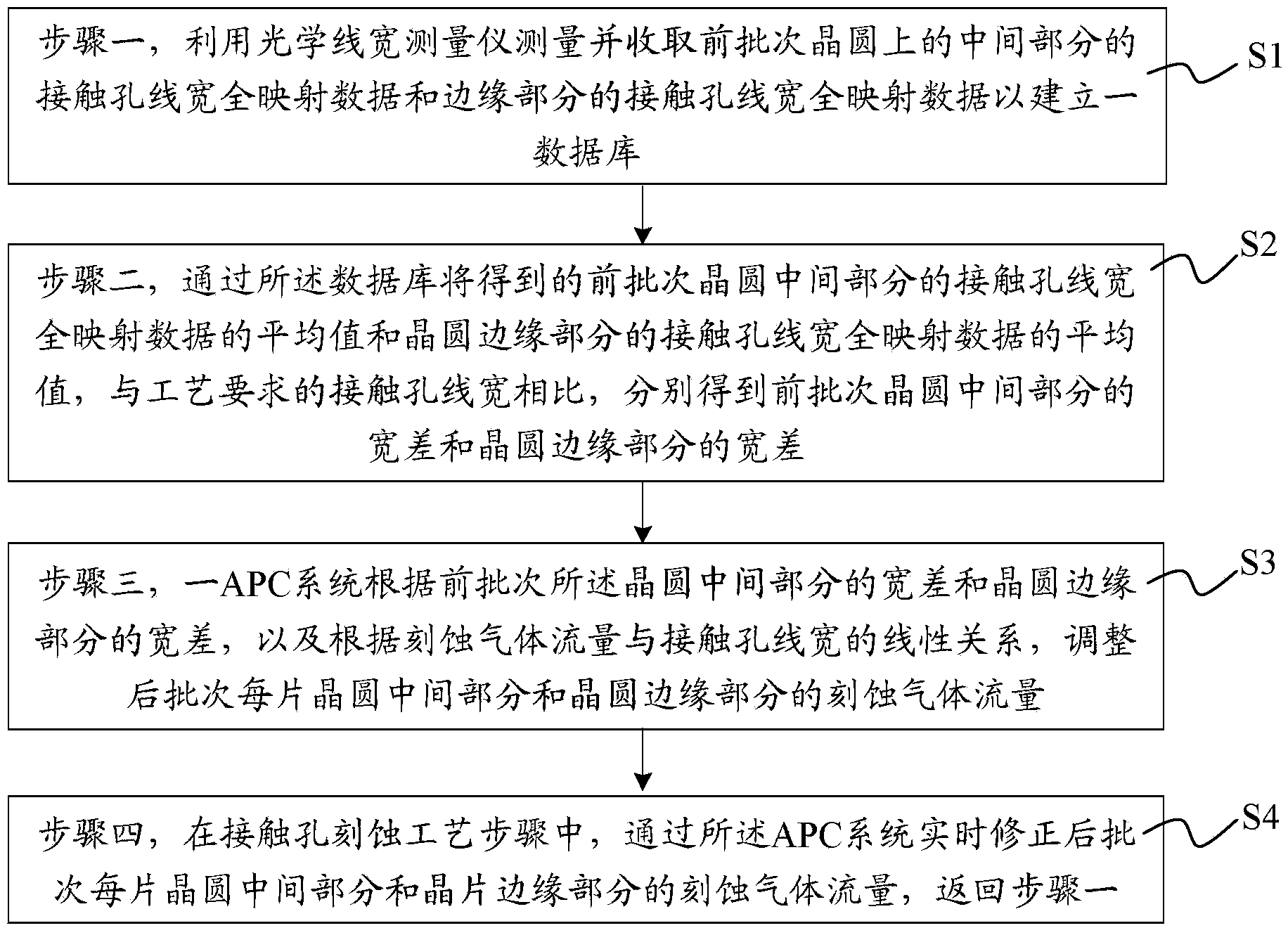

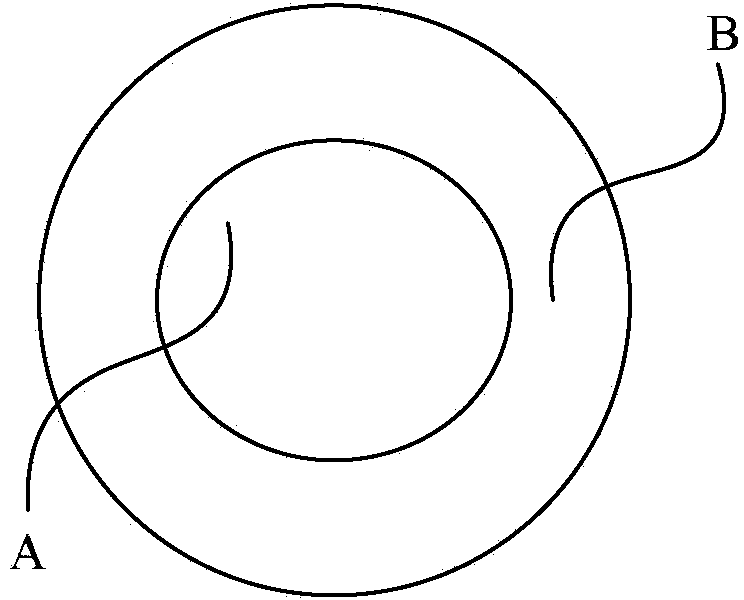

Etching method for improving uniformity of contact hole line width

ActiveCN103915378AImprove product yieldGrasp changes in gas flow demandSemiconductor/solid-state device testing/measurementSolid-state devicesPhysicsTraffic volume

The invention provides an etching method for improving the uniformity of the contact hole line width. The method comprises the steps that an optical line width measurement instrument is used for measuring and collecting contact hole line width full-mapping data on wafers of the prior batch, so that a database is established; the average value of the contact hole line width full-mapping data of the middle portions of the wafers of the prior batch and the contact hole line width full-mapping data of the edges of the wafers of the prior batch is compared with the value of the contact hole line width required by the technology through the database, so that the width difference of the middle portions of the wafers of the prior batch and the width difference of the edges of the wafers of the prior batch are obtained respectively; according to the width difference of the middle portions of the wafers of the prior batch and the width difference of the edges of the wafers of the prior batch, the etching gas flow of the middle portions of wafers of a later batch and the etching gas flow of the edges of the wafers of the later batch are respectively adjusted through an APC system; in the contact hole etching technology steps, the etching gas flow of the wafers of the later batch is corrected in real time through the APC system, so that influence, caused by the photoetching difference of the wafers of the prior batch, on photoetching of the wafers of the later batch can be avoided, the shortages that the gas flow of the middle portions and the edges of the wafers is not changed in the contact hole etching technology are overcome, and the gas flow change of each portion is accurately mastered.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

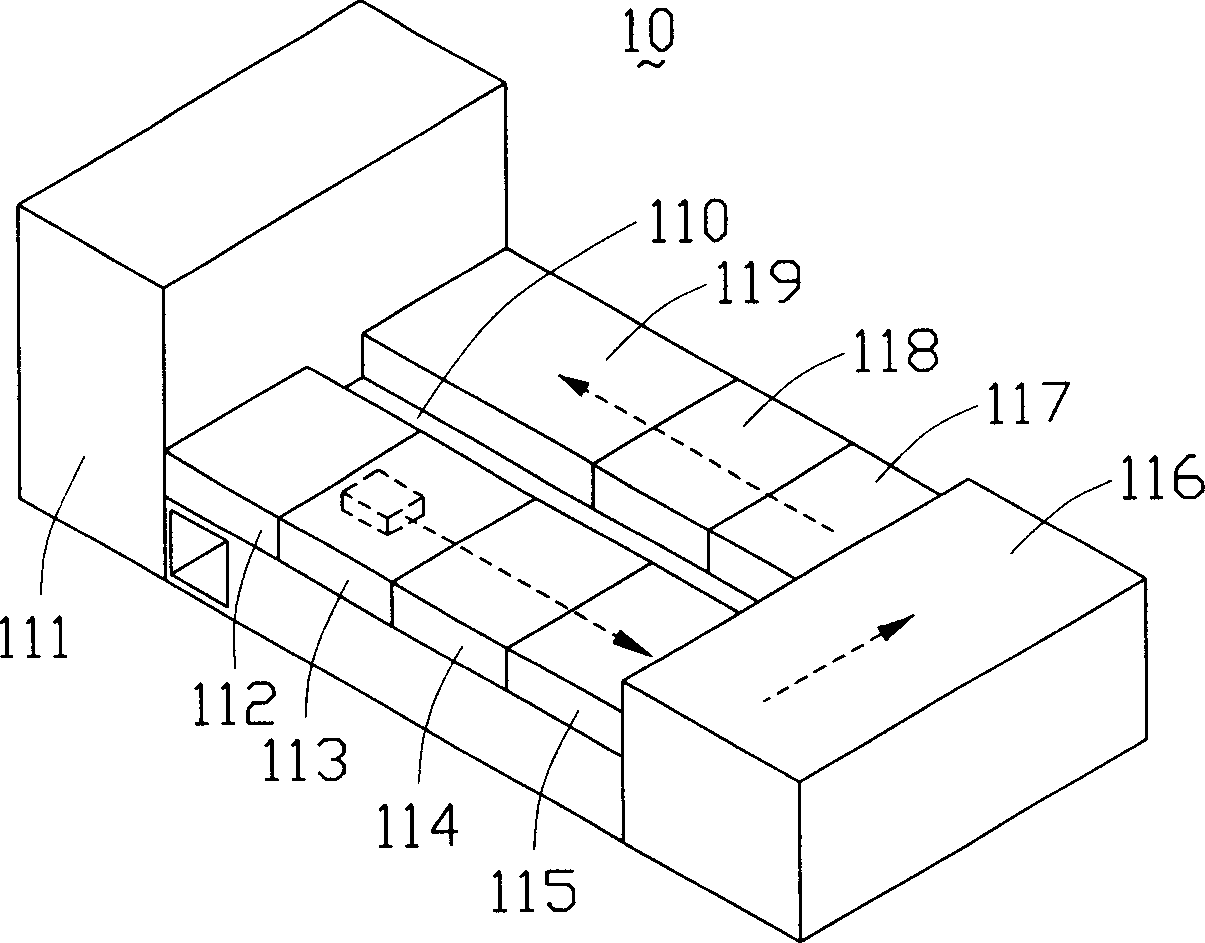

Wet etching device and wet etching method

InactiveCN1797221AGood etching qualityImprove product yieldSemiconductor/solid-state device manufacturingPhotosensitive material processingChemistryEtching

The invention provides a wet etching device, comprising in sequence: a bearing and buffering region; a first etching room using etching liquid to pre-etch and primarily etch a glass substrate; a washing room adopting high pressure water column to eliminate by-products formed on the surface of the glass substrate after the glass substrate is etched in the first etching room; a second etching room; a rising and drying transmission region.

Owner:HONG FU JIN PRECISION IND (SHENZHEN) CO LTD +1

Backlight module and display device

InactiveCN101761834AEasy to assembleImprove product yieldNon-linear opticsLight fasteningsBackplaneEngineering

The invention provides a backlight module and a display device. The backlight module comprises a back plate and a supporting seat, wherein the back plate comprises a bottom plate, a side plate and a lug, and the lug is provided with a first through hole; the supporting seat comprises a chamfer and a supporting plate; the chamfer extends to the interior of the supporting seat from the side face of the supporting plate facing the side plate; a top plate is arranged above the chamfer and provided with a second through hole corresponding to the first through hole; the supporting plate is arranged on the side wall forming the chamfer and parallel to the top plate, and the supporting plate, the top plate and the side wall form an accommodating area and an opening; and the lug is inserted in the accommodating area and combines and fixes the supporting seat and the back plate through a fixing piece, the first through hole and the second through hole. The lug of the back plate of the backlight module is arranged in the accommodating area of the supporting seat and supported by the supporting plate so that the lug is not easy to generate displacement caused by the action of external force during locking and fixing a bolt, and the locking and fixing of the lug with a lamp holder and a frame is not easy to generate a misplacement condition so as to be beneficial to assembling and improving the product yield.

Owner:AU OPTRONICS (SUZHOU) CORP LTD +1

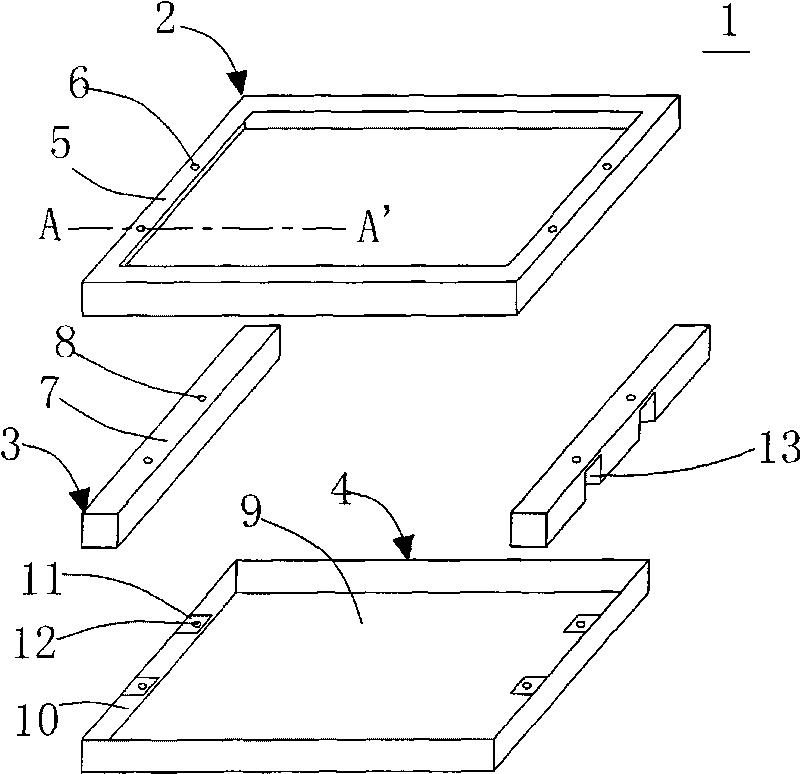

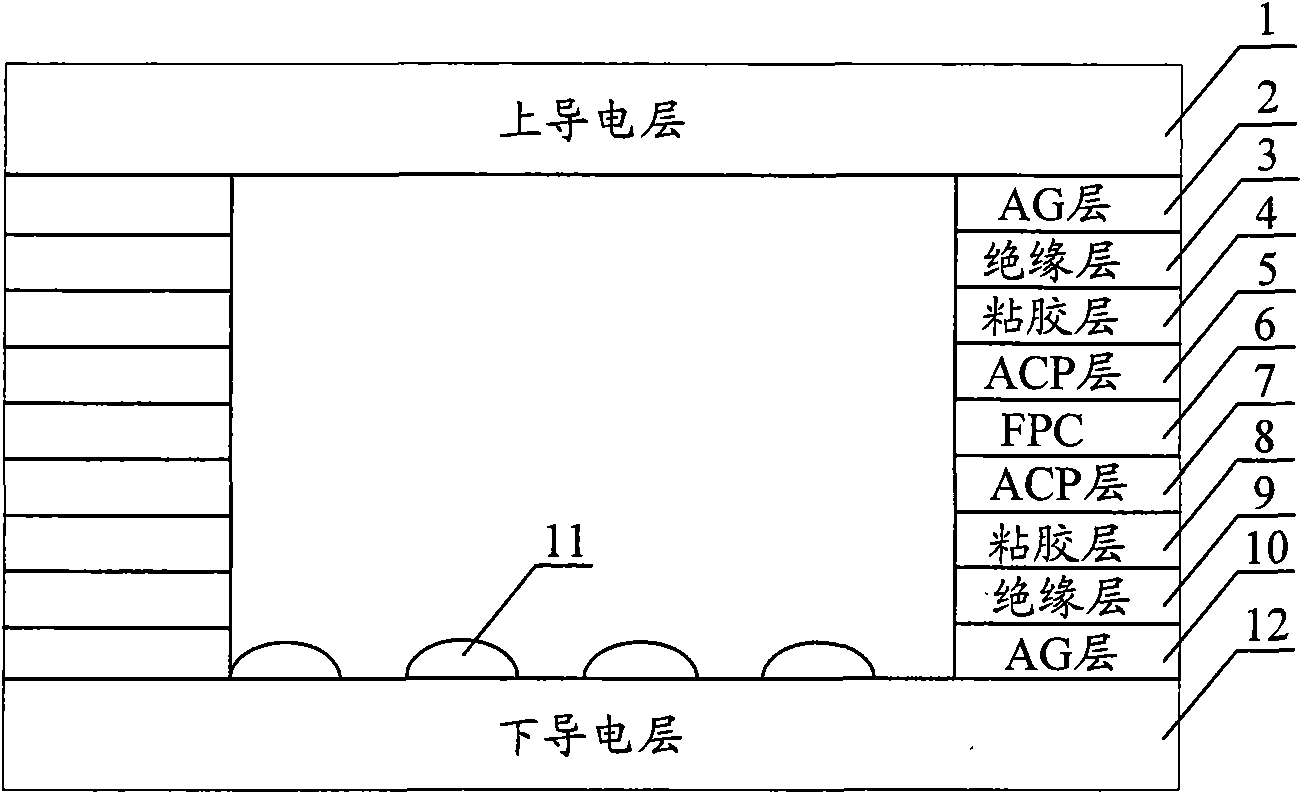

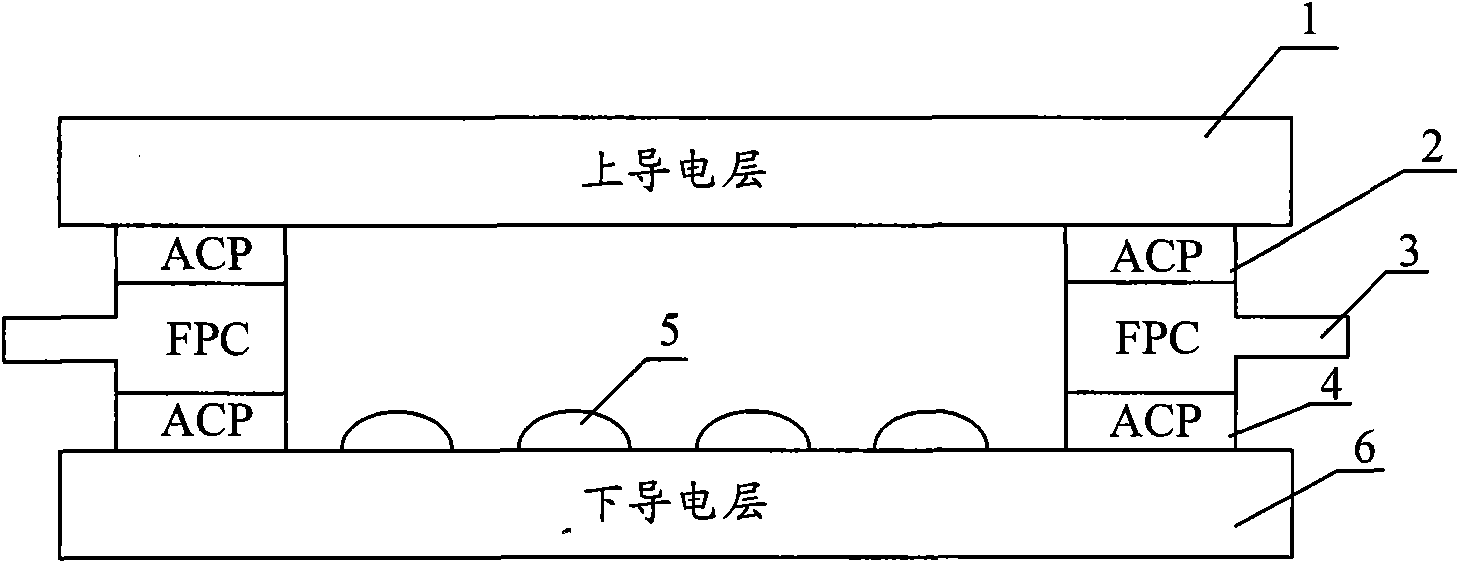

Resistance-type touch screen and manufacturing method thereof

ActiveCN101526874AShort processImprove product yieldInput/output processes for data processingPrinted circuit boardElectricity

The invention applies to the field of touch screens, and provides a resistance-type touch screen and a manufacturing method thereof. The touch screen comprises a lower conducting layer, a flexible printed circuit board and an upper conducting layer, wherein the lower conducting layer is taken as a voltage distribution layer; isolation points are attached to one side of the lower conducting layer; the flexible printed circuit board is positioned on the isolation-point side of the lower conducting layer and is electrically connected with the lower conducting layer; and the upper conducting layer is used for detecting voltage and is bonded to the flexible printed circuit board. The resistance-type touch screen provided by the invention has the advantages of leaving out conductive electrodes, insulation-layer printing, acid etching, demoulding and other intermediate links in a process, shortening process flow, improving product yield and saving manpower and material resources.

Owner:深圳市合力泰光电有限公司

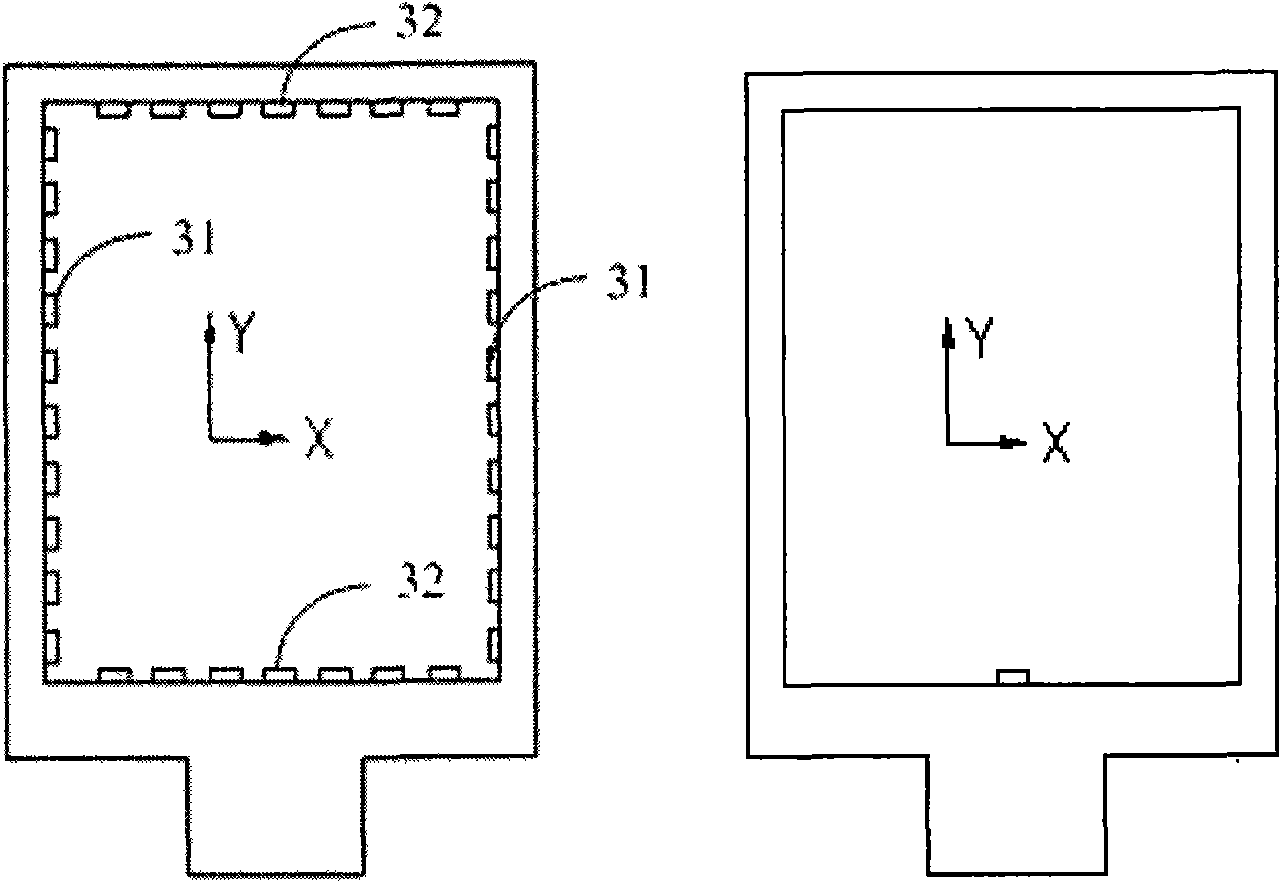

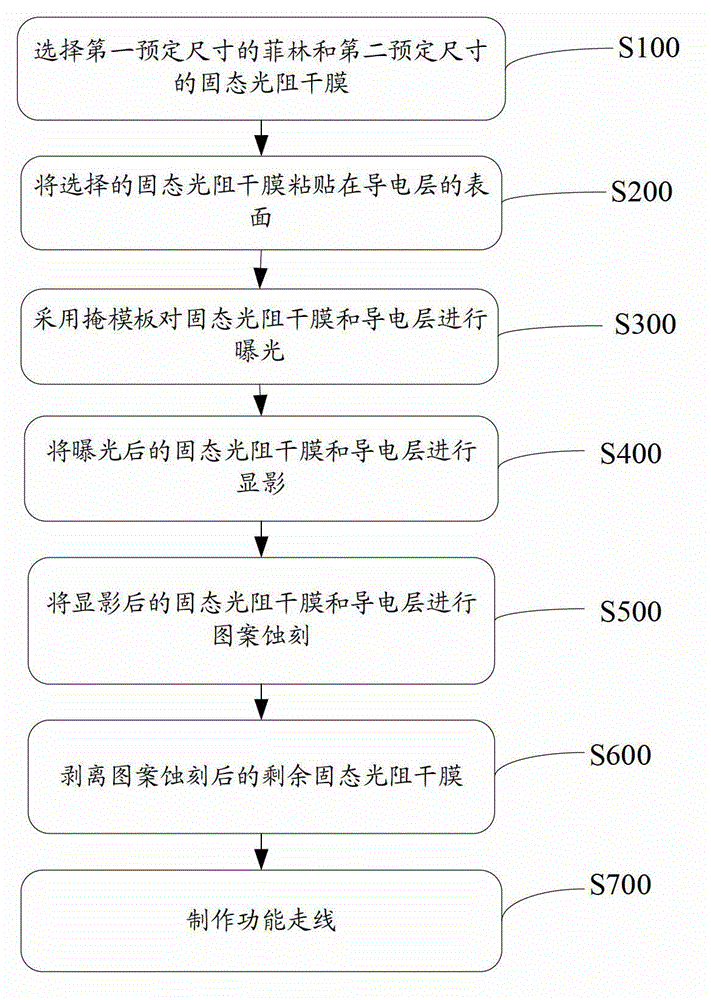

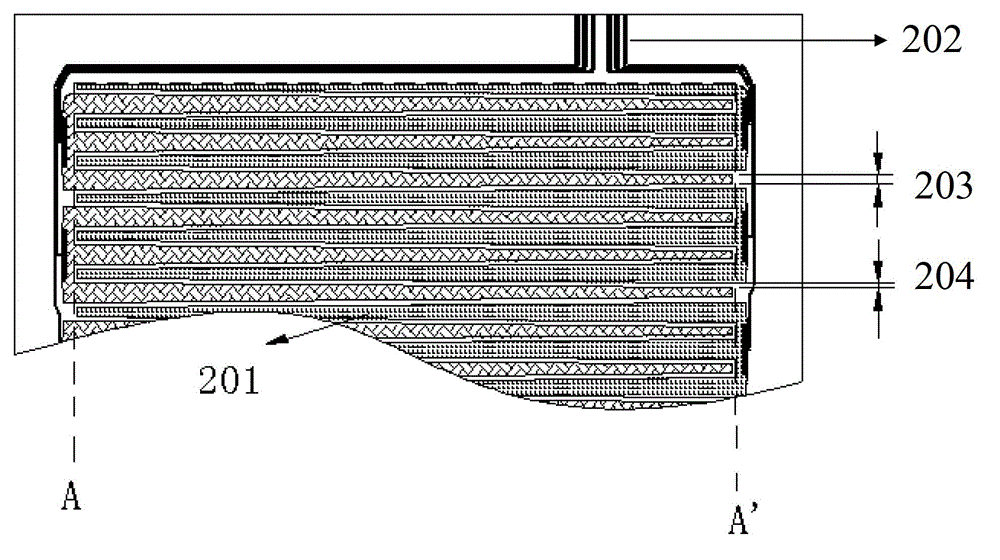

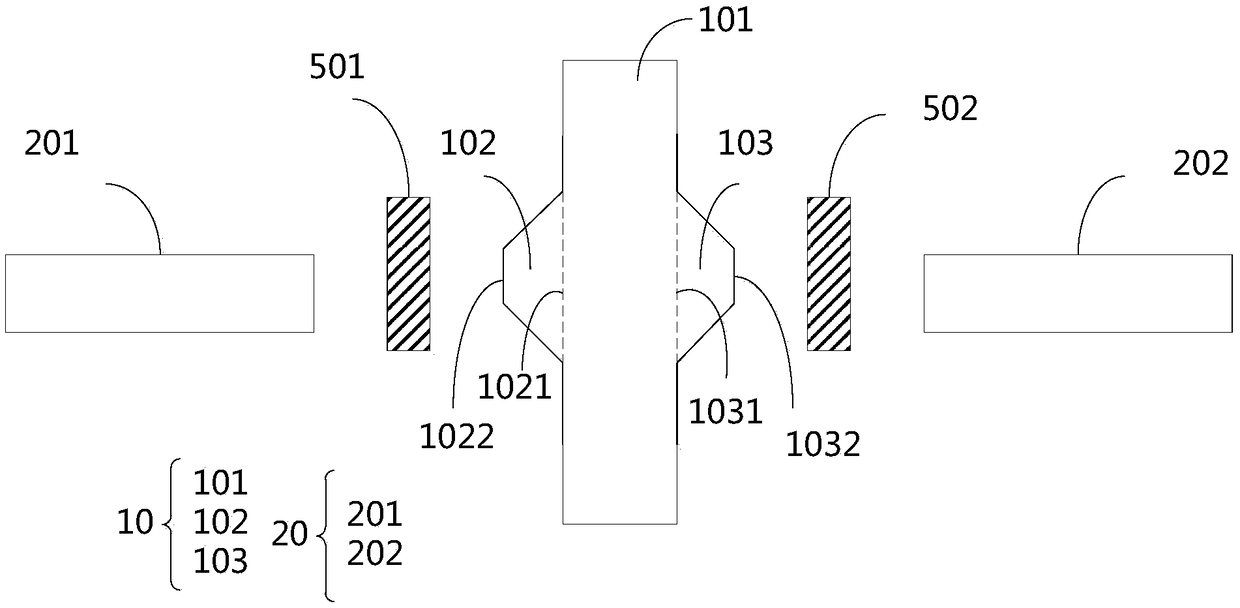

Touch inductor for capacitive touch screen with film structure and manufacturing method thereof

ActiveCN102880370AImprove product yieldReduce manufacturing costPhotomechanical apparatusInput/output processes for data processingInductorFilm structure

The invention provides a touch inductor for a capacitive touch screen with a film structure and a manufacturing method thereof. The manufacturing method comprises the following steps: selecting a film which has a first preset size and comprises a conductive layer and a solid-state light resistance dry film with a second preset size; adhering the solid-state light resistance dry film to the surface of the conductive layer; exposing the solid-state light resistance dry film and the conductive layer by employing a mask plate; developing the exposed solid-state light resistance dry film and the conductive layer; performing pattern etching on the developed solid-state light resistance dry film and the conductive layer; stripping the residual solid-state light resistance dry film subjected to pattern etching; and manufacturing functional routing. According to the manufacturing method, the problem that the method for coating liquid-state light resistance glue is difficult to manufacture is solved, the product performance of a touch screen is improved, the production cost is reduced, and the touch inductor has the advantage of extremely high cost performance.

Owner:TRULY OPTO ELECTRONICS

Array substrate and display panel

ActiveCN108666304AReduce the chance of static injuryImprove product yieldSemiconductor/solid-state device detailsSolid-state devicesEngineeringSurface plate

The invention provides an array substrate and a display panel. The array substrate comprises a first routing and a second routing, wherein the first routing comprises a main body part and a first projection part, and the first projection part is arranged on the side, close to the second wiring, of the main body part; the second wiring and the first projection part are oppositely arranged, and a first electrostatic protection electrode is arranged between the second wiring and the first projection part. The array substrate has the beneficial effects that, according to the array substrate and the display panel provided by the invention, the probability of damage by static electricity can be reduced, namely metal routings required in the panel cannot be influenced even if the damage by staticelectricity occurs, so that the product yield is improved.

Owner:SHENZHEN CHINA STAR OPTOELECTRONICS SEMICON DISPLAY TECH CO LTD

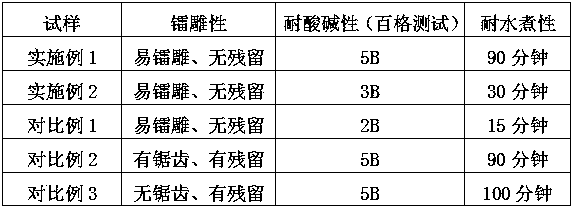

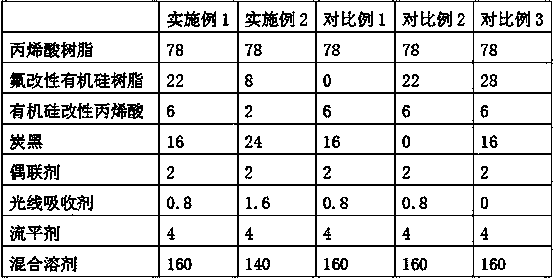

Coating for circuit of LDS shell

The invention discloses a coating for a circuit of an LDS shell. The coating comprises, by mass, 10 to 60 parts of an acrylic resin used as a matrix resin, 5 to 20 parts of a fluorine-modified organic silicone resin, 1 to 10 parts of a compatibilizer, 3 to 20 parts of carbon black, 0.1 to 8 parts of a light absorbent and a proper amount of a solvent. According to the invention, addition of 5 to 20 parts of the fluorine-modified organic silicone resin enables acid and alkali resistance and boiling resistance of the coating to be obviously improved; addition of 3 to 20 parts of carbon black and 0.1 to 8 parts of the light absorbent enables absorption of laser rays to be greatly improved, laser engraving performance of the coating to be substantially enhanced and generation of sawteeth and residues to be avoided.

Owner:GUANGDONG JANUS SMART GRP CO LTD

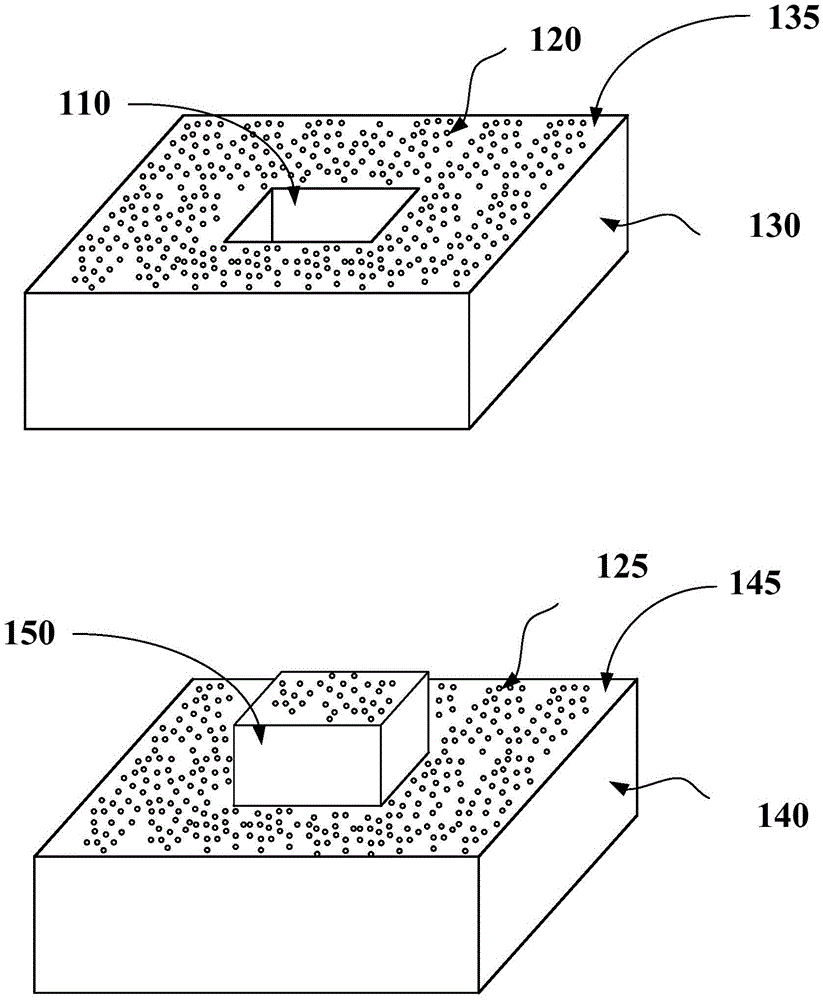

Wet paper-plastic pulp fishing system, wet paper-plastic product and method for forming wet paper-plastic product

ActiveCN105908577AAvoid bridgingImprove product yieldTextiles and paperFishingPulp and paper industry

The present invention relates to a wet paper-plastic pulp fishing system, which includes a pulp tank and a mold assembly. The pulp tank is used for loading a paper pulp. The mold assembly includes a lower mold and an upper mold. The lower mold is provided with a first surface and the first surface is provided with at least one groove and at least one first through hole. The upper mold is provided with a second surface and the second surface is provided with at least one lug corresponding to the at least one groove. The second surface of the upper mold is sunk to be below the liquid level of the paper pulp in the pulp tank, and is correspondingly compounded with the first surface of the lower mold below the liquid level of the paper pulp. Furthermore, at least one part of the paper pulp forms at least one wet embryonic layer between the first surface and the second surface of the upper mold, so that the bridging phenomenon in the prior art is avoided.

Owner:GOLDEN ARROW PRINTING

Laser drilling plate machining method adopting secondary outer-layer core material for reducing copper

InactiveCN103917049ASolve the problem of laser hole breakdownImprove product yieldPrinted circuit manufactureCopper foilLaser drilling

The invention discloses a laser drilling plate machining method adopting a secondary outer-layer core material for reducing copper. The laser drilling plate machining method is characterized by comprising secondary outer-layer graph manufacturing, laminating and laser drilling. The laser drilling plate machining method specifically comprises the following steps that a secondary outer-layer core material is selected; a secondary outer-layer bearing plate is manufactured; a secondary outer-layer graph is manufactured; a skylight layer is manufactured; laser drilling is performed on a skylight printed board. In the machining process of a laser drilling plate, 0.5OZ copper foil is used for replacing 0.33OZ copper foil in the secondary outer-layer graph of a printed circuit board, the copper reducing technology is adopted, so that when laser drilling is performed, the problem of laser hole breakdown is completely solved, and the product yield is greatly improved. The conflict that the graph layer requires thinner copper foil and the laser hole bearing plate requires thicker copper foil is removed, and the wide promotional significance is achieved.

Owner:DALIAN PACIFIC ELECTRONICS

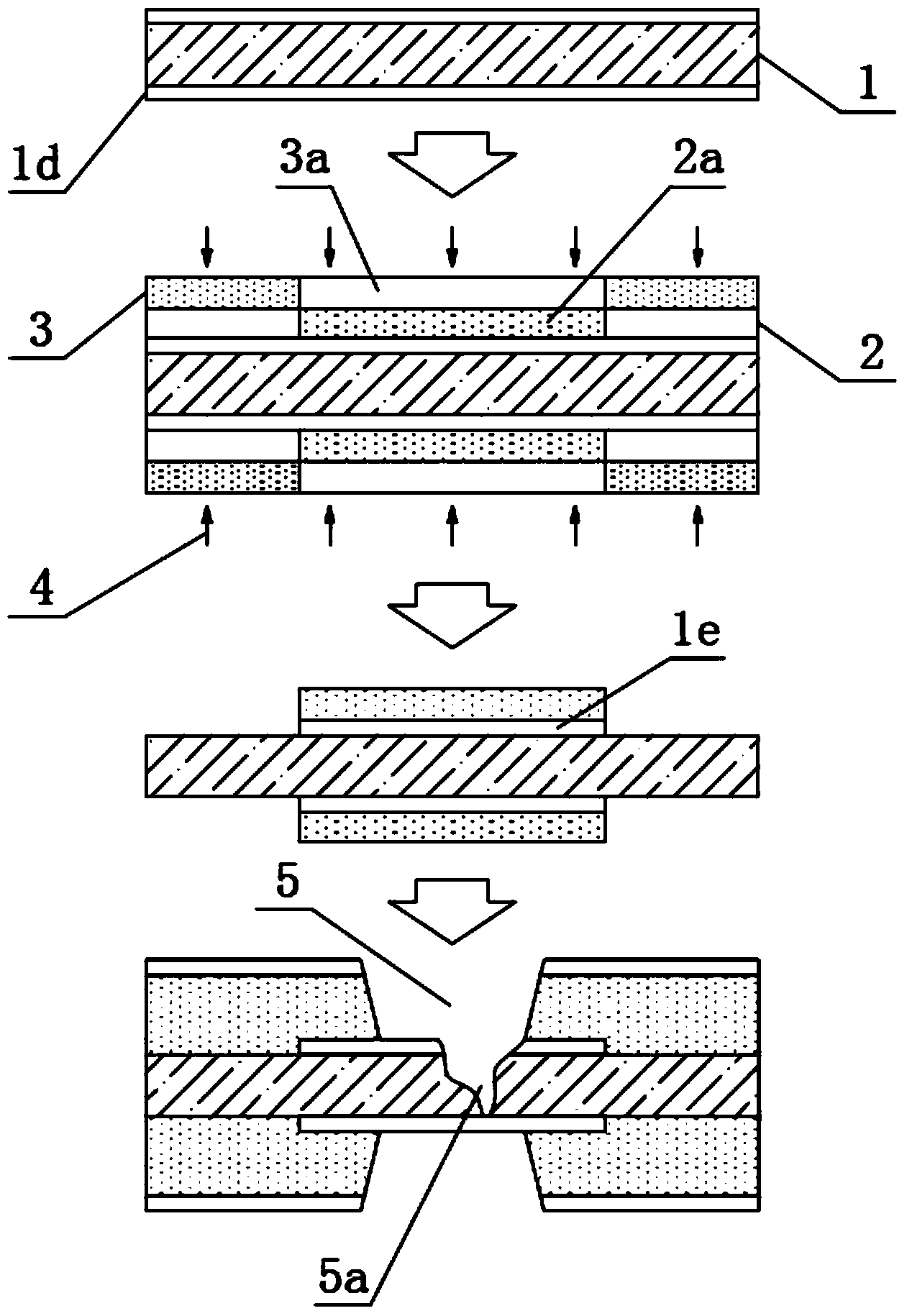

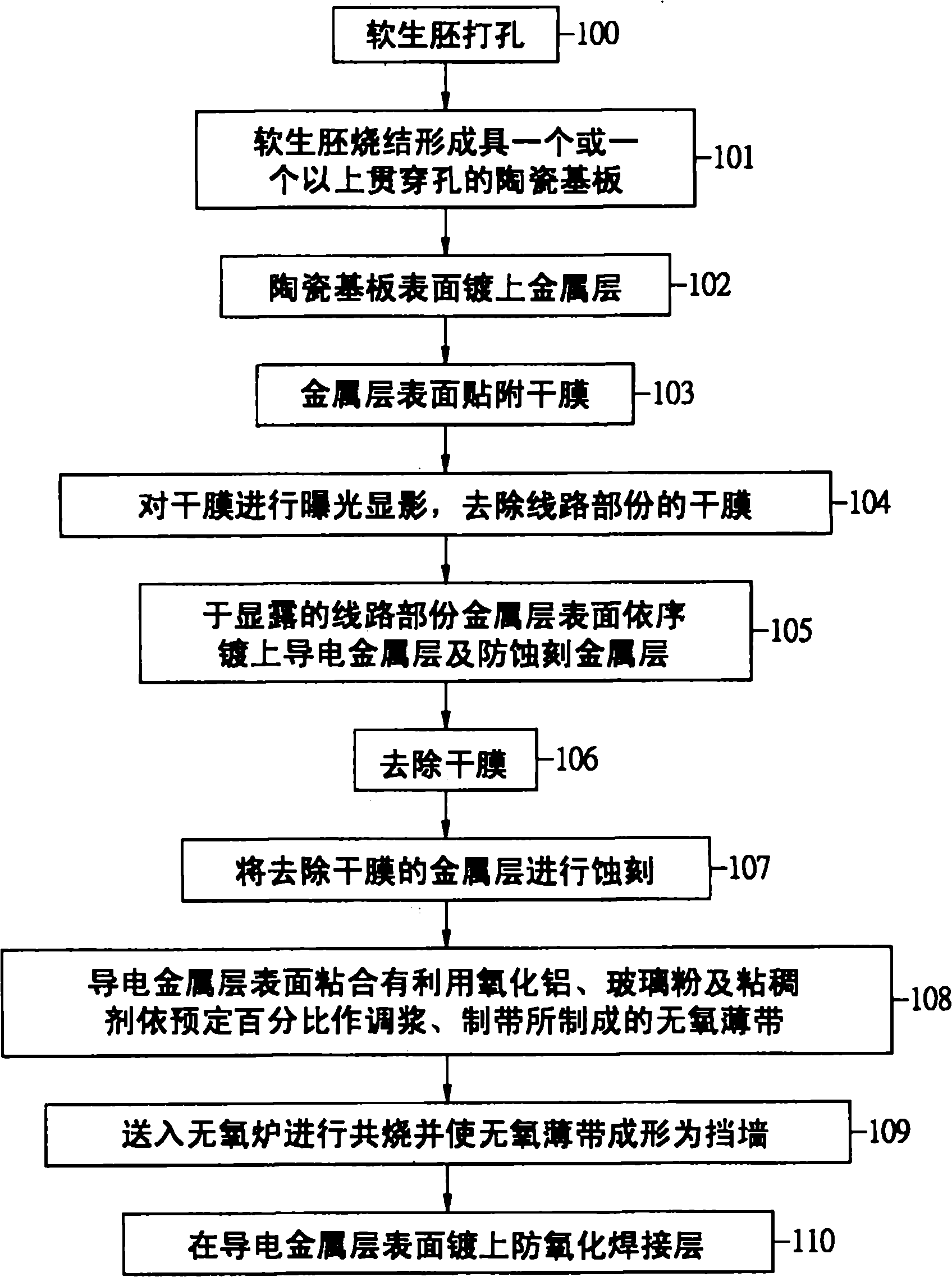

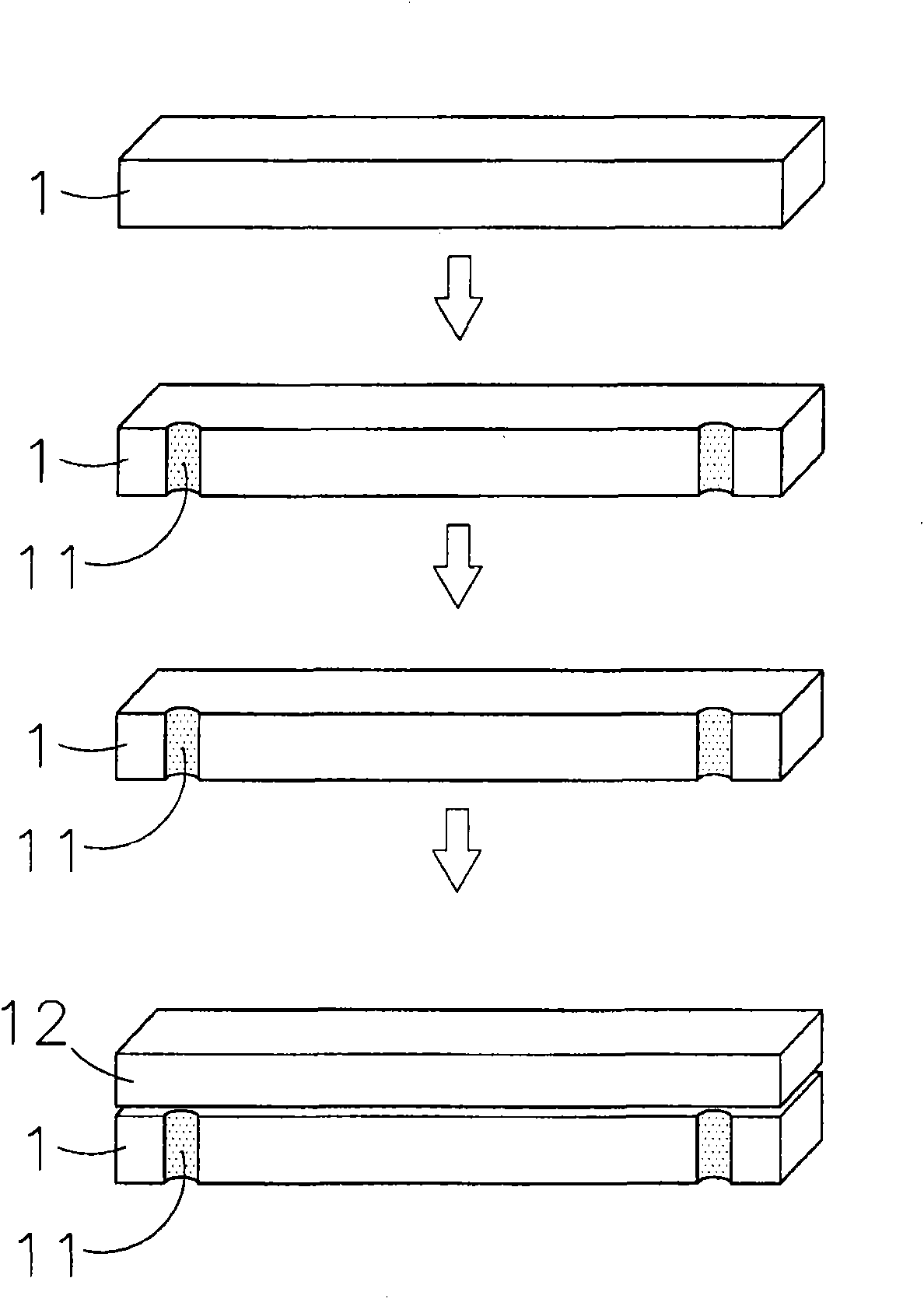

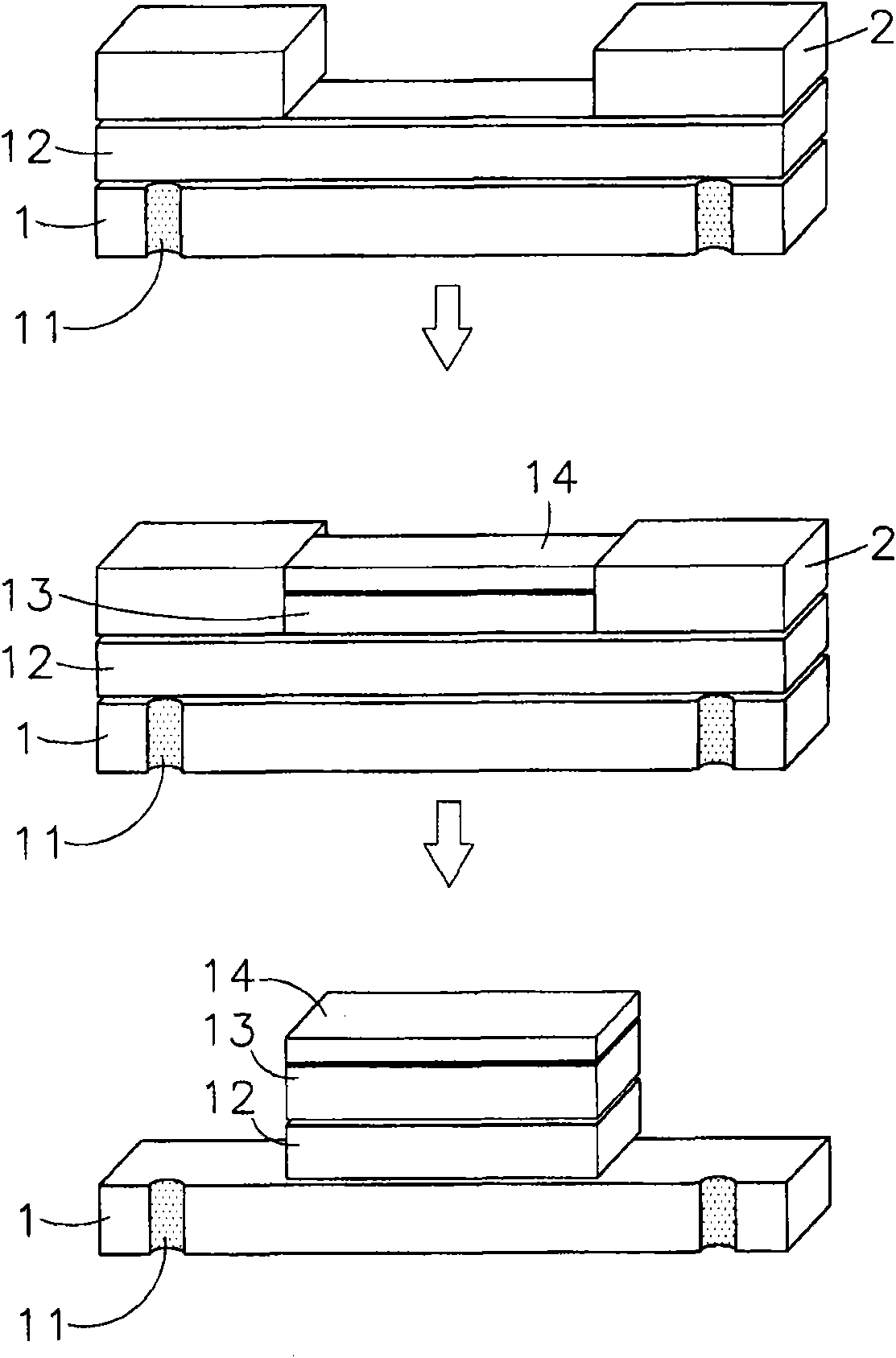

High-precision ceramic substrate process

InactiveCN102254831AImprove product yieldReduce manufacturing costSemiconductor/solid-state device manufacturingSemiconductor devicesElectroplatingMetal

The invention discloses a high-precision ceramic substrate process. In the high-precision ceramic substrate process, a ceramic substrate is required to be manufactured in electroplating and high-accuracy exposure / etching ways. Differences from an ordinary ceramic substrate manufactured in a printing way particularly after a metal layer is plated on the surface of the ceramic substrate are that: a dry film is attached to the surface of the metal layer, and is exposed and developed; a conductive metal layer is plated on the exposed surface of the metal layer; the metal layer and the conductive metal layer in a line part are retained by etching; an anaerobic thin strip is adhered to the surface of the conductive metal layer at a preset position, and is made by mixing a preset percent of ceramic powder, a preset percent of glass powder and a preset percent of pasting agent to form size and manufacturing the strip; and the ceramic substrate is fed into an anaerobic furnace for cofiring, and the anaerobic thin strip can form a barricade. The cofiring is performed in the anaerobic furnace, so the conductive metal layer may not be oxidized to overcome the shortcoming of stripping of the plated metal layer or no sticking in welding in subsequent welding and electroplating processes.

Owner:HOLY STONE ENTERPRISE

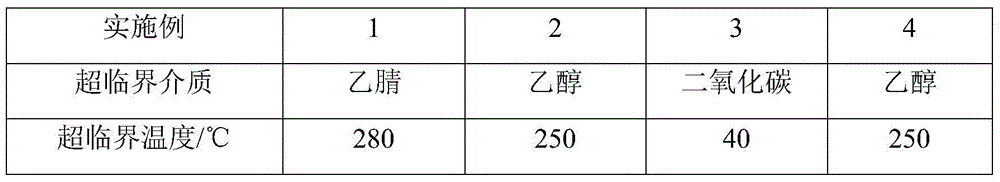

Supercritical drying method of sodium metaaluminate modified resin purified water-glass aerogel

PendingCN105776234AImprove product yieldIncrease productivityAlkali metal silicatesSolventSupercritical drying

The invention provides a supercritical drying method of sodium metaaluminate modified resin purified water-glass aerogel.Firstly, solvent replacement and hydrophobic modification are conducted on wet gel, then the wet gel subjected to the hydrophobic modification is put into a high-pressure reaction kettle, a supercritical medium is poured into the kettle, the heating temperature is set for heating, and degassing or reflux is performed to bring out the solvent in the wet gel till solvent recovery is completed after the medium in the reaction kettle reaches a supercritical state, wherein the supercritical medium is an acetonitrile, ethanol or carbon dioxide solvent.The product produced by adopting the supercritical drying method is high in product yield and high in production efficiency, slightly comes off and can be subjected to industrialized amplification.The supercritical drying method can be integrated to a production line.The whole preparation method is simple and easy to operate, free of strong acid and alkali corrosion, low in equipment requirement and suitable for industrial production after amplification.

Owner:ZHUO DA NEW MATERIAL TECH GRP

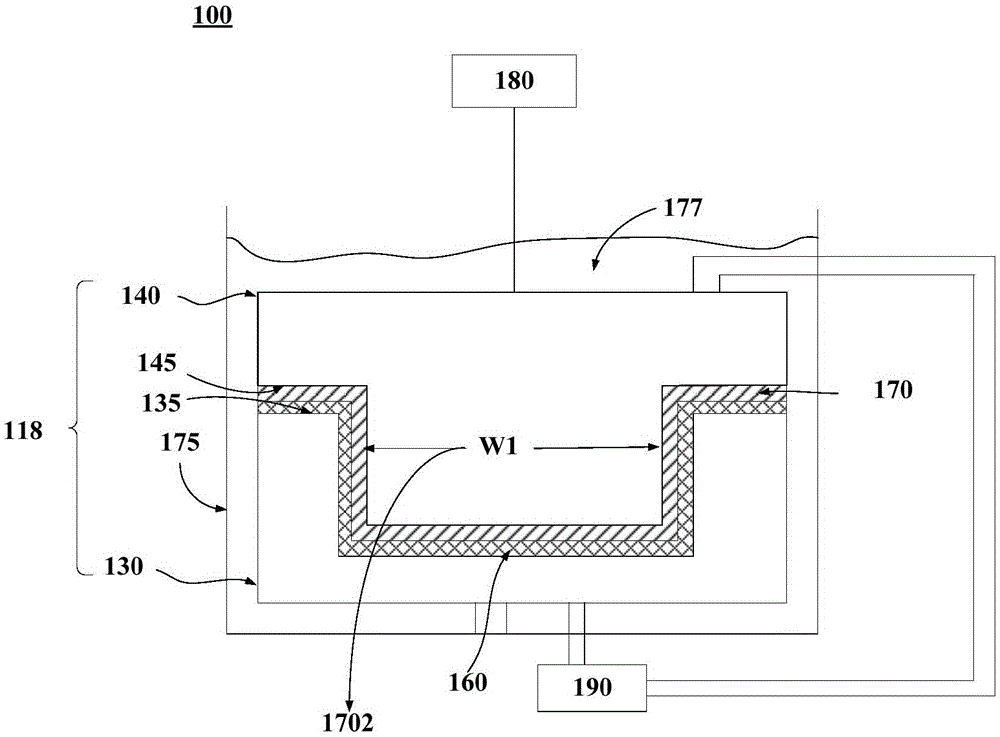

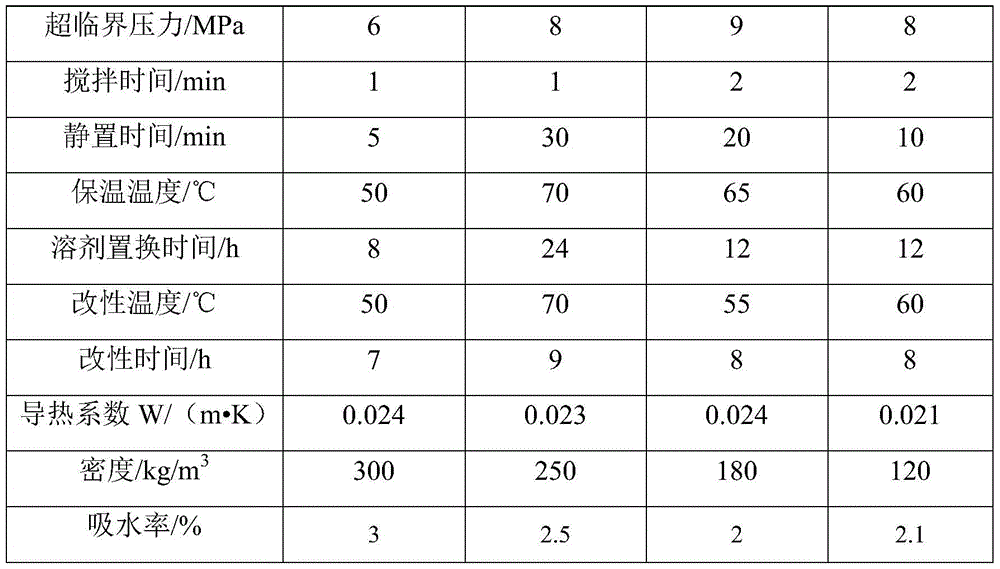

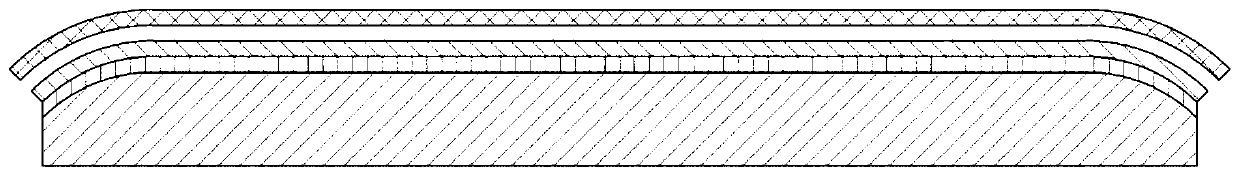

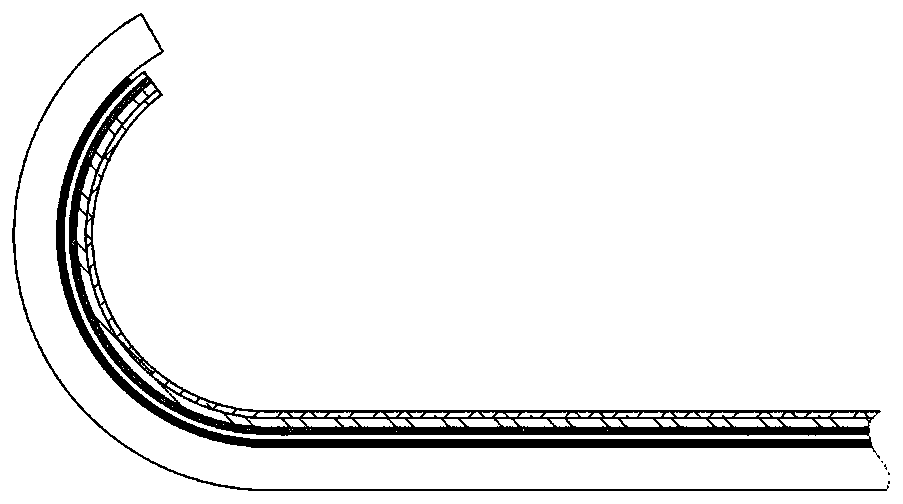

Assembly tool and process

PendingCN111145642AHigh bonding reliabilityImprove product yieldLaminationLamination apparatusPhysicsMechanical engineering

The invention provides an assembly tool and process which are applied to an assembly procedure of electronic equipment. The electronic equipment comprises a flexible display module and cover plate glass, the flexible display module and the cover plate glass are bonded, and the assembly tool comprises a clamping assembly, a profiling mold, a turnover mechanism and a base film; the profiling mold isprovided with a profiling part and a connecting part which are connected with each other; the clamping assembly is used for clamping and fixing the base film, the base film is arranged on the surfaceof the profiling mold, and the face, back on to the profiling mold, of the base film is used for being bonded with the flexible display module; and the turnover mechanism is arranged on the surface,back on to the profiling mold, of the base film, is arranged opposite to the two sides of the profiling mold; and the turnover mechanism is used for driving the base film to move from one side of theprofiling part to the other side of the profiling part. According to the embodiment of the invention, the assembly of an inverted buckling type flexible screen and the cover plate glass can be realized, the tight fitting of a bent part is ensured, the bonding reliability is improved, and the product yield is improved.

Owner:VIVO MOBILE COMM CO LTD

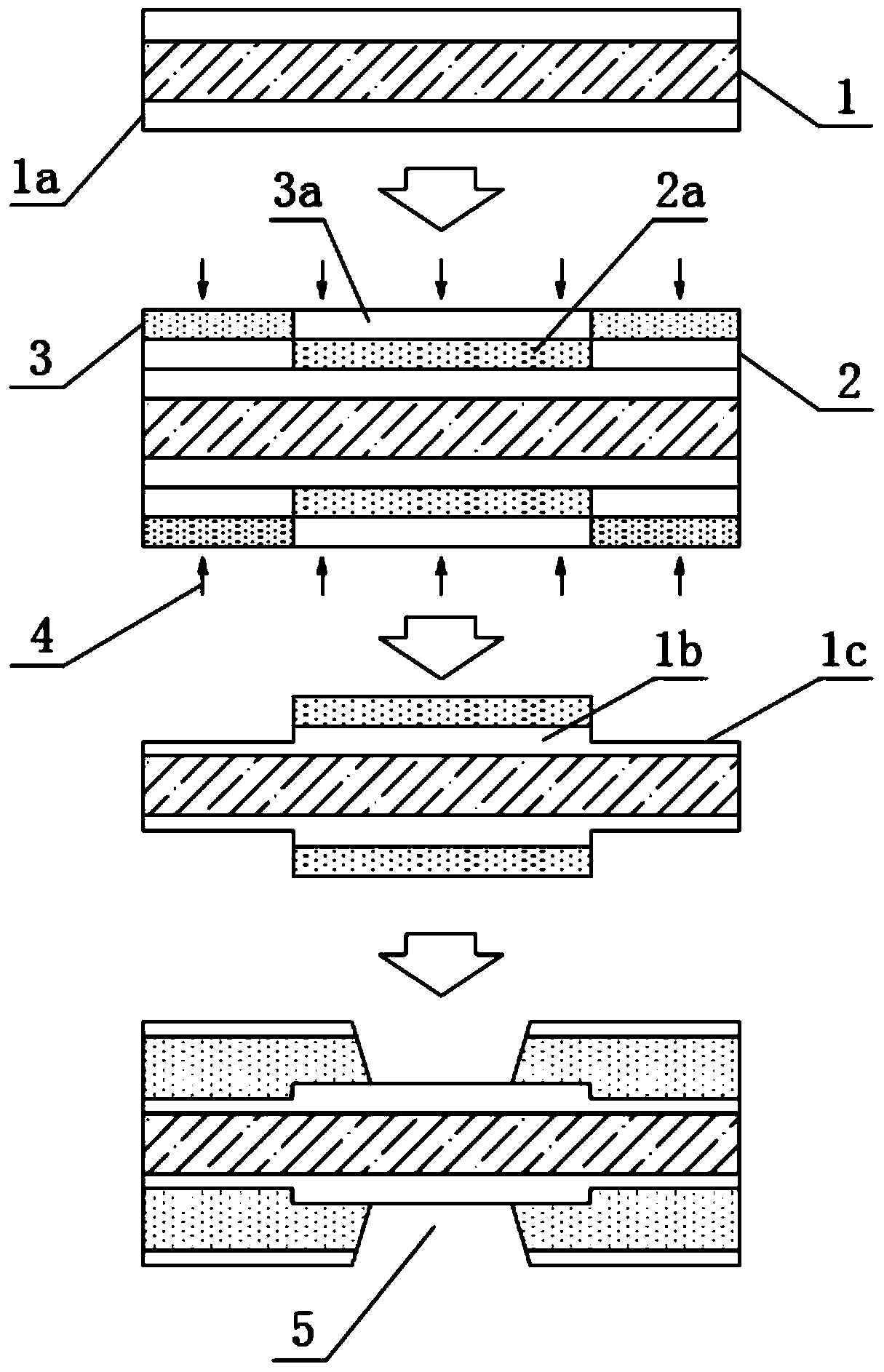

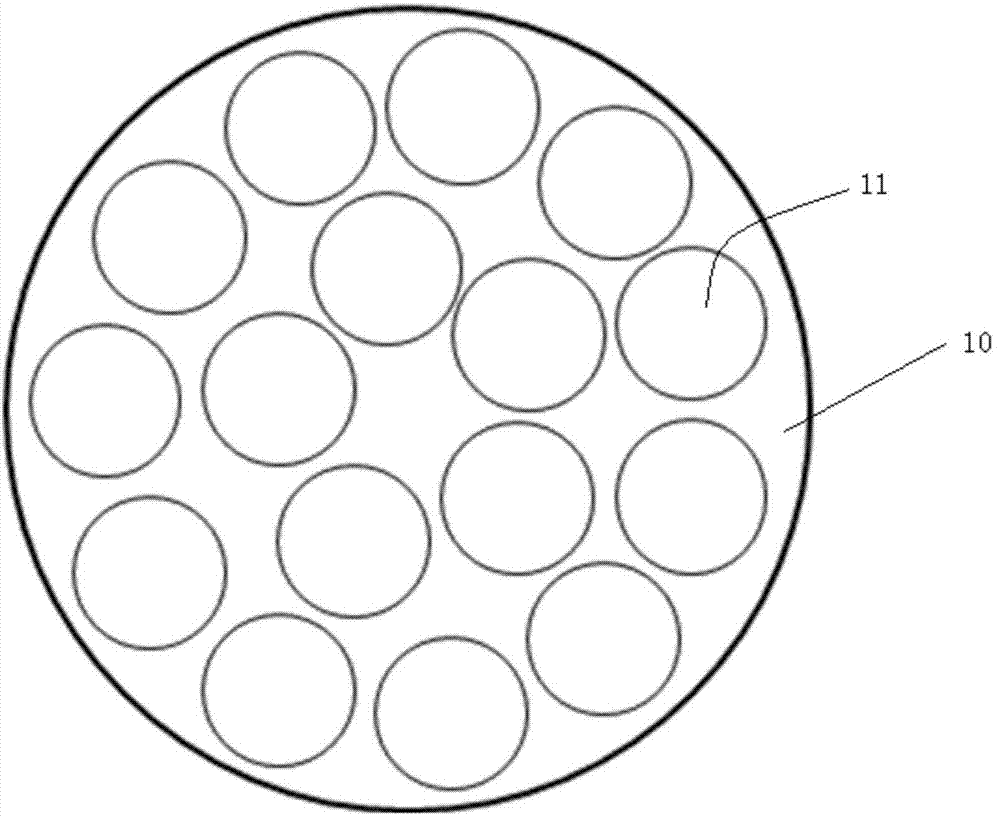

Multilayer line manufacturing process of wafer-level micro electromechanical system chip encapsulation technology

InactiveCN101870449AImprove product yieldEfficiently cope with downsizingDecorative surface effectsChemical vapor deposition coatingSolder maskCopper plating

The invention discloses a multilayer line manufacturing process of wafer-level micro electromechanical system chip encapsulation technology. The process comprises the following flows of: pre-processing, wafer thinning, exposure and development, etching, insulating layer coating, laser drilling, copper sputtering, chemical copper plating pretreatment, chemical copper plating, electric copper plating, exposure and development, copper etching, insulating layer coating and exposure and development, laser drilling, copper sputtering, chemical copper plating pretreatment, chemical copper plating, electric copper plating, exposure and development, copper etching, N (N is more than or equal to 0) times (insulating layer coating and exposure and development, laser drilling, copper sputtering, chemical copper plating pretreatment, chemical copper plating, electric copper plating, exposure and development, copper etching), acid chemical nickel plating, chemical cyanide gilding, solder mask coating and exposure and development, BGA forming, and subsequent cutting, testing and packing. The process for forming a multilayer mutual conduction line effectively deals with product size reduction and line denseness, and improves the yield of products.

Owner:HUATIAN TECH KUNSHAN ELECTRONICS

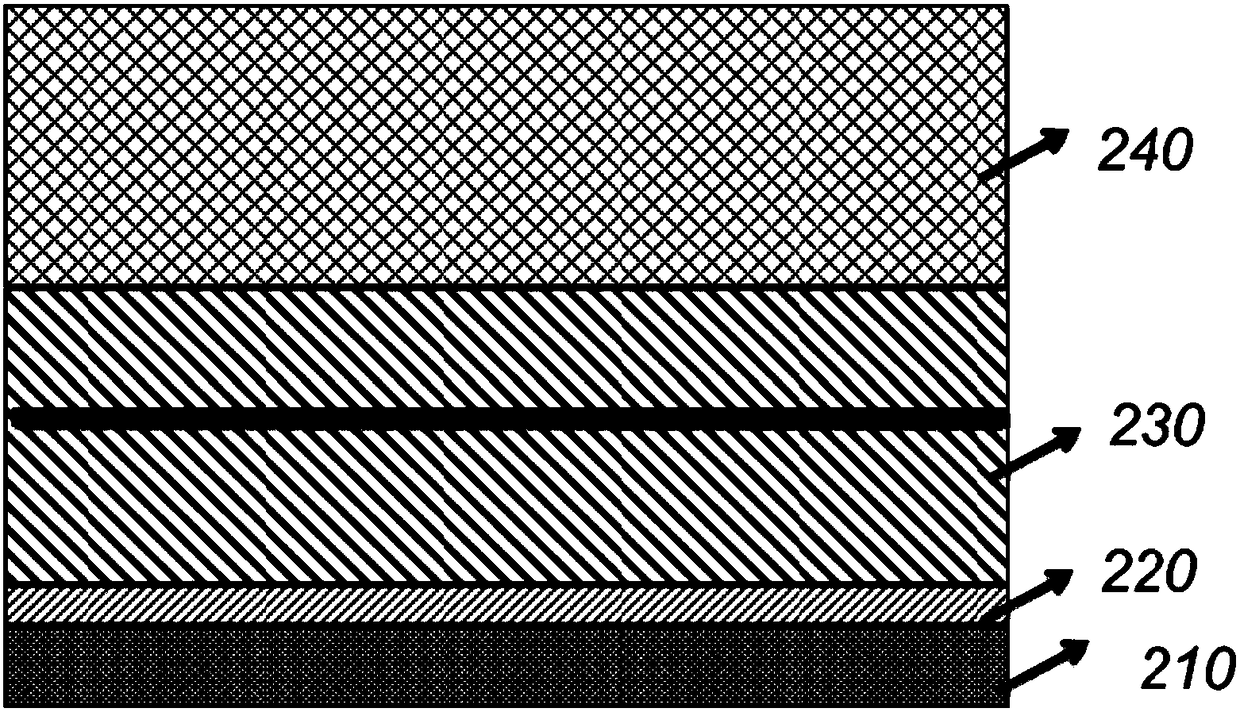

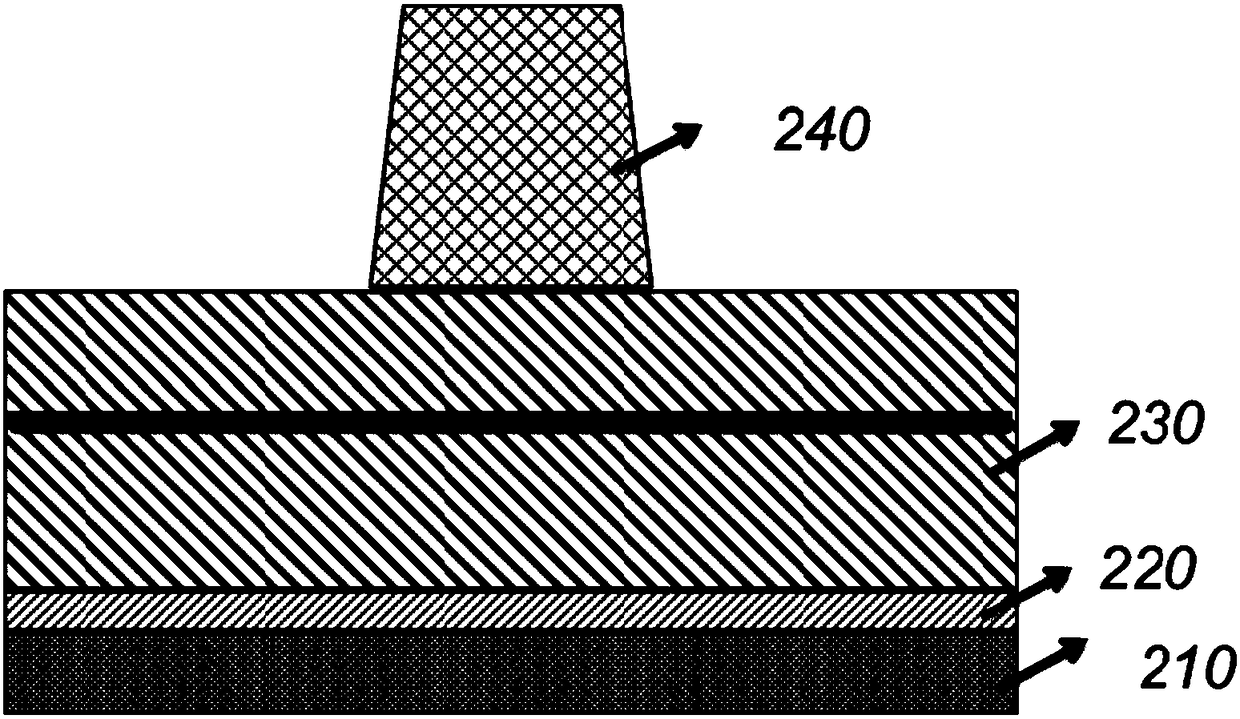

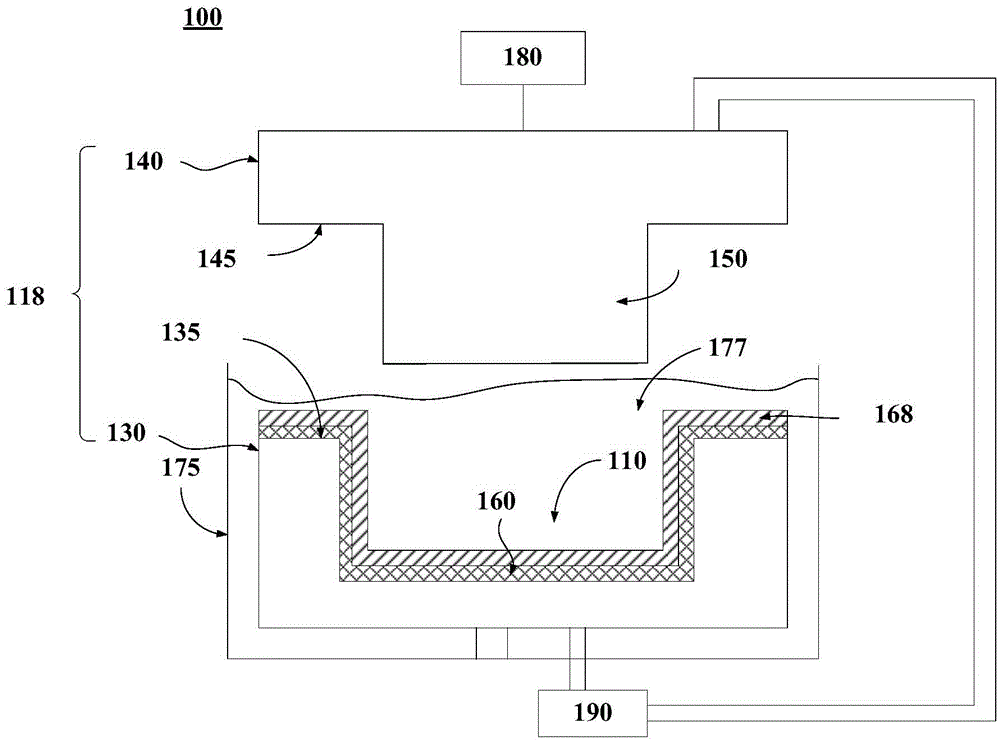

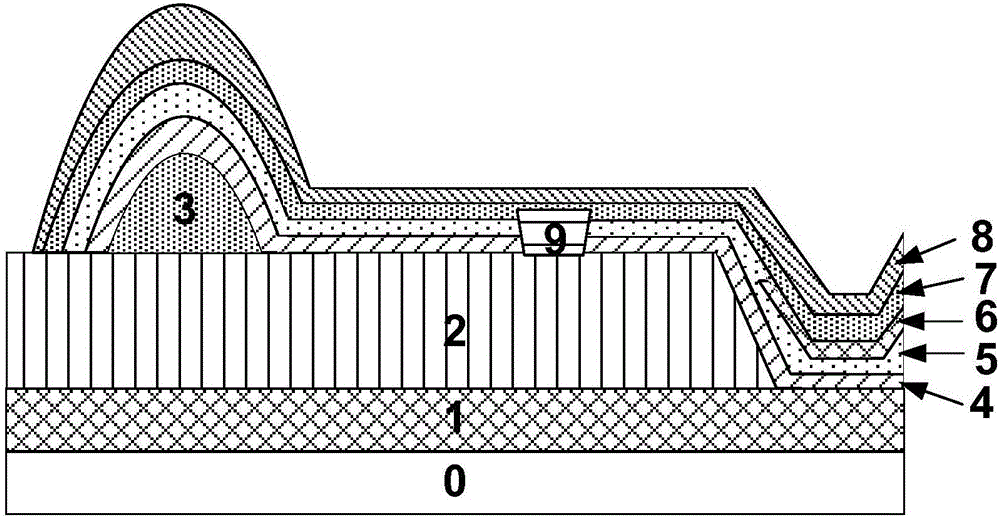

OLED (Organic Light Emitting Diode) display device and production method thereof

ActiveCN106783927AImprove product yieldReduce lateral leakageSolid-state devicesSemiconductor/solid-state device manufacturingHole injection layerElectron transporting layer

The invention discloses an OLED (Organic Light Emitting Diode) display device and a production method thereof. The OLED display device comprises a substrate, anode layers, pixel defining layers, hole injecting layers, hole transmitting layers, light emitting layers, electron transporting layers, electron injecting layers, spacing pillars and blocking pillars positioned on a region beyond of the spacing pillars on pixel spaced regions; the blocking pillars at least penetrate through the hole transporting layers and the hole injecting layers. In the OLED display device provided by the invention, one spacing pillar is produced in the pixel spacing region between two adjacent light emitting pixels with different colors, and at least one of two inner angles, close to the pixel spacing region, of each blocking pillar is greater than 90 degrees, so that when organic materials such as the hole transporting layers and the hole injecting layers are evaporated, the hole transporting layers and the hole injecting layers can be broken at positions of the blocking pillars, and further transverse current leakage between a certain light-emitting pixel and the adjacent light emitting pixel is reduced when the certain light-emitting pixel is lightened; the problem of light stealing of other light-emitting pixels is solved, and the yield of the product is improved.

Owner:WUHAN TIANMA MICRO ELECTRONICS CO LTD +1

Production process of air-conditioner condenser pipe

InactiveCN106239076AImprove product yieldReduce manufacturing costManufacturing engineeringMaterials preparation

The invention discloses a production process of an air-conditioner condenser pipe. The production process comprises the following steps of preparing materials, rolling, drawing, straightening, washing, annealing, detecting flaws and putting in storage. According to the process, existing equipment is employed for production, special equipment is not needed so that the air-conditioner condenser pipe can be produced in large scale; compared with a conventional production process, the process is high in product yield and low in production cost after being employed for production, the material waste is reduced, the produced condenser pipe is high in quality and the competitiveness of an enterprise is improved.

Owner:ANHUI TIANXIANG AIR CONDITIONING SCI & TECH CO LTD

Flexible light-emitting panel, preparation method of flexible light-emitting panel and display equipment

InactiveCN110491914APrevent delaminationImprove product yieldSolid-state devicesSemiconductor/solid-state device manufacturingBackplaneEngineering

The invention discloses a flexible light-emitting panel, a preparation method of the flexible light-emitting panel, and display equipment. The flexible light-emitting panel comprises: a back plate; anadhesive layer that comprises a first sub-adhesive layer arranged on the back plate and a plurality of second sub-adhesive layers protruding in the direction away from the back plate from the first sub-adhesive layer; a flexible layer arranged on the first sub-adhesive layer, wherein the flexible layer comprises a plurality of sub-flexible layers arranged at intervals, the second sub-adhesive layers are located in the intervals, and the second sub-adhesive layers correspond to the intervals in a one-to-one mode; an array substrate, a light-emitting device and a packaging layer are sequentially arranged on each sub-flexible layer in a stacked mode, and a cover plate is arranged on the packaging layer and the second sub-adhesive layers in a covering manner. According to the invention, interlayer stripping among a plurality of functional layers for preparing the flexible light-emitting panel can be avoided, and the product yield is improved.

Owner:WUHAN CHINA STAR OPTOELECTRONICS SEMICON DISPLAY TECH CO LTD

Method for grinding silicon chips

The invention discloses a method for grinding silicon chips. The method is characterized in that the silicon chips are ground by the aid of PWA9 grinding sand slurry; the silicon chips are respectively ground under multilevel pressures, the first-level pressures range from 265kg to 275kg, the rotational speeds range from 4 revolutions / min to 6 revolutions / min, rotational speed ratios range from 0.4 to 0.6, and the grinding time ranges from 40 seconds to 50 seconds; the second-level pressures range from 140kg to 160kg, the rotational speeds range from 14 revolutions / min to 16 revolutions / min, rotational speed ratios range from 0.4 to 0.6, and the grinding time ranges from 60 seconds to 120 seconds; the third-level pressures range from 110kg to 120kg, the rotational speeds range from 24 revolutions / min to 26 revolutions / min, rotational speed ratios range from 0.4 to 0.6, and the grinding time ranges from 60 seconds to 120 seconds; the fourth-level pressures range from 90kg to 110kg, the rotational speeds range from 28 revolutions / min to 32 revolutions / min, rotational speed ratios range from 0.4 to 0.6, and the grinding time ranges from 40 seconds to 50 seconds; the fifth-level pressures range from 65kg to 75kg, the rotational speeds range from 34 revolutions / min to 36 revolutions / min, rotational speed ratios range from 0.4 to 0.6, and the grinding time ranges from 9min to 11min; the various levels of pressures are switched over at time intervals which range from 5 seconds to 15 seconds. The method for grinding the silicon chips has the advantages that the silicon chips are ground by the aid of PWA9 grinding sand, and accordingly the grinding cost can be reduced by 10%; ground products are high in yield, and the defect rate due to saw marks and fragments can be reduced and reaches 0.5%.

Owner:JINGHUA ELECTRONICS MATERIAL