Method for forming non-load-effect large size groove

A large-scale, no-load technology, used in electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve the problems of fast etching speed, slow etching rate, and connection failure in small-scale trenches, and achieve improved etching. Process performance, the effect of expanding the etching process window, and improving product yield

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] The specific embodiment of the present invention will be further described below in conjunction with accompanying drawing:

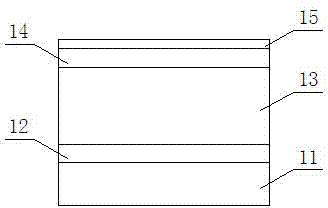

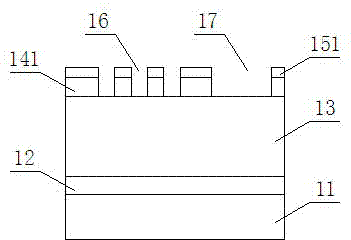

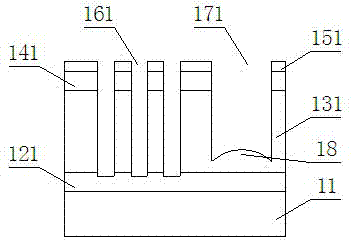

[0028] Figure 6-12 It is a schematic structural diagram of the process flow of the method for forming a large-size groove without load effect in the present invention;

[0029] like Figure 6-12 As shown, first, an interlayer dielectric layer (inter layer dielectric, ILD for short) 21 with a thickness of 300A, a barrier layer 22 made of SiN with a thickness of 2500A, and a barrier layer 22 made of SiN with a thickness of 400A are sequentially deposited from bottom to top on the semiconductor structure 2 . A low dielectric constant dielectric layer 23 of silicon oxide (FSG) containing F, a metal hard mask 24 made of TiN with a thickness of 50A, and a metal hard mask 24 made of silicon dioxide (SiO 2 ) oxide layer 25; wherein, the interlayer dielectric layer 21 covers the upper surface of the semiconductor structure 2, the barrier layer 22 covers...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More