Quad-core DSP and 1553B bus controller integrated SIP encapsulated circuit

A technology of bus controller and packaged circuit, which is applied to the architecture with a single central processing unit, instruments, electrical digital data processing, etc., can solve the problem that the computer controller cannot meet the requirements of small size and weight, and achieve the improvement of technical capabilities , high signal integrity, the effect of breaking technical barriers

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0015] In order to make the purpose, content, and advantages of the present invention clearer, the specific implementation manners of the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments.

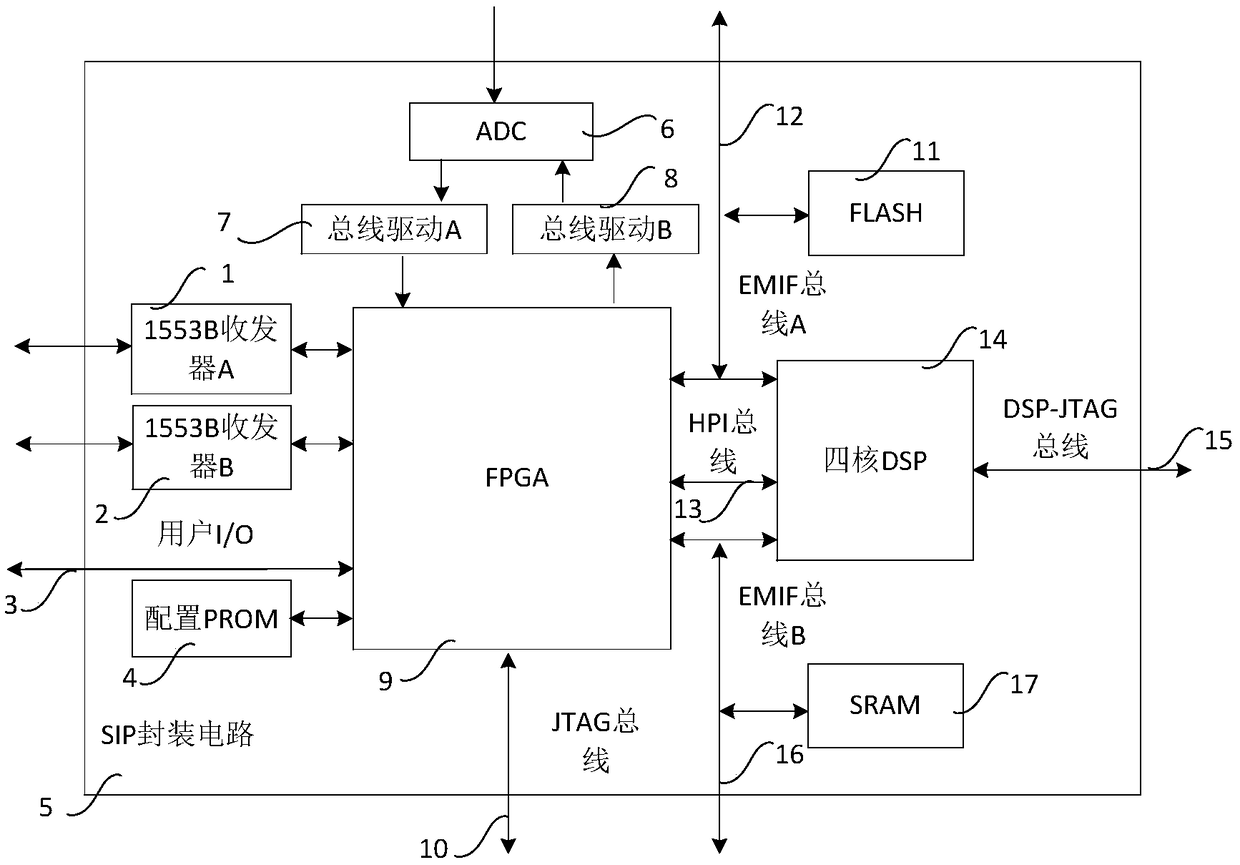

[0016] figure 1 Shown is the schematic diagram of general controller SIP circuit of the present invention, as figure 1 As shown, a general controller SIP circuit of the present invention includes: 1553B transceiver A 1, 1553B transceiver B 2, user I / O 3, PROM 4, ADC 6, bus driver A 7, bus driver B 8, FPGA 9, JTAG bus 10, FLASH 11, EMIF bus A 12, HPI bus 13, quad-core DSP 14, DSP-JTAG 15, EMIF bus B 16 and SRAM 17.

[0017] Such as figure 1 As shown, FPGA 9 and quad-core DSP 14 are bidirectionally connected through EMIF bus A 13, FPGA 9 and quad-core DSP 14 are bidirectionally connected through EMIF bus B 16, FPGA 9 and quad-core DSP 14 are bidirectionally connected through HPI 13 bus, FLASH 11 and FPGA 9. Quad-core ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More