A System-on-Chip Based on Two-Level Boot Structure

A system-level chip and connecting chip technology, which is applied in the direction of instruments, calculations, and electrical digital data processing, can solve the problems of no address input, the processor cannot randomly fetch instructions to access, and no discovery, etc., so as to save time and be very reliable. Effects of portability and versatility, improved verifiability and testability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0021] The technical solutions of the present invention will be further described below with reference to the accompanying drawings and specific examples.

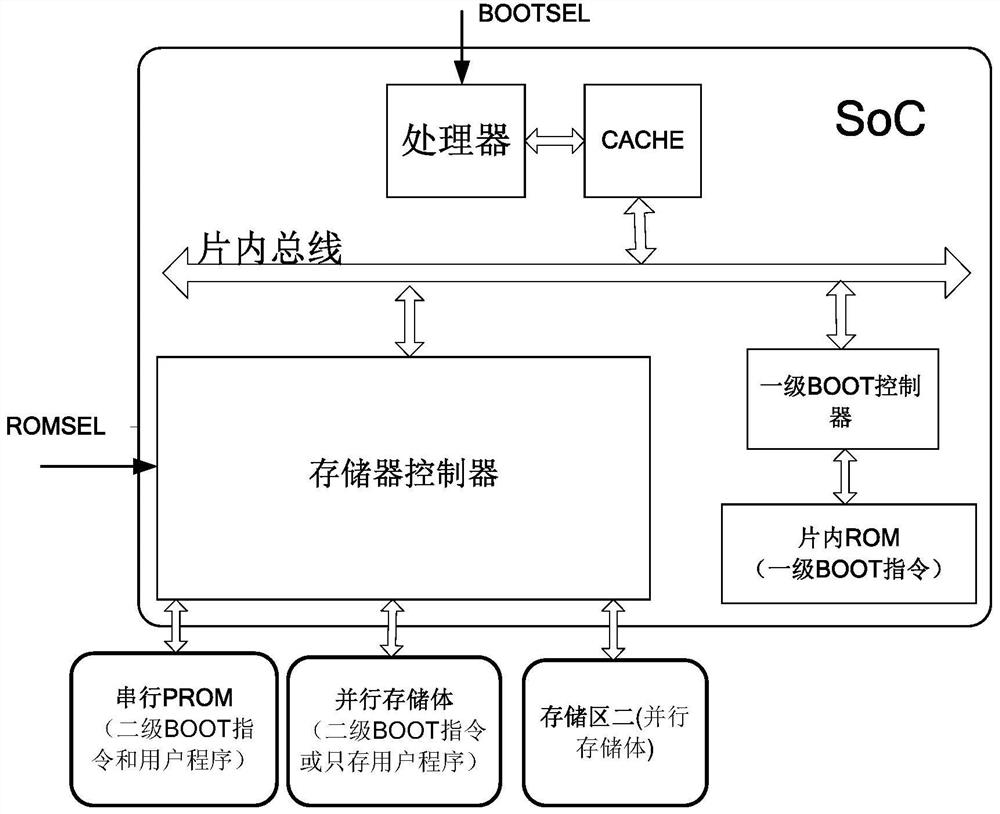

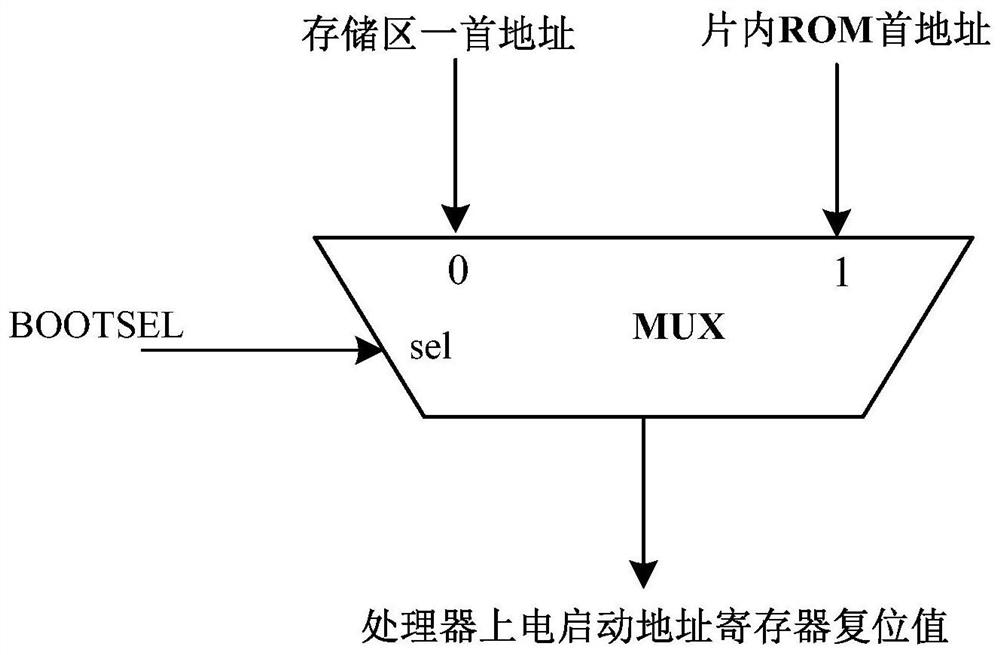

[0022] The present invention provides a system-level chip based on a two-stage BOOT structure, such as figure 1 As shown, including a memory controller, a memory controller connecting piece, a cache memory (Cache) between the in-chip buses and the processor, and the in-chip boke is set between the slide ROM; memory The controller connects two external storage area one and storage area two, where the storage area includes a serial PROM and parallel MRAM, and the memory controller can only access one of the one; the storage area is parallel SRAM. Where the processor is connected to the Bootsel control pin, the memory controller is connected to the ROMSEL control pin.

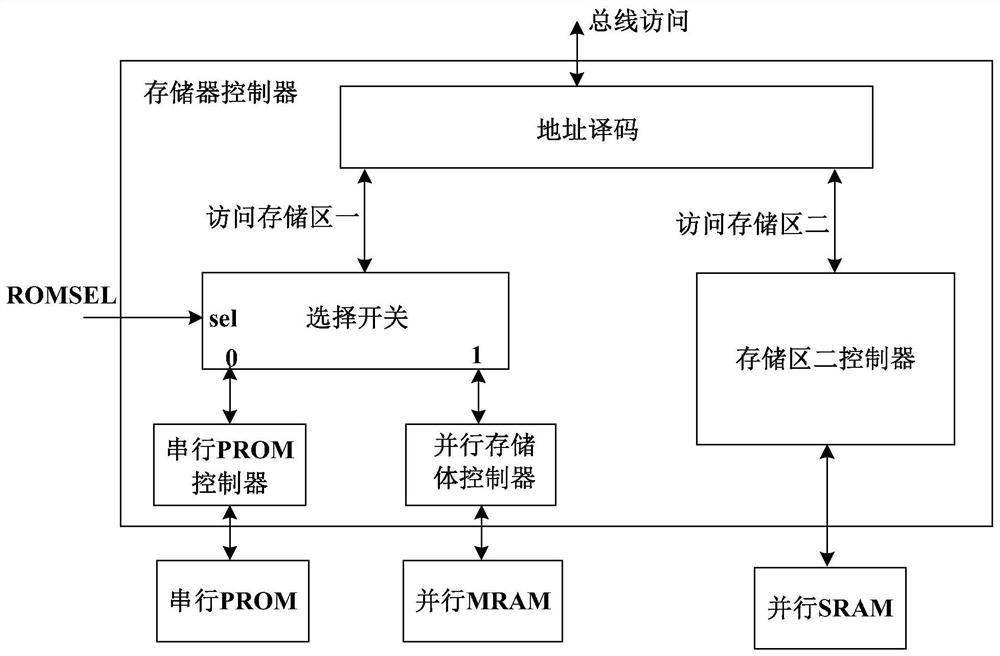

[0023] Such as image 3 As shown, the memory controller includes an address decoding unit connected to a sheet bus, and an address decoding unit is connected to a ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More