Analog circuit fault feature extraction method based on cloud correlation coefficient matrix

A technology for simulating circuit faults and correlation coefficients, which is applied in the feature extraction of analog circuit faults, cloud correlation coefficient matrix to realize the feature extraction of analog circuits, can solve the problems of low similarity and tolerance of circuit components, and achieve low similarity and difference Large, high-resolution effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

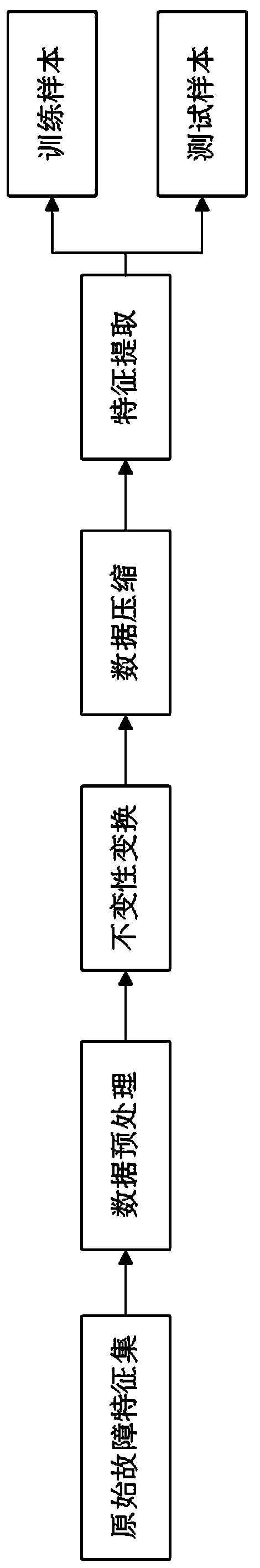

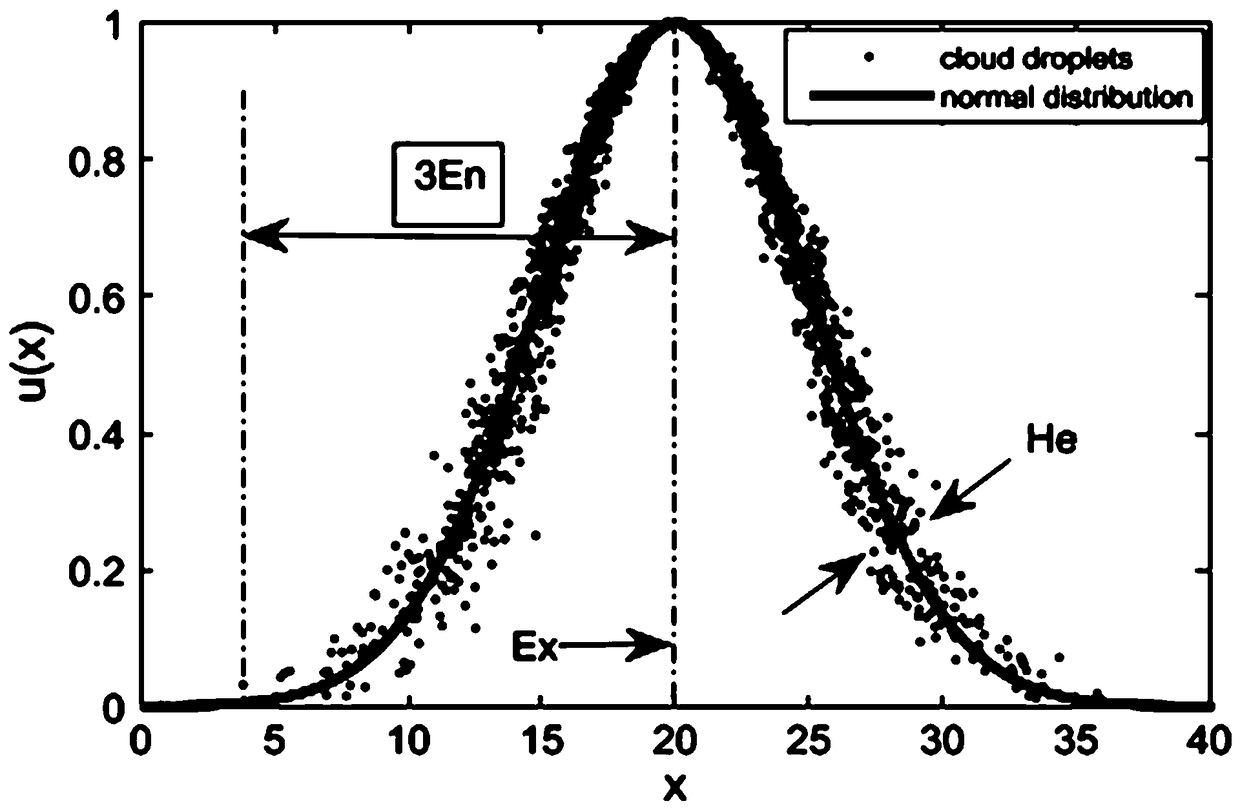

Method used

Image

Examples

Embodiment 1

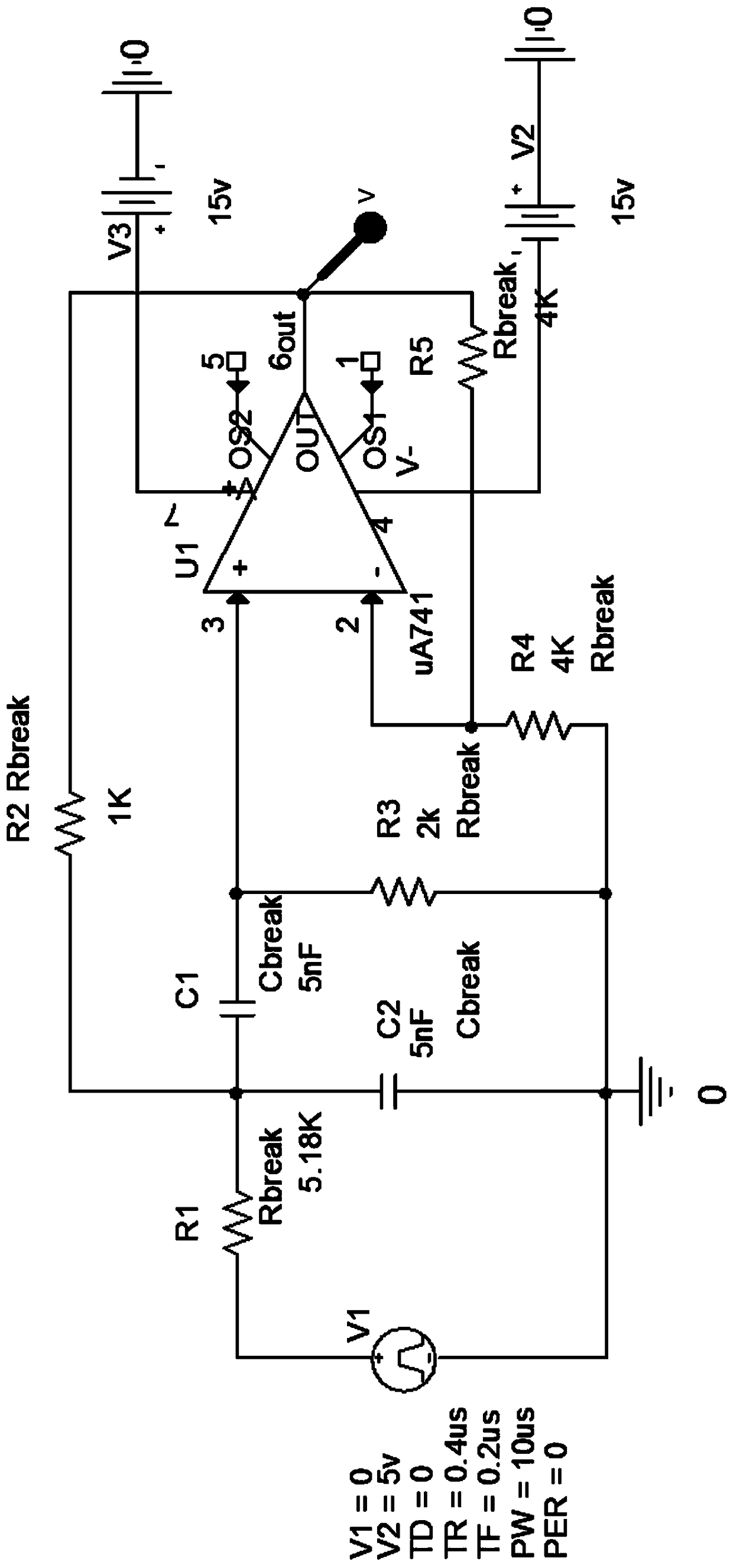

[0054] Such as image 3 As shown, the tested analog circuit is selected as a Sallen_Key band-pass filter with a center frequency of 25kHz. In order to explain the technical solution of the present invention in more detail, single and double fault situations of the circuit are considered. The parameter values of each component are their nominal values, and the allowable errors in the components are: the resistance tolerance range is ±5%X n , capacitance tolerance is ±10% x n , X n is the nominal value of the component, and the test stimulus is a single-cycle pulse signal with an amplitude of 5V and a pulse width of 10μs. Through the analysis of the sensitivity of the circuit, it can be known that the resistance R2, the resistance R3, the capacitance C1 and the capacitance C2 have the most significant influence on the output response of the circuit. Therefore, they are regarded as faulty component groups.

[0055] Single Fault Condition: When any component in a circuit is ...

Embodiment 2

[0066] Such as Figure 7 As shown, in order to verify the validity and universality of the scheme of the present invention, a relatively complex quadratic high-pass filter with four operational amplifiers in the circuit is used as the circuit under test. According to the sensitivity analysis, resistance R1, resistance R2, resistance R3, resistance R4 and capacitance C1, capacitance C2 have the most significant response to the circuit output, so they are taken as the fault element group. 100 Monte-Carlo analyzes are performed on each fault state of the circuit time-domain voltage signal, and 1000 sampling points are acquired each time within the first 400us of the test response. Other settings and diagnosis are the same as the circuit under test in Embodiment 1. Table 3 is the single fault mode, Table 4 is the double fault mode, NF is the normal state category, "—" indicates that the parameter does not exist, and k in Table 3 is kΩ.

[0067] Table 3 Single fault mode of quadr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More