Global Layout Optimization Method for Integrated Circuits Based on Generalized Augmented Lagrangian

A global layout and integrated circuit technology, applied in CAD circuit design, electrical digital data processing, instruments, etc., can solve the problem of slow speed of scattered units, achieve the effect of line length optimization, strong robustness, and guaranteed speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0013] The present invention will be further explained below with reference to the accompanying drawings and specific embodiments.

[0014] The present invention provides an integrated circuit global layout optimization method based on generalized augmented Lagrangian, which comprises the following steps:

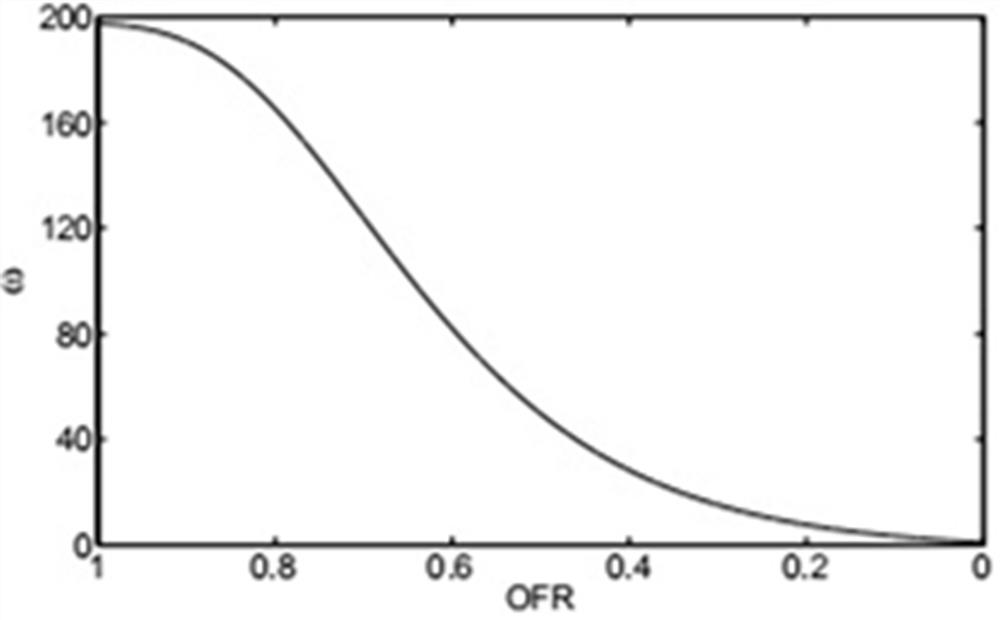

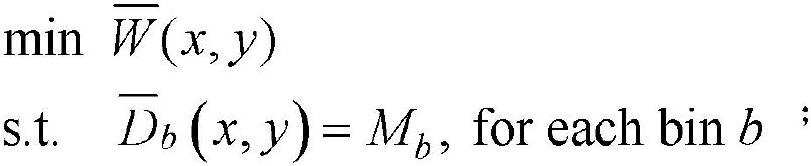

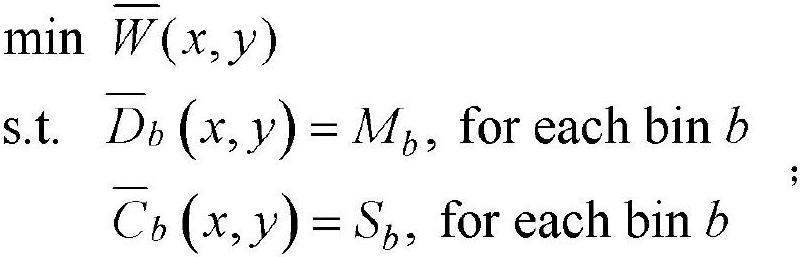

[0015] Step S1: represent the circuit as a hypergraph H={V, E}; each unit in the circuit is regarded as a vertex; each net is regarded as a hyperedge; where V={v 1 , v 2 ,...,v n } is the set of n units; E={e 1 , e 2 ,...,e m } is a set of m nets; n, m are natural numbers; step S2: provide a generalized augmented Lagrangian method, and use it to solve the VLSI global layout problem; step S3: prove the generalized augmentation proposed in step S2 The Lagrangian method is globally convergent for the global layout problem; Step S4: apply the generalized augmented Lagrangian method to deal with the global layout problem with line network congestion degree constraints.

[...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More