Clock generation device based on phase-locked loop and standard ruler delay line and implementation method thereof

A technology of clock generation and implementation method, applied in the direction of automatic power control, electrical components, etc., to achieve the effects of high stability, light weight and small size

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment approach 1

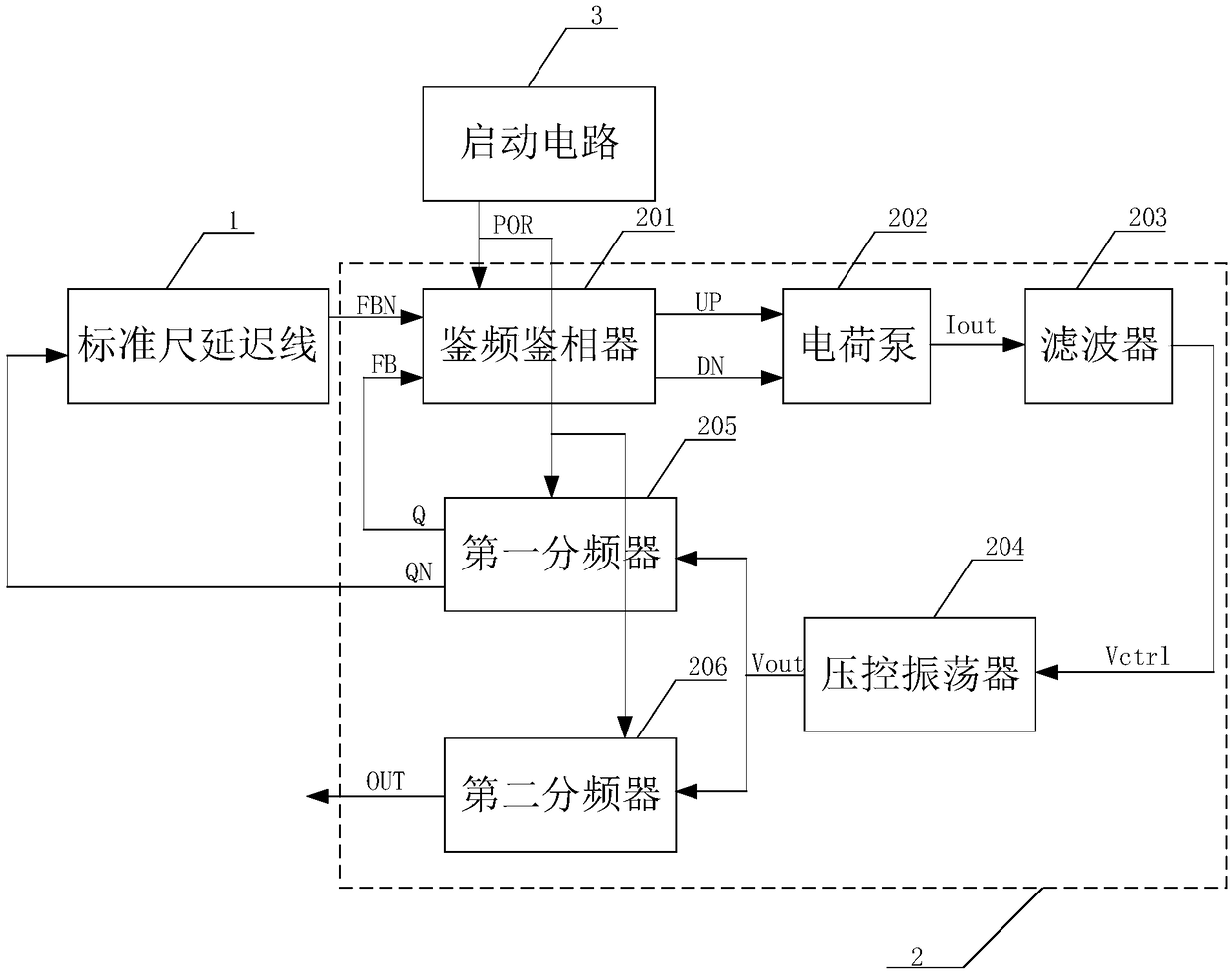

[0034] Specific implementation mode one: the following combination figure 2 Describe this embodiment mode, the clock generation device based on phase-locked loop and standard scale delay line described in this embodiment mode, this clock generation device comprises standard scale delay line 1 and phase-locked loop 2; Phase-locked loop 2 comprises frequency discriminator phase detector 201, charge pump 202, filter 203, voltage controlled oscillator 204, first frequency divider 205 and second frequency divider 206;

[0035] The UP output end and the DN output end of the frequency discrimination phase detector 201 are respectively connected to the UP input end and the DN input end of the charge pump 202, and the current output end I of the charge pump 202 out Connect the current input terminal of the filter 203, the output terminal V of the filter 203 ctrl Connect the input end of the voltage-controlled oscillator 204, the clock signal output end Vout of the voltage-controlled ...

specific Embodiment approach 2

[0036] Specific implementation mode two: the following combination figure 2 Describe this embodiment mode, this embodiment mode will further explain Embodiment 1, the clock generating device also includes a start-up circuit 3;

[0037] The reset output terminal of the start-up circuit 3 is simultaneously connected to the reset input terminal of the frequency and phase detector 201 , the reset input terminal of the first frequency divider 205 and the reset input terminal of the second frequency divider 206 .

[0038] In this embodiment, the initial states of the frequency and phase detector 201 , the first frequency divider 205 and the second frequency divider 206 are very important, and the startup circuit 3 is used to ensure that the initial states are correct.

specific Embodiment approach 3

[0039] Embodiment 3: In this embodiment, Embodiment 1 is further described. The first frequency divider 205 is a frequency divider in a loop, and the Q output terminal and the QN output terminal of the first frequency divider 205 are symmetrical.

[0040] In this embodiment, the first frequency divider 205 is used as a frequency divider in the loop, and a two-way frequency divider is used. The two outputs Q and QN must have a high degree of symmetry, that is, the QN signal is not simply in the Q signal. Then connect an inverter to get it. In the present invention, the two-frequency divider is composed of eight three-input NAND gates plus an inverter.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More