Dynamic comparator offset voltage calibration method

A technology of dynamic comparator and offset voltage, applied in energy-saving methods, instruments, electrical components, etc., can solve the problems of performance degradation, small quantization range of SARADC, etc., and achieve the effect of high calibration accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0018] Below in conjunction with accompanying drawing and specific embodiment, the present invention is described in detail:

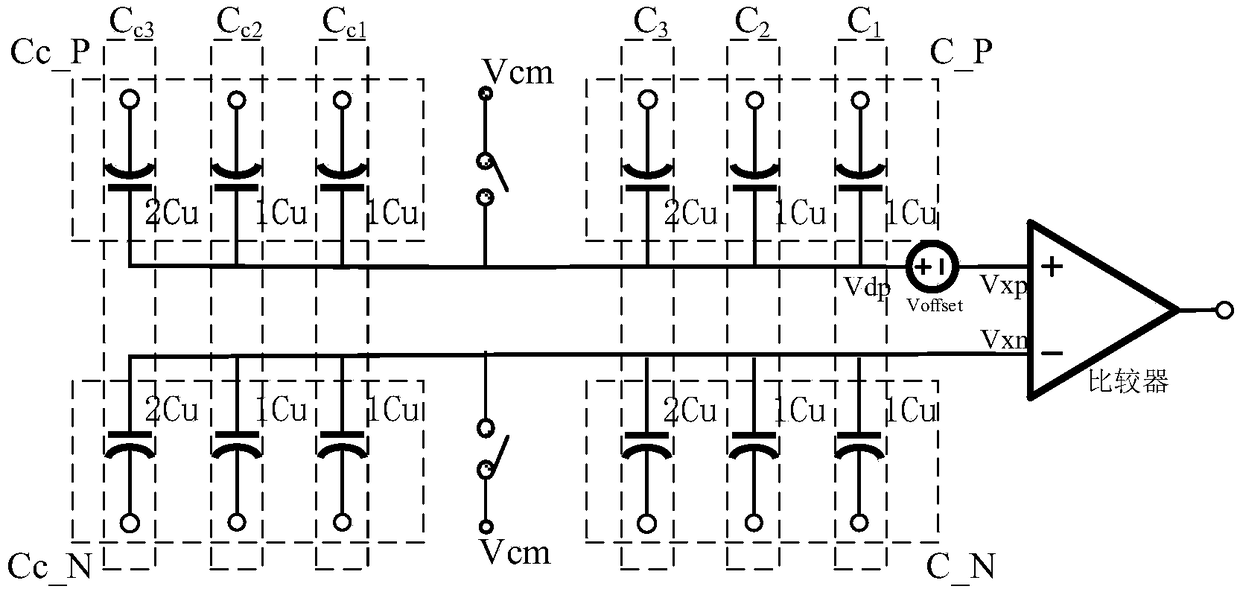

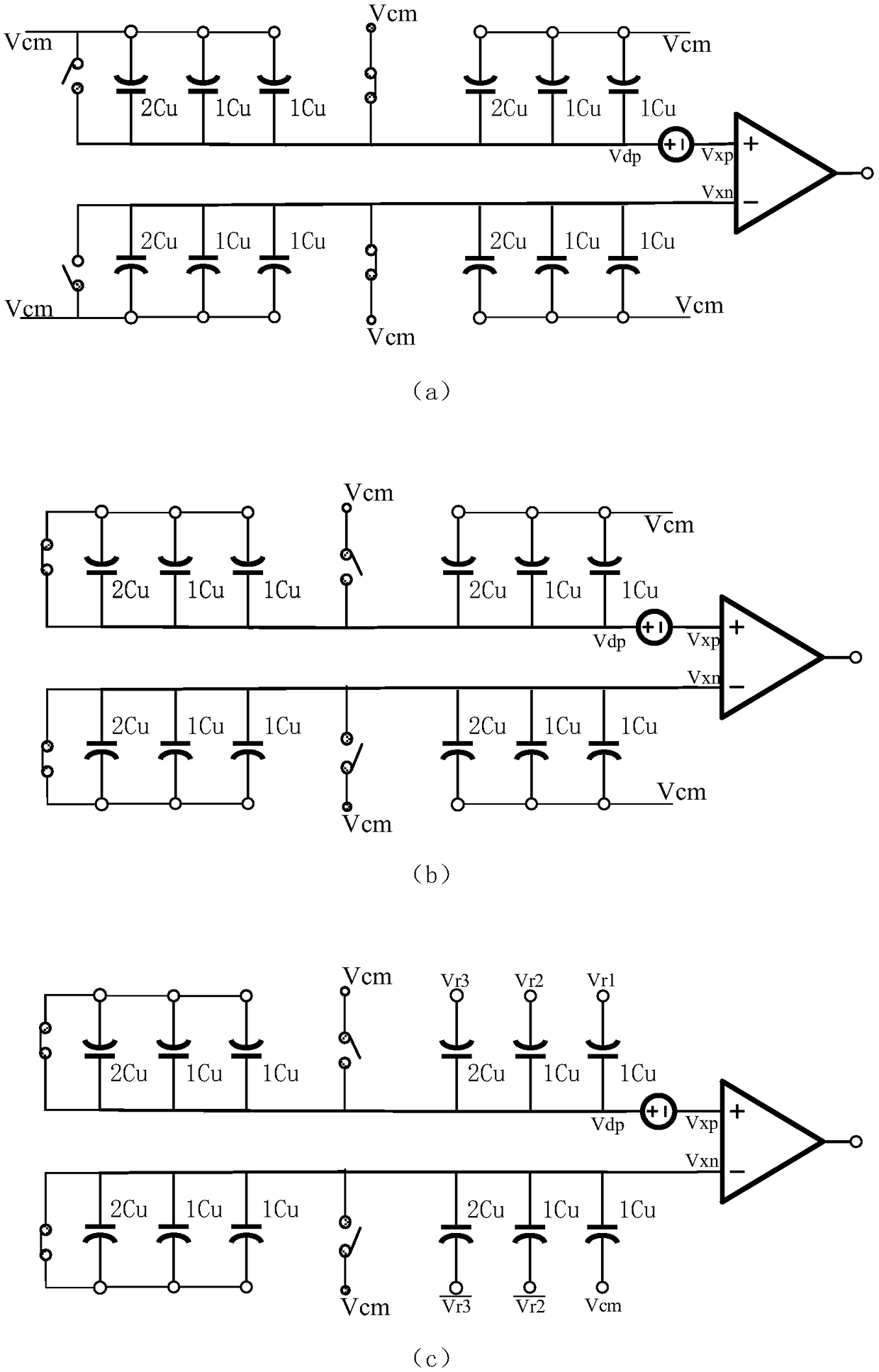

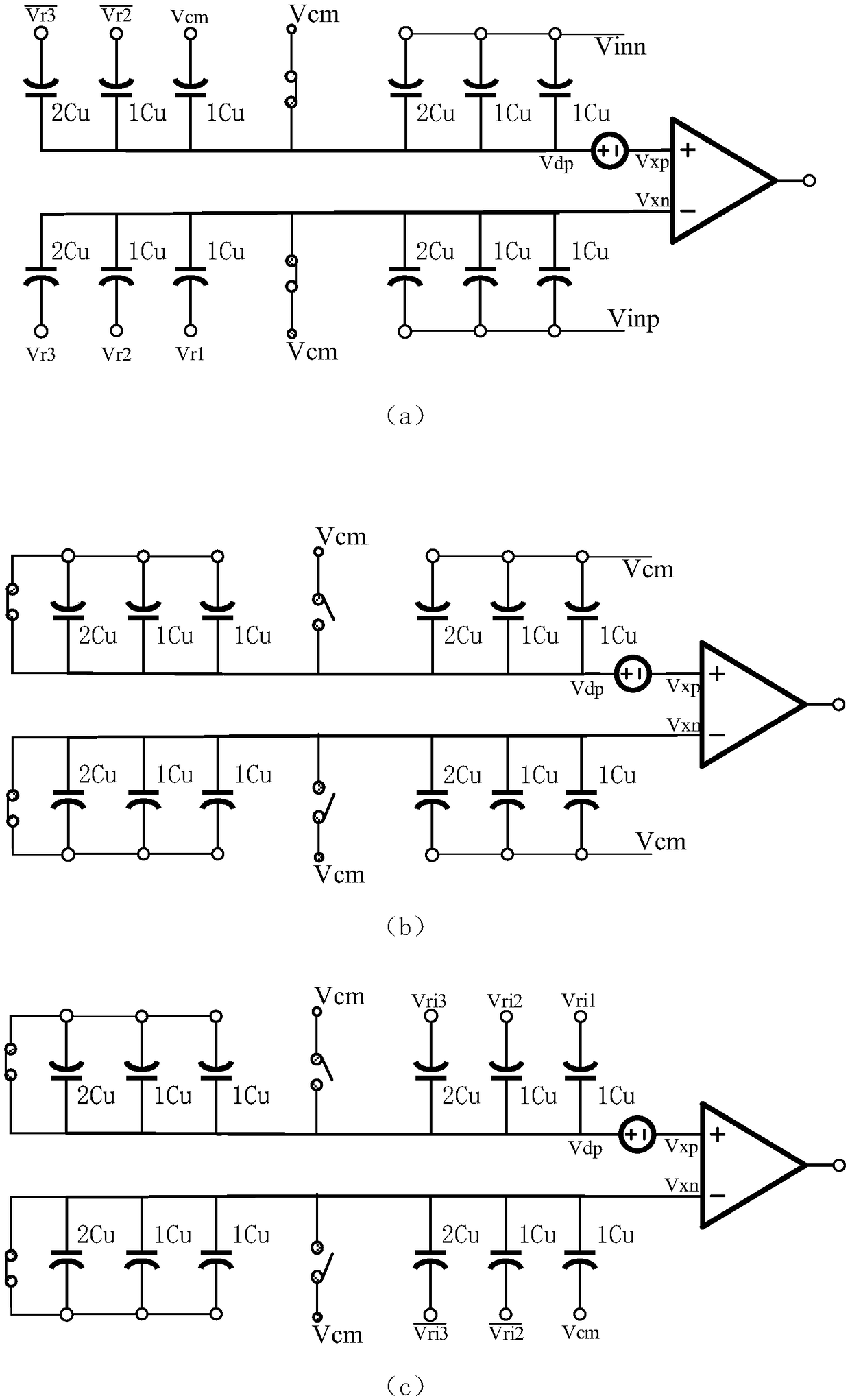

[0019] The present invention is applicable to the successive approximation analog-to-digital converter in the sampling form of the lower plate, and realizes comparator misadjustment by setting a calibrating capacitor array cCDAC with the same structure as the quantization capacitor array CDAC in the digital-to-analog converter of the successive approximation analog-to-digital converter voltage calibration, such as figure 1 Shown is a circuit structure of a digital-to-analog converter for successive approximation to analog-to-digital converters. The upper plate of the capacitor in the quantized capacitor array CDAC is connected to one of the input terminals of the comparator, and the lower plate is connected to the reference voltage and common mode through a switch. voltage, input voltage or ground voltage; the calibration capacitor array cCDAC is the s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More