Method for evaluating wafer and method for manufacturing epitaxial wafer

A technology for evaluating methods and manufacturing methods, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

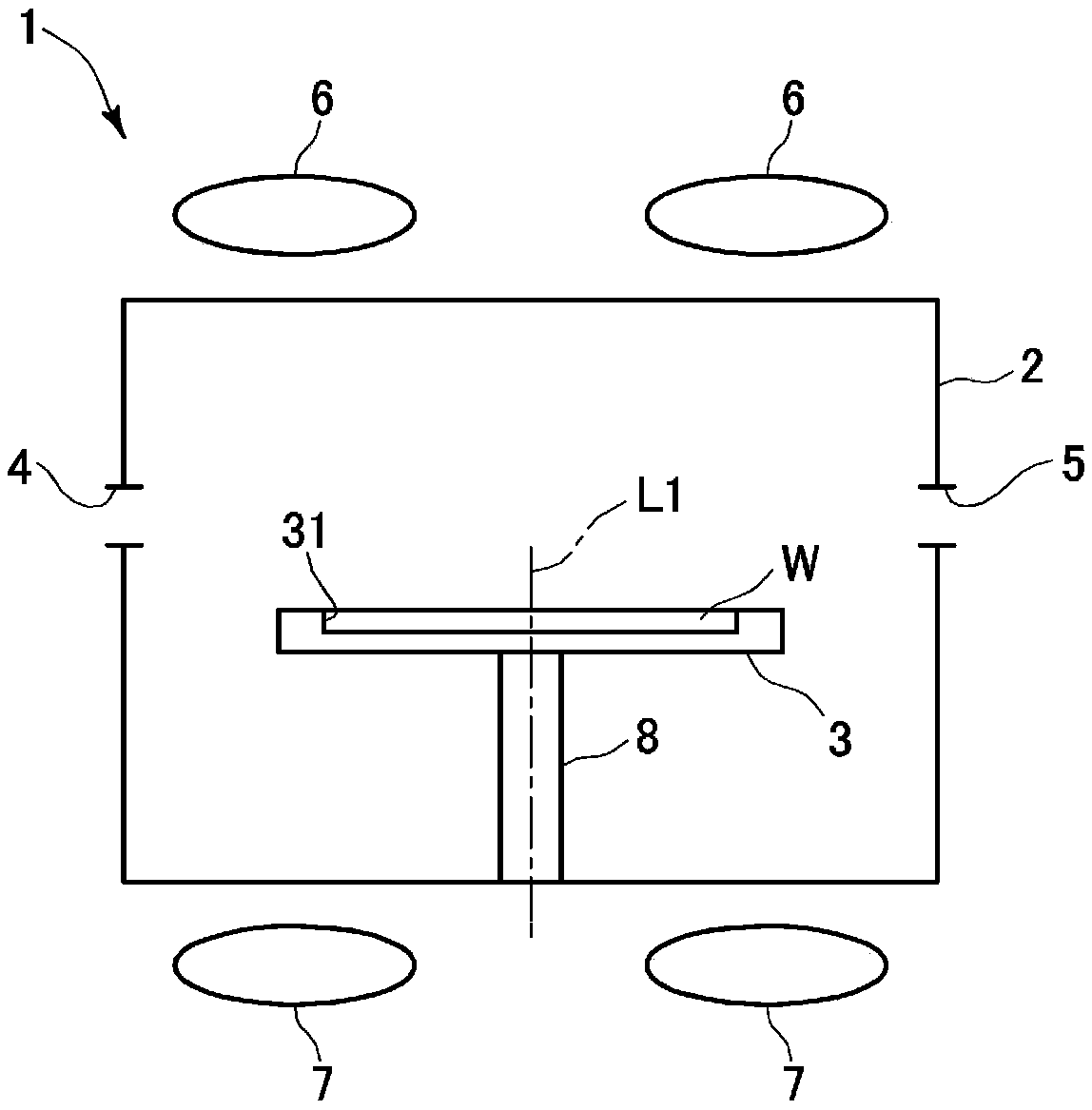

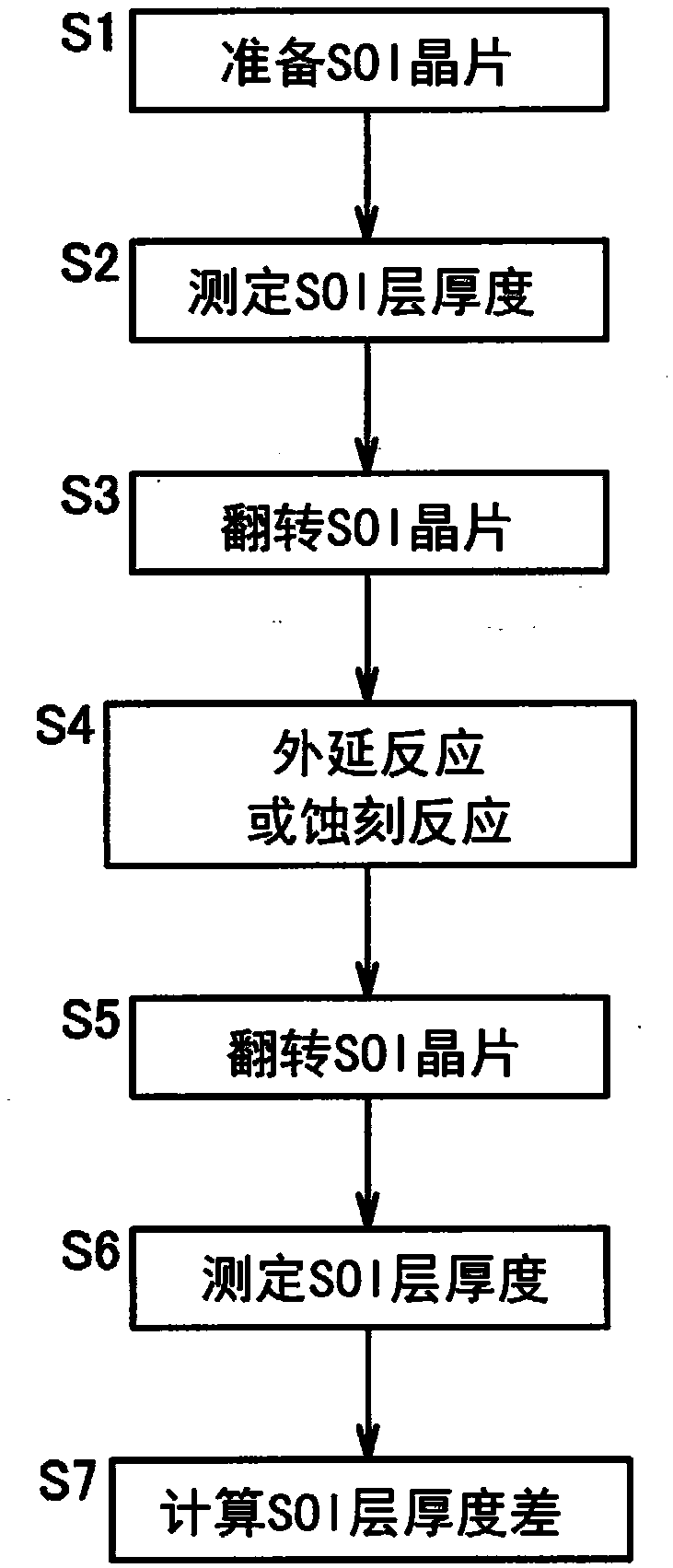

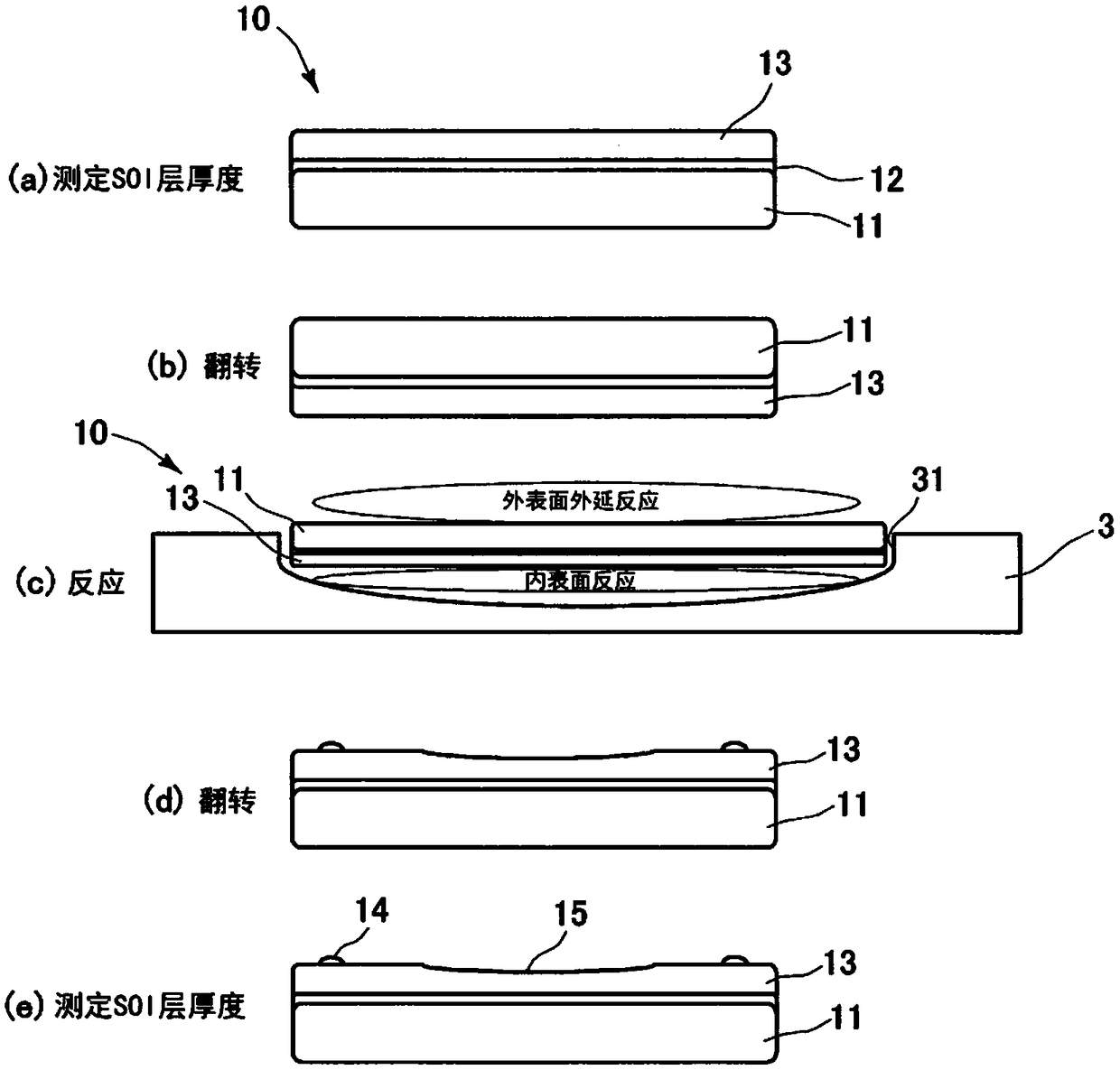

[0055] adopted with figure 1 The same epitaxial growth setup, according to figure 2 In the step of , the inner surface distribution of the deposited amount or the etched amount of the wafer inner surface (SOI layer) is obtained. At this time, in the step S4, the silicon source gas supplied to the SOI wafer is DCS (dichlorosilane) gas, so that the deposition reaction (epitaxy reaction) mainly proceeds on the outer surface of the silicon substrate of the SOI wafer. In addition, on multiple SOI wafers, one at a time figure 2 At this time, for different SOI wafers, the power ratios of the upper lamp and the upper lamp in the process of S4 are made different.

[0056] The in-plane distribution of the deposition amount or etching amount of the inner surface (SOI layer) of each SOI wafer is as follows: Figure 4 shown. Figure 4 It shows that the ratio of the power of the lower lamp to the total power of the upper lamp and the lower lamp is 47% (Lwr47), 51% (Lwr51), 55% (Lwr55)...

Embodiment 2

[0061] adopted with figure 1 The same epitaxial growth setup, according to figure 2 The in-plane distribution of the amount of deposition or etching on the inner surface of the wafer (SOI layer) is obtained. At this time, in the step S4, HCl gas is supplied to the outer surface of the SOI wafer, so that the etching reaction mainly proceeds on the outer surface of the silicon substrate of the SOI wafer. Reaction conditions (flow rate of HCl gas, etc.) were set such that the etching amount of the outer surface of the silicon substrate was 0.5 μm. In addition, a base having a plurality of dimples on the bottom surface of the base recess is prepared. Next, using this susceptor, HCl gas is supplied to the outer surface of the SOI wafer to cause a reaction.

[0062] When HCl gas is supplied to the outer surface of the SOI wafer, the in-plane distribution of the deposition amount or the etching amount of the inner surface (SOI layer) of the SOI wafer is as follows: Figure 5 , ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More