A chip package structure and method

A technology of chip packaging structure and shielding structure, which is applied in the electronic field, can solve problems such as unreliable chip safety performance and system shutdown, and achieve the effects of improving use safety, improving heat dissipation performance, and ensuring work stability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0022] In view of the deficiencies in the prior art, the inventor of this case was able to propose the technical solution of the present invention after long-term research and extensive practice. The technical solution, its implementation process and principle will be further explained as follows.

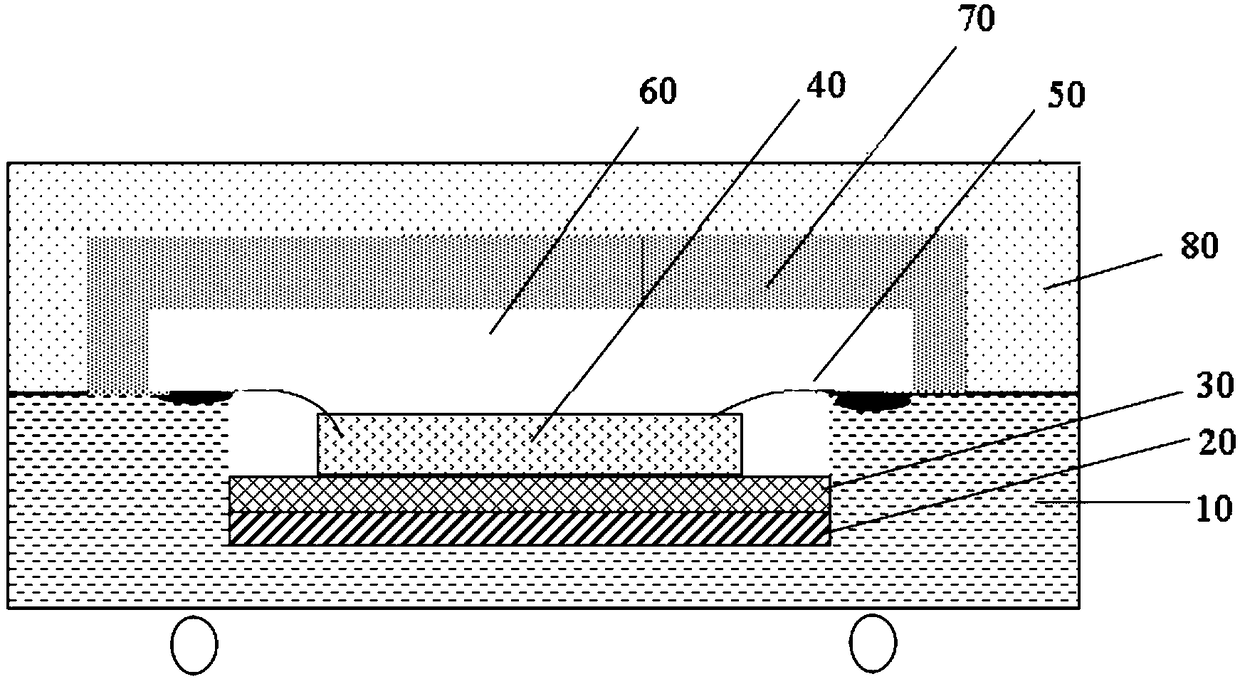

[0023] A chip packaging structure provided by an embodiment of the present invention includes:

[0024] Substrate;

[0025] a heat dissipation layer arranged on one side surface of the substrate;

[0026] a wafer, disposed on a side of the heat dissipation layer away from the substrate;

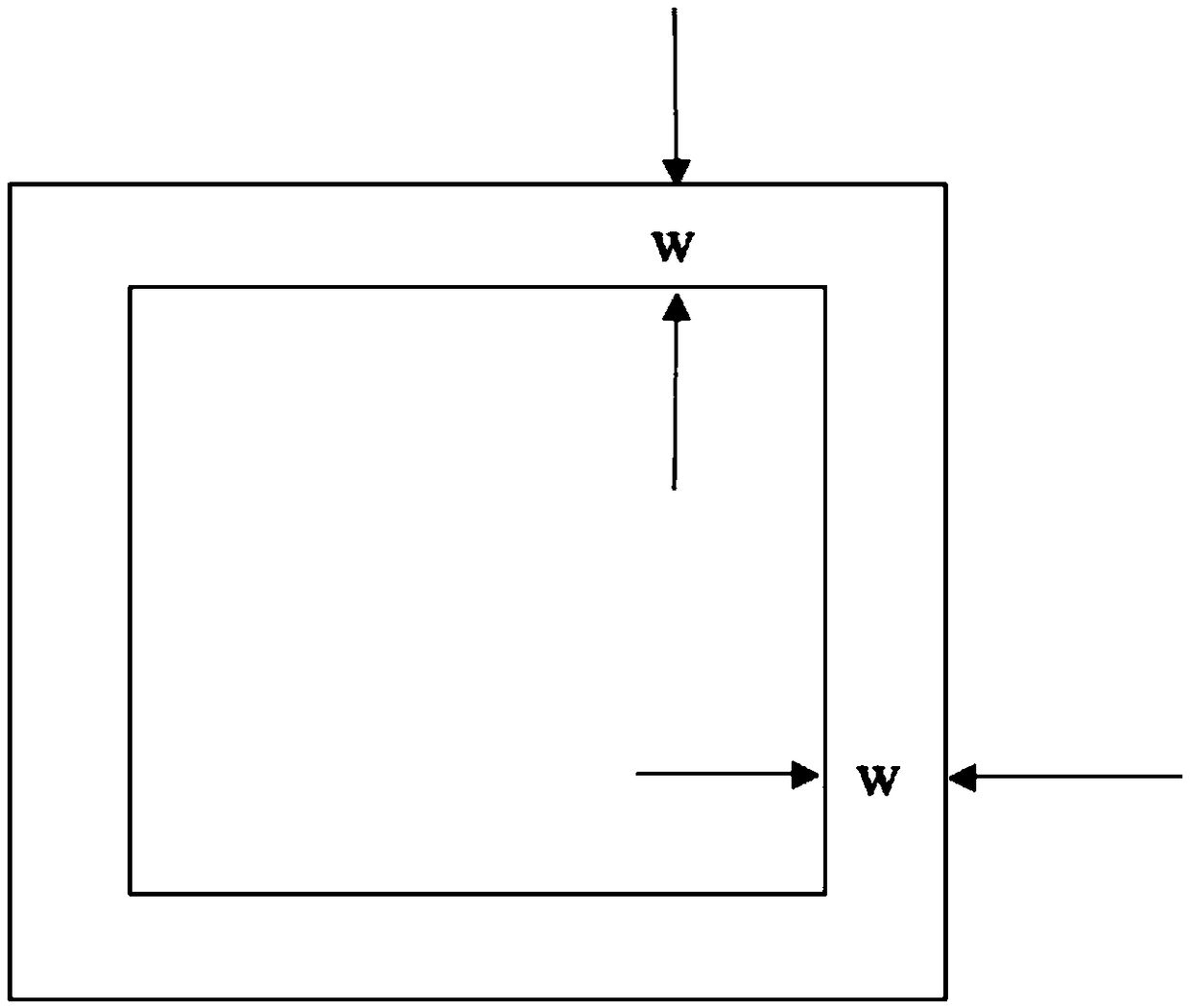

[0027] The shielding structure is fixedly installed on the substrate and covers the periphery of the wafer, and a cavity is formed between the shielding structure and the wafer.

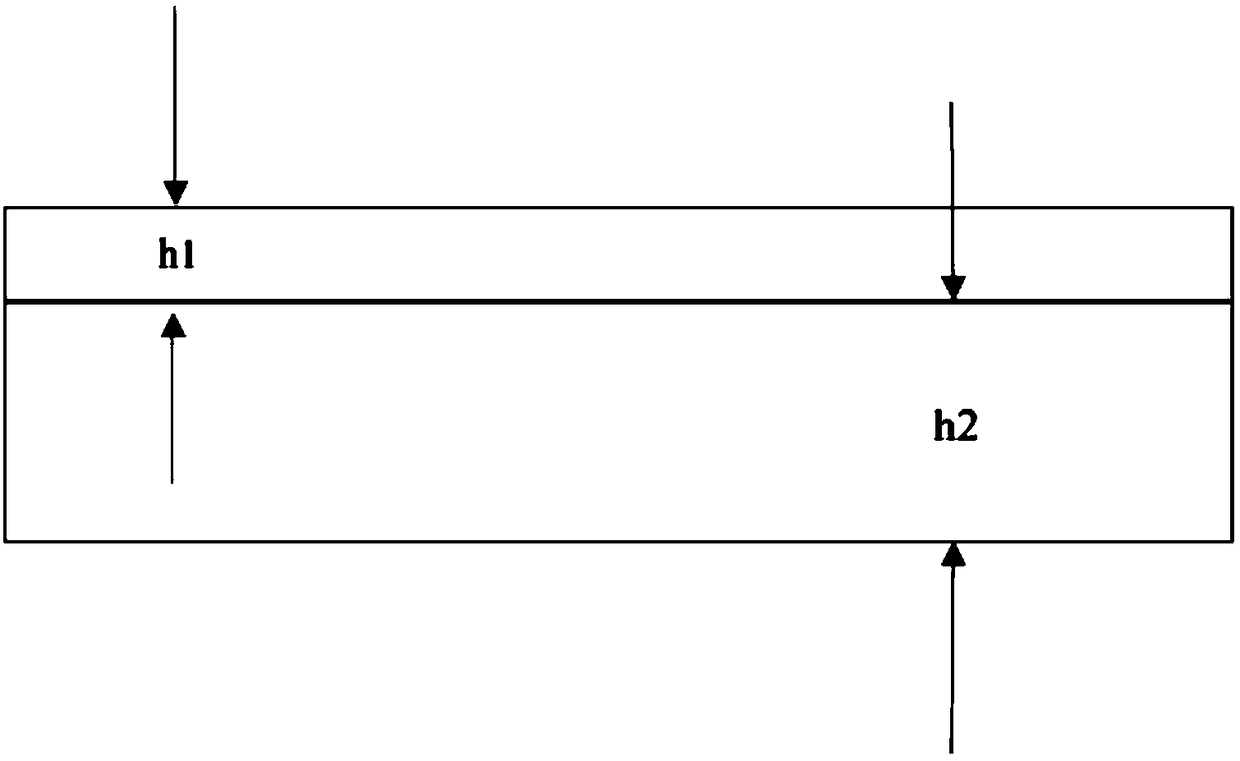

[0028] In some embodiments, the heat dissipation layer includes a heat conduction layer and an adhesive layer, and the wafer is connected to the heat conduction layer through the adhesive layer.

[0029] In some pref...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com