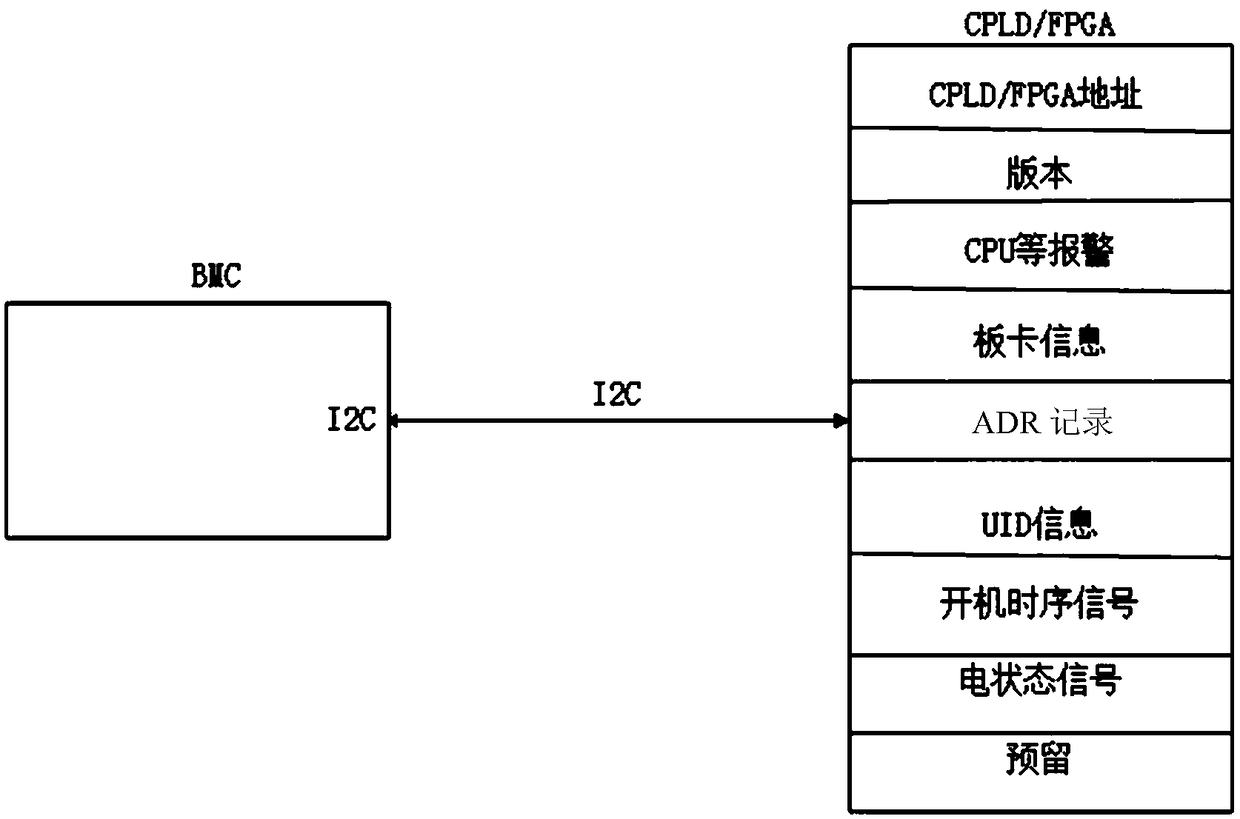

A CPLD/FPGA register control method and system

A control method and register technology, applied in the computer field, can solve problems such as increased production costs, large logic resources, consumption, etc., and achieve the effects of perfect management and increased production costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

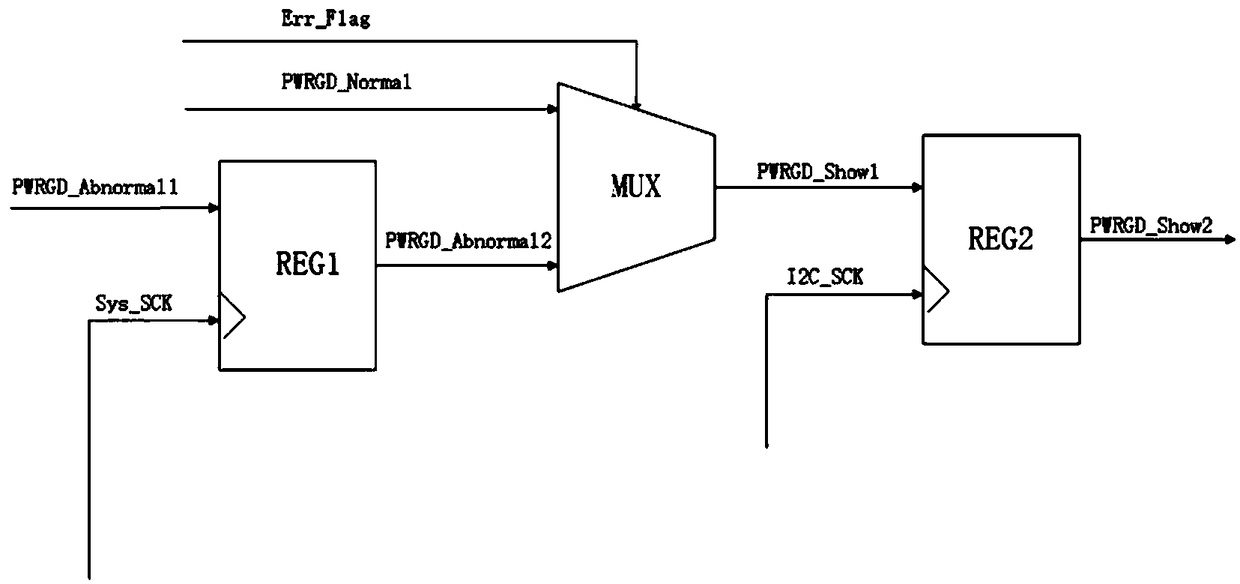

Method used

Image

Examples

Embodiment Construction

[0026] Embodiments of the present disclosure are described below. It is to be understood, however, that the disclosed embodiments are merely examples and that other embodiments may take various alternative forms. The figures are not necessarily to scale; some features may be exaggerated or minimized to show details of particular components. Therefore, specific structural and functional details disclosed herein are not to be interpreted as limiting, but merely as a representative basis for teaching one skilled in the art to variously employ the present invention. As will be understood by persons of ordinary skill in the art, various features shown and described with reference to any one figure can be combined with features shown in one or more other figures to create embodiments not explicitly shown or described . Combinations of features shown provide representative embodiments for typical applications. However, various combinations and modifications of the features consist...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com