Protection method for a processor instruction Cache single event upset soft error

A single-event flipping and processor instruction technology, applied in the aerospace field, can solve problems such as program flow soft errors, just in its infancy, processor application problems, etc., and achieve the effect of saving development costs and wide applicability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

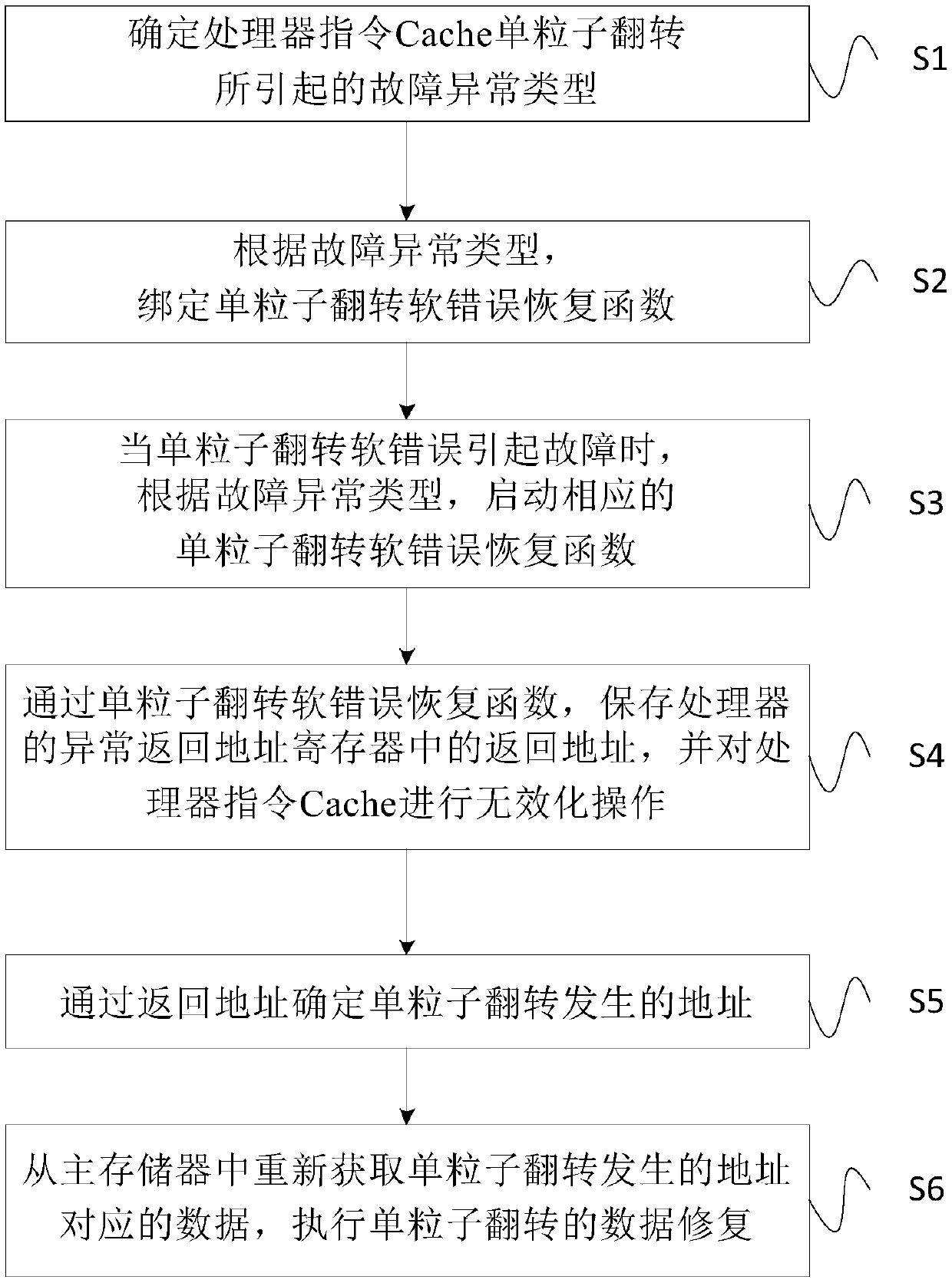

Method used

Image

Examples

Embodiment Construction

[0032] The present invention will be described in detail below in conjunction with specific embodiments. The following examples will help those skilled in the art to further understand the present invention, but do not limit the present invention in any form. It should be noted that those skilled in the art can make several changes and improvements without departing from the concept of the present invention. These all belong to the protection scope of the present invention.

[0033] In order to solve the problem of program soft errors caused by on-orbit single-event flips encountered in the application of high-performance processors in on-board computers, the present invention provides a protection method for processor instruction Cache single-event flip soft errors. The technical solution of the present invention will be described in detail below with specific embodiments in conjunction with the high-performance processor PPC750 instruction Cache single event flip soft error...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com