An SOC chip system-level verification system and an SOC chip system-level verification method

A chip system and verification system technology, applied in CAD circuit design, special data processing applications, instruments, etc., can solve the problems of insufficient flexibility and low verification efficiency, simplify the work of maintaining code, speed up rapid convergence, and improve the overall The effect of work efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

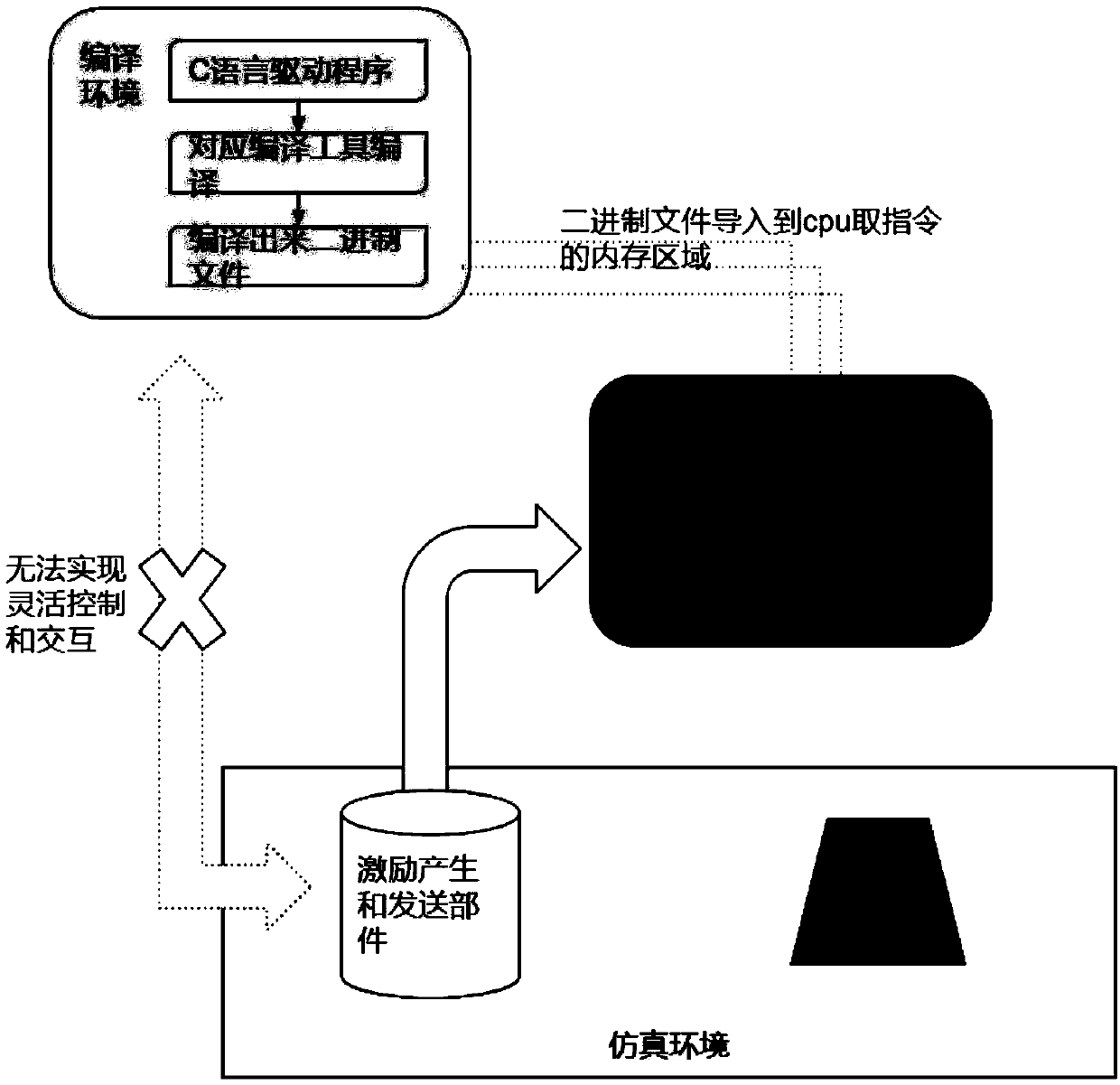

Problems solved by technology

Method used

Image

Examples

Embodiment 1

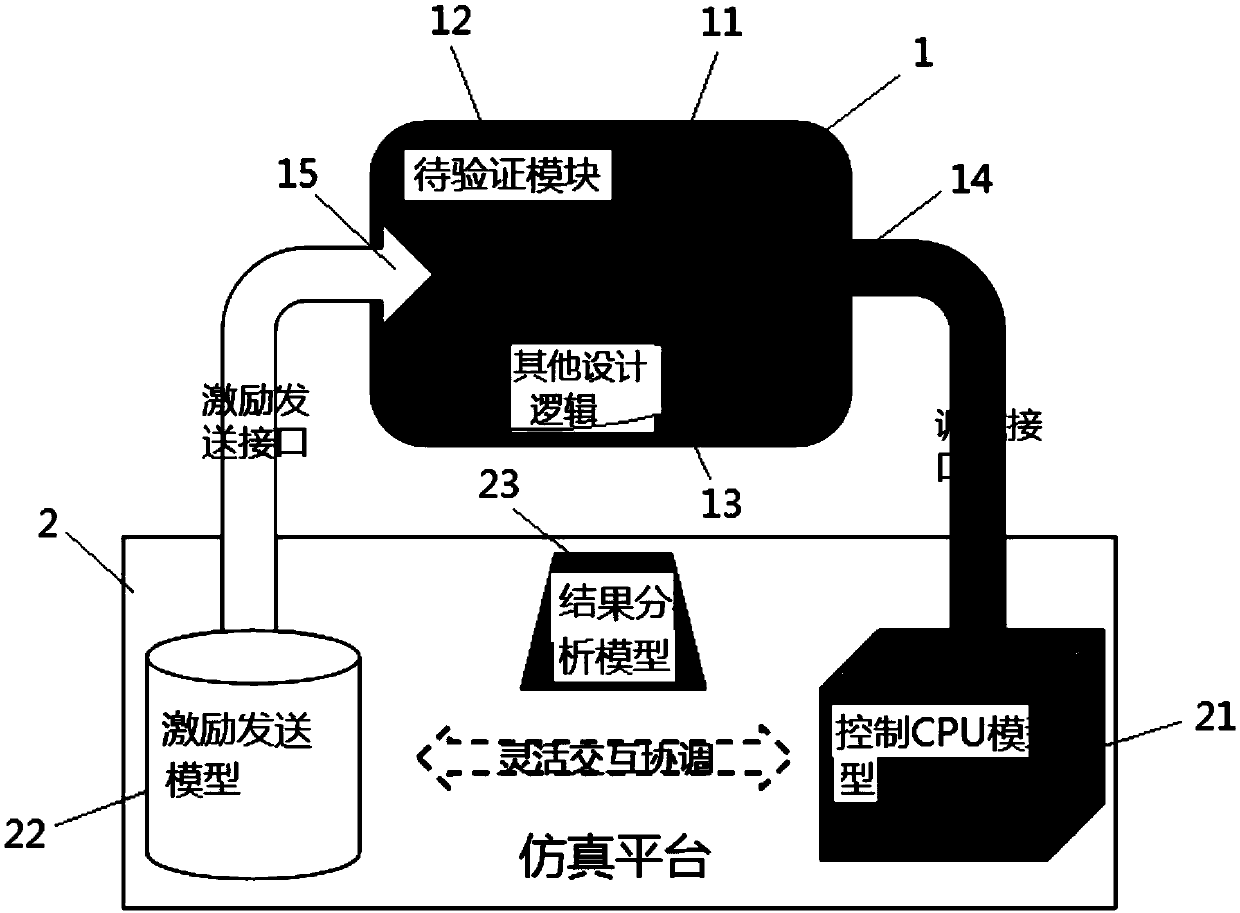

[0036] Please refer to figure 2 , the present invention provides a SOC chip system-level verification system, including a SOC chip 1 and a simulation platform 2;

[0037] The SOC chip 1 includes a CPU 11, a debugging interface 14 connected to the CPU 11, a module to be verified 12, and an excitation sending interface 15 connected to the module 12 to be verified by other design logic 13;

[0038] Described emulation platform 2 comprises control CPU model 21, incentive sending model 22 and result analysis model 23; Wherein:

[0039] The control CPU model 21 is connected with the module 12 to be verified by the debugging interface 14 according to the interface protocol; when the verification starts, receive the indication signal of the verification start and control the CPU11 to enter the debugging mode, and receive the verification end indication signal when the verification ends and Controlling the CPU 11 to exit the debugging mode, the CPU 11 acts in accordance with the inst...

Embodiment 2

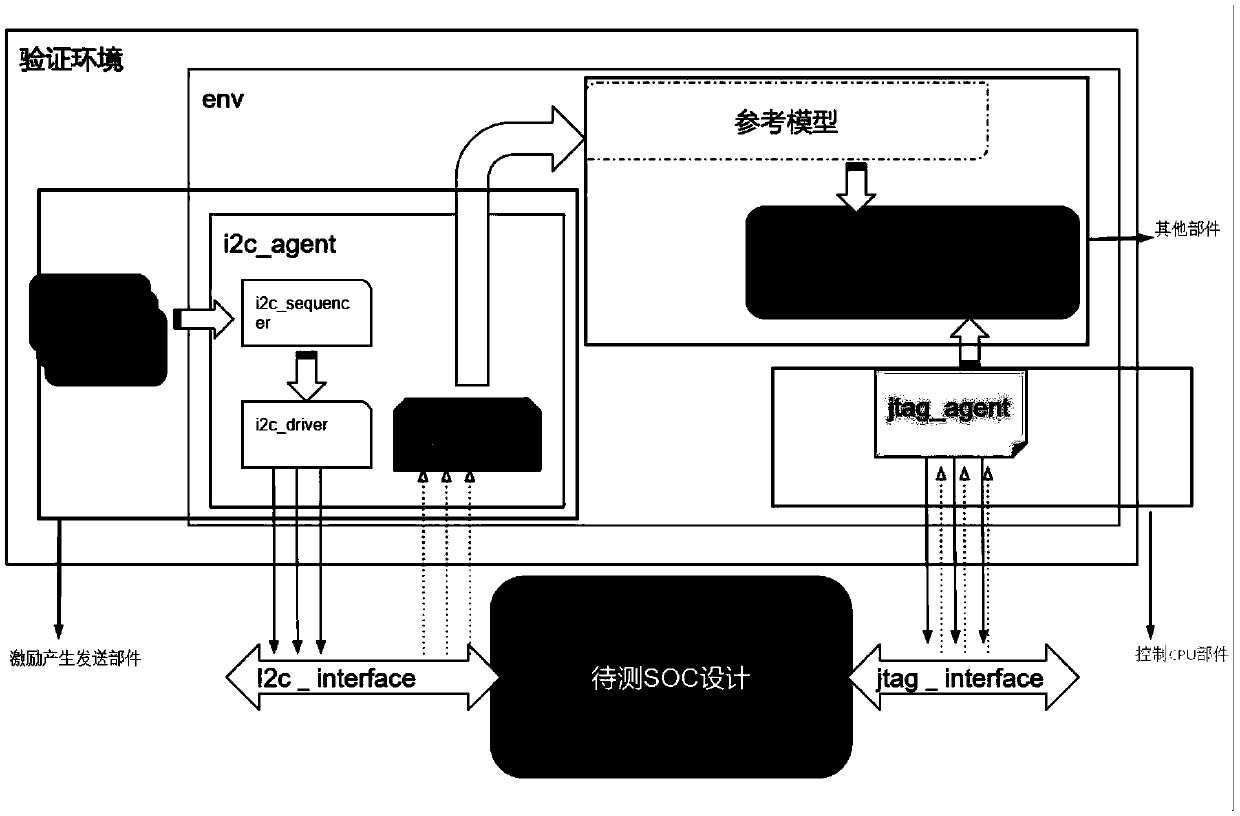

[0051] Please refer to image 3 , for the concrete realization that this invention is applied to the application of I2C interface:

[0052] The verification environment mainly includes:

[0053] 1. The stimulus generating and sending component (stimulus sending model 22) is mainly connected to the corresponding pins of the SOC design (SOC chip 1) to be tested through the I2c_interface according to the I2C interface protocol, and the components of the test design can be sampled at the same time. Respond or return data.

[0054] 2. The control CPU component (control CPU model 21) is mainly connected to the corresponding controller of the SOC design to be tested through jtag_interface according to the jtag interface protocol, and the CPU enters the debug mode by accessing the cpu register. In this mode, the CPU enters the halt (pause) state, the behavior of the CPU is completely taken over by jtag.

[0055] 3. Other components (result analysis model 23) are mainly used for aut...

Embodiment 3

[0059] The embodiment of the present invention also provides a SOC chip system-level verification simulation platform, including the simulation platform in the SOC chip system-level verification system of any embodiment.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More