SPI verification method based on UVM verification methodology

A verification methodology and verification method technology, applied in the field of SPI verification based on UVM verification

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

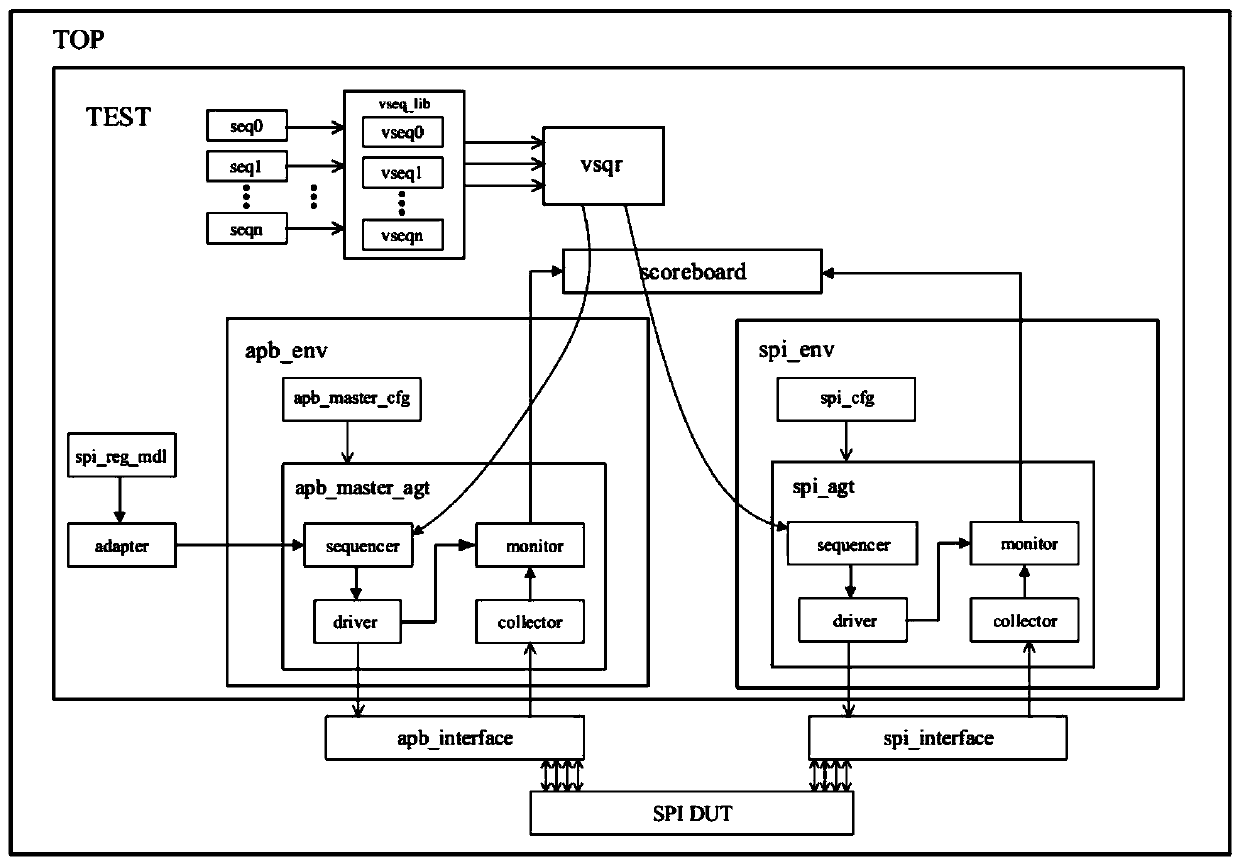

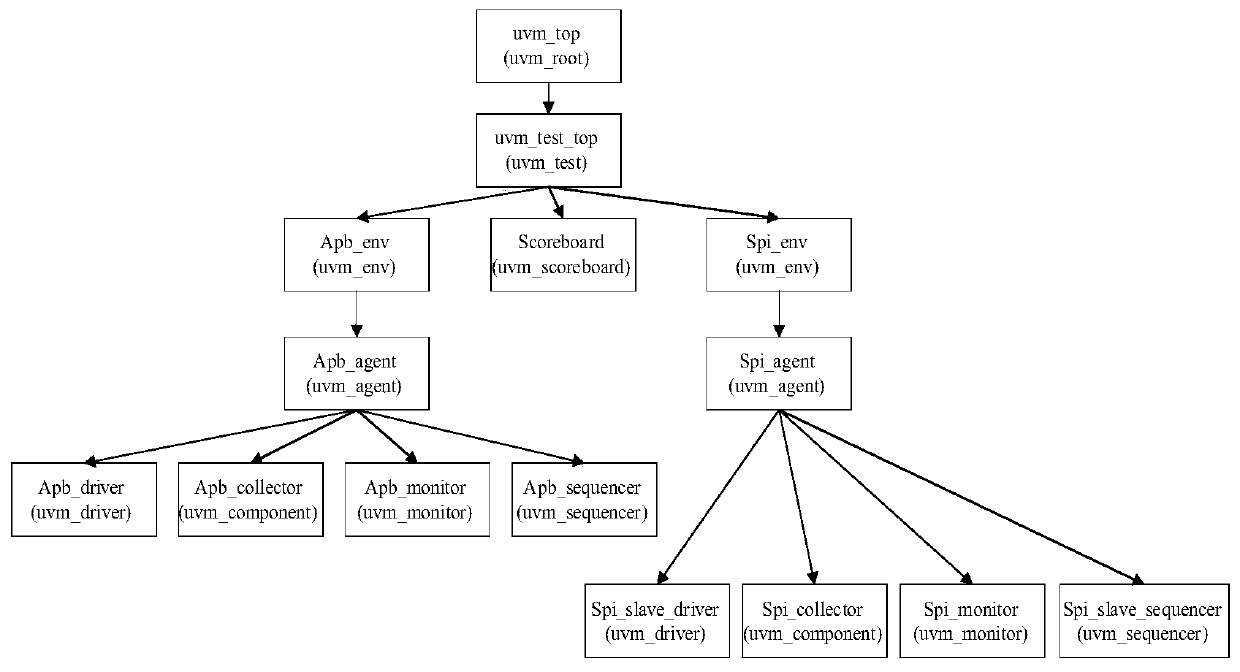

[0028] The architecture of the verification platform of the present invention is as follows: figure 1 As shown, the entire verification platform mainly includes the following parts: APB bus system apb_env, SPI bus system spi_env, SPI register model spi_reg_mdl, scoreboard scoreboard, both APB and SPI systems contain a configuration component and a proxy component, and the proxy component consists of It consists of stimulus generator, driver, collector, and monitor. The above are the main components of the verification platform. In addition to instantiating the above components in the TEST layer, a sequence is also added.

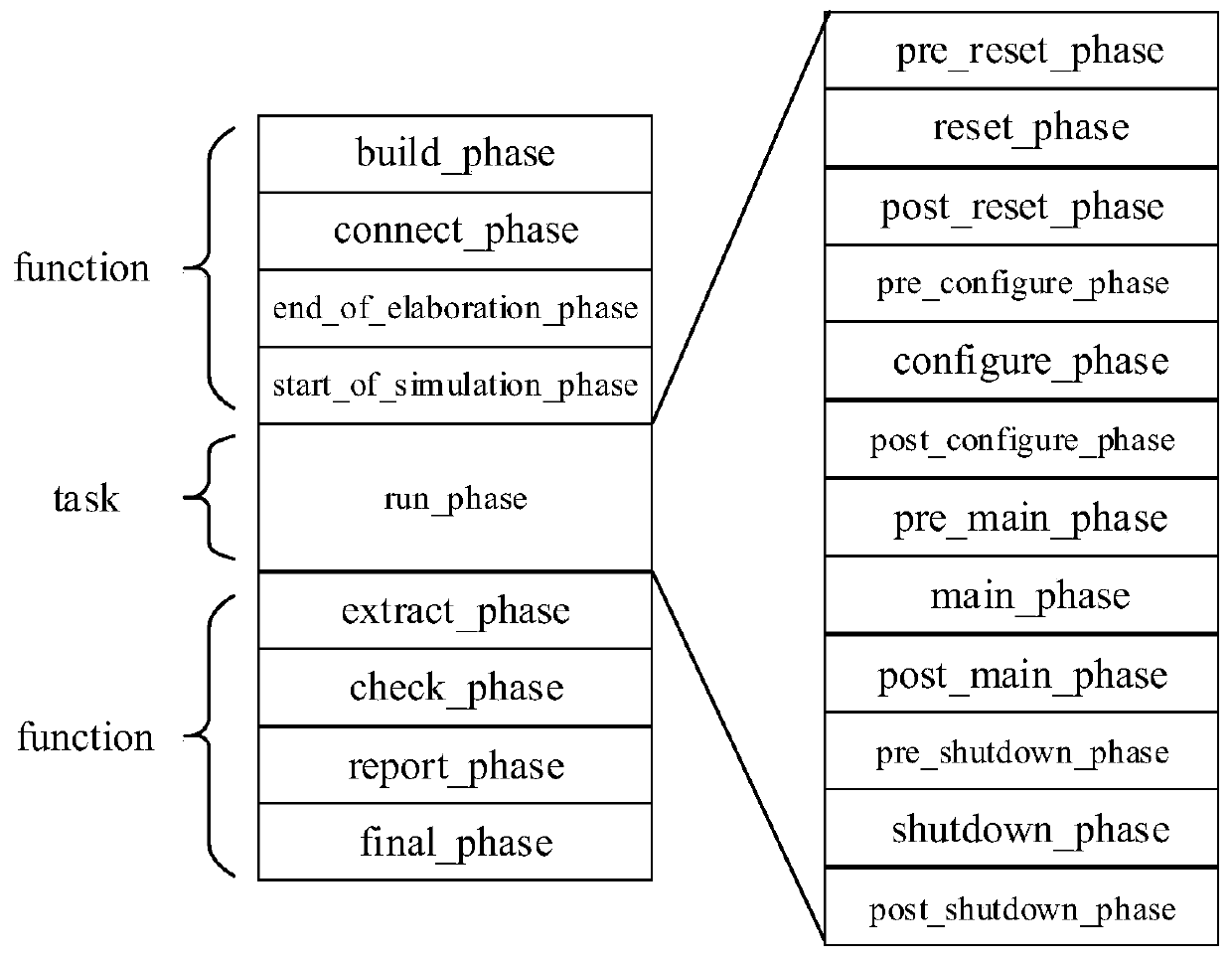

[0029] The sequences in the test cases are all scheduled in the virtual sequence through the `uvm_do_on() task, and vsqr sends the data packets generated by each sequence to the specified sequencer. According to the requirements of each test, build a different virtual sequence and add it to vseq_lib. The raise_objection and drop_objection of main_phase are e...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More