Patents

Literature

72results about How to "Verified and reliable" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

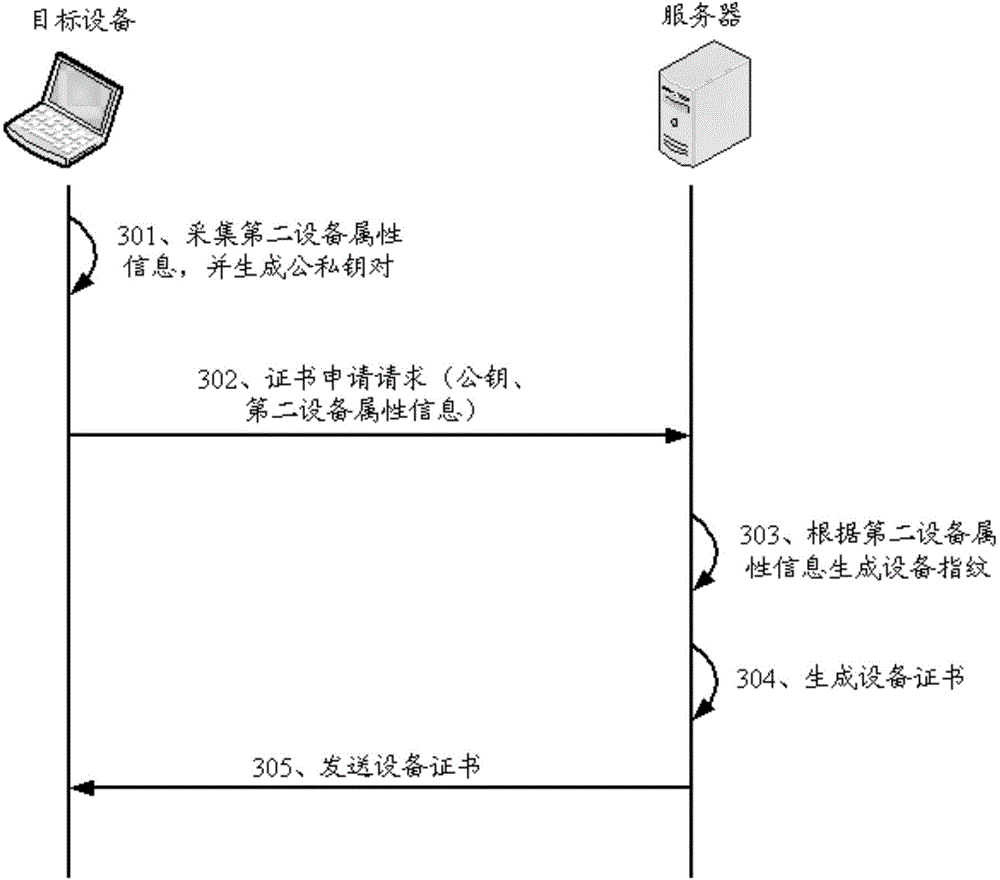

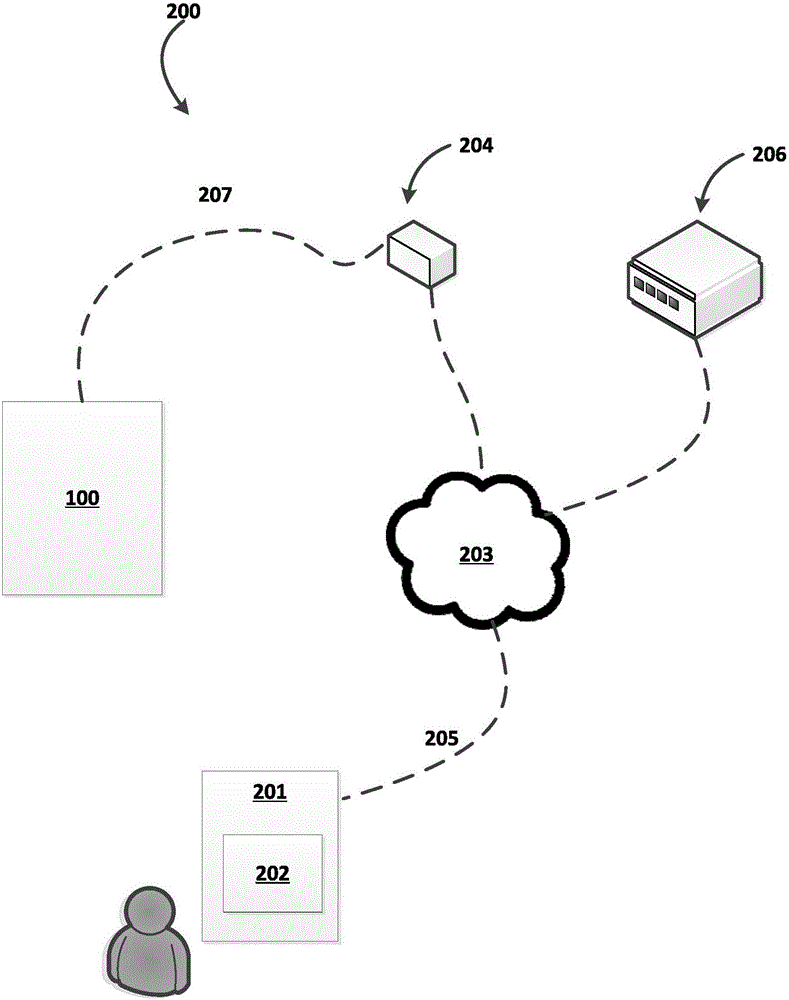

Equipment verification method and device

ActiveCN105763521AEfficient identificationVerified and reliablePlatform integrity maintainanceSecuring communicationDevice PropertiesValidation methods

The invention provides an equipment verification method and device. The equipment verification method is used for verifying target equipment requesting to perform target service. The method includes receiving an equipment verification request sent by to-be-verified target equipment, wherein the equipment verification request includes an equipment certificate and first equipment attribute information of the target equipment and the equipment certificate includes an equipment fingerprint generated according to second equipment attribute information; determining the equipment certificate is the certificate of the target equipment and allowing the target equipment to perform the target service when the equipment fingerprint confirms that the equipment certificate is valid and the equipment fingerprint matches with the first equipment attribute information. The invention improves equipment verification reliability.

Owner:ADVANCED NEW TECH CO LTD

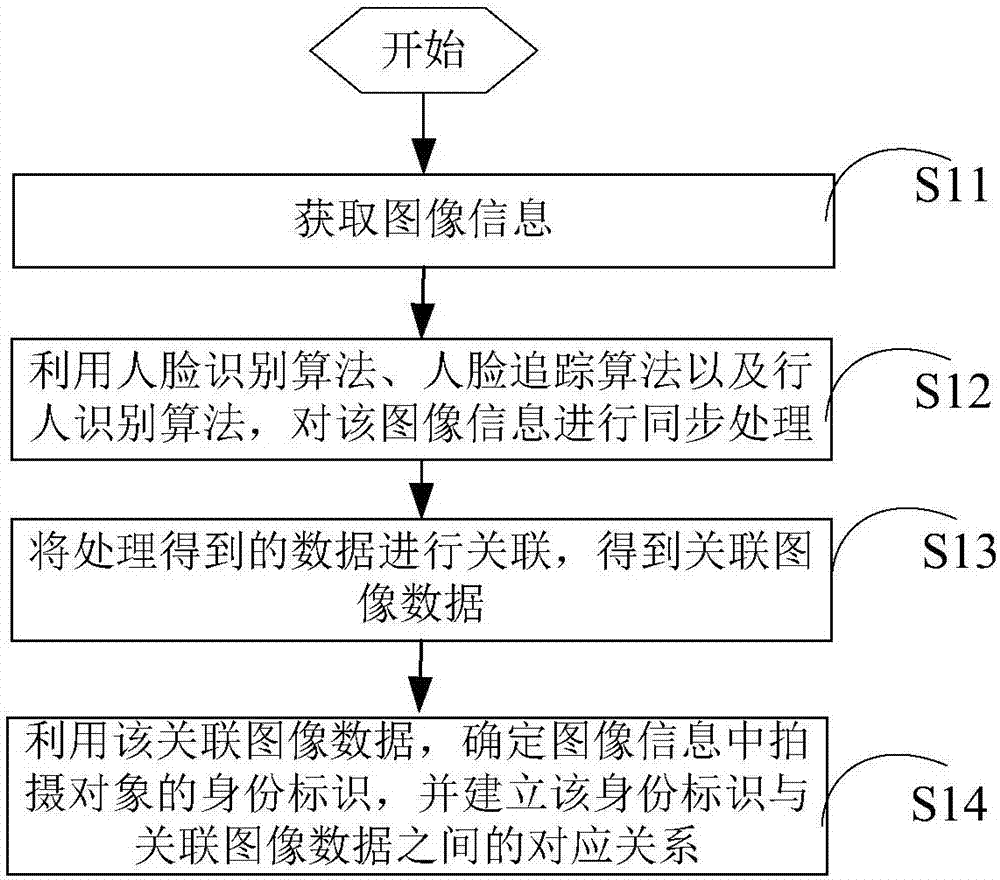

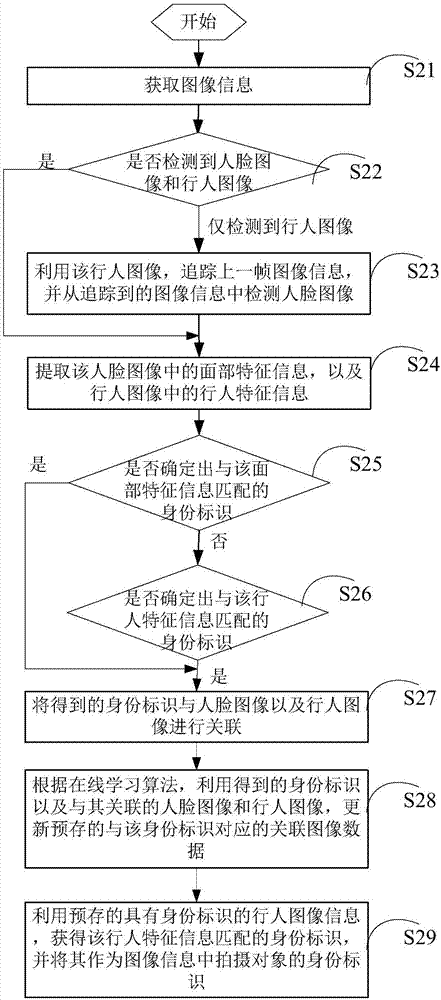

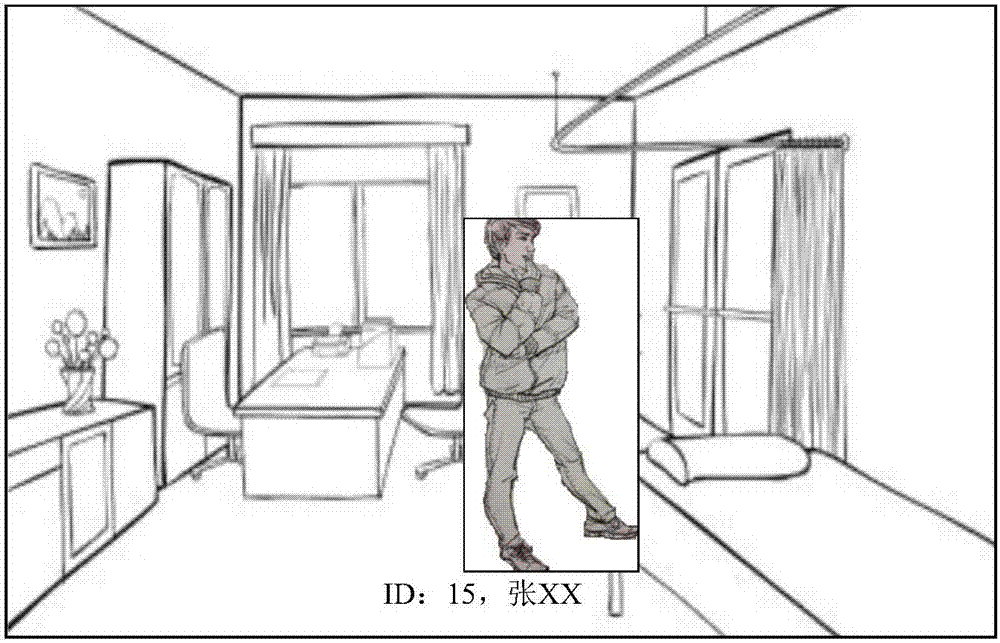

Information processing method and device and electronic device

ActiveCN106991395AImprove accuracyRich image informationCharacter and pattern recognitionPattern recognitionInformation processing

The application provides an information processing method and device and an electronic device. After the image information is obtained, a face identification algorithm, a face tracking algorithm and a pedestrian identification algorithm can be utilized to process the image information synchronously, and the processed data is correlated to obtain the correlated image data, so that the identity identifiers of the shot objects in the image information are determined by utilizing the correlated image data, and the user identity identification accuracy is improved substantially. Moreover, according to the application, the corresponding relation between the identity identifiers and the correlated image data is established, thereby enriching the user image information correlated with the identity identifiers, and laying the foundation for verifying the user identity rapidly and reliably in future.

Owner:LENOVO (BEIJING) LTD

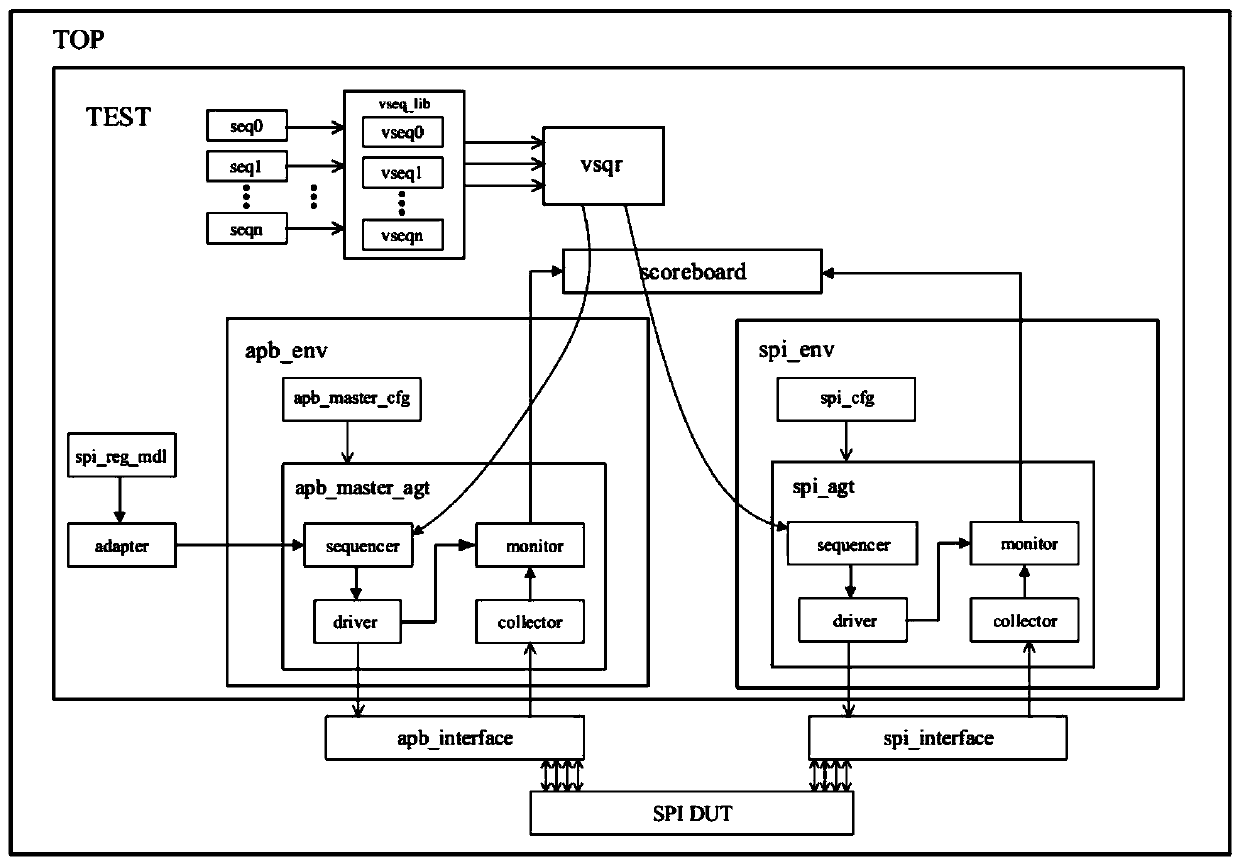

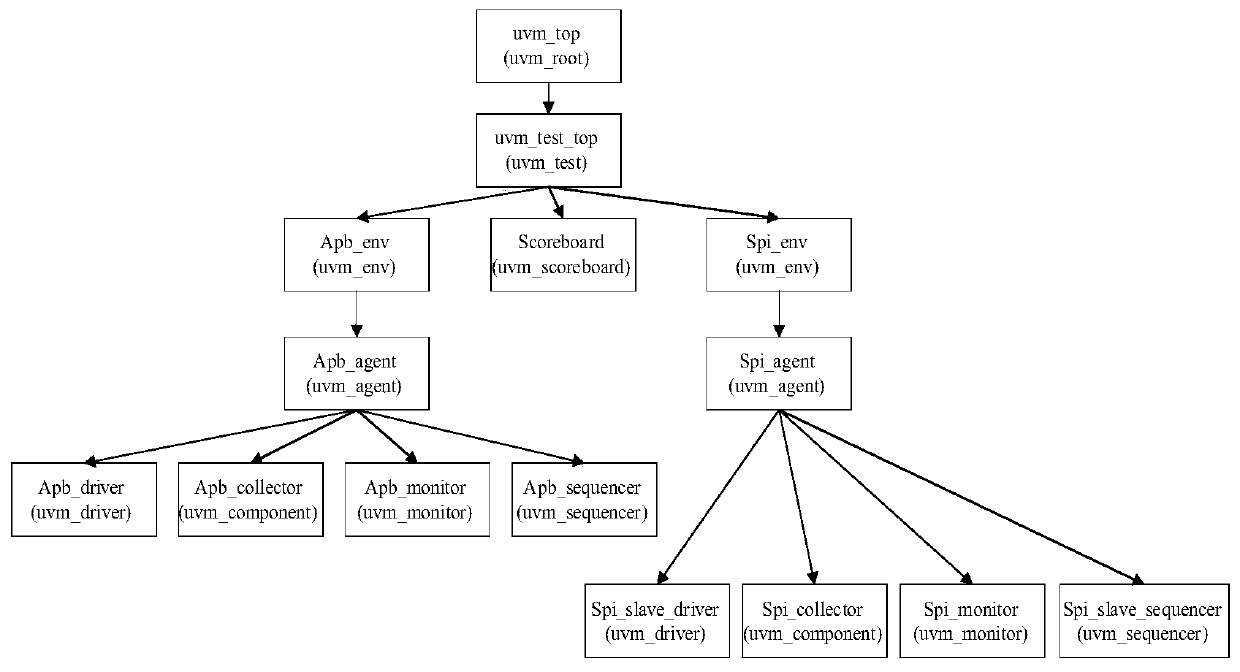

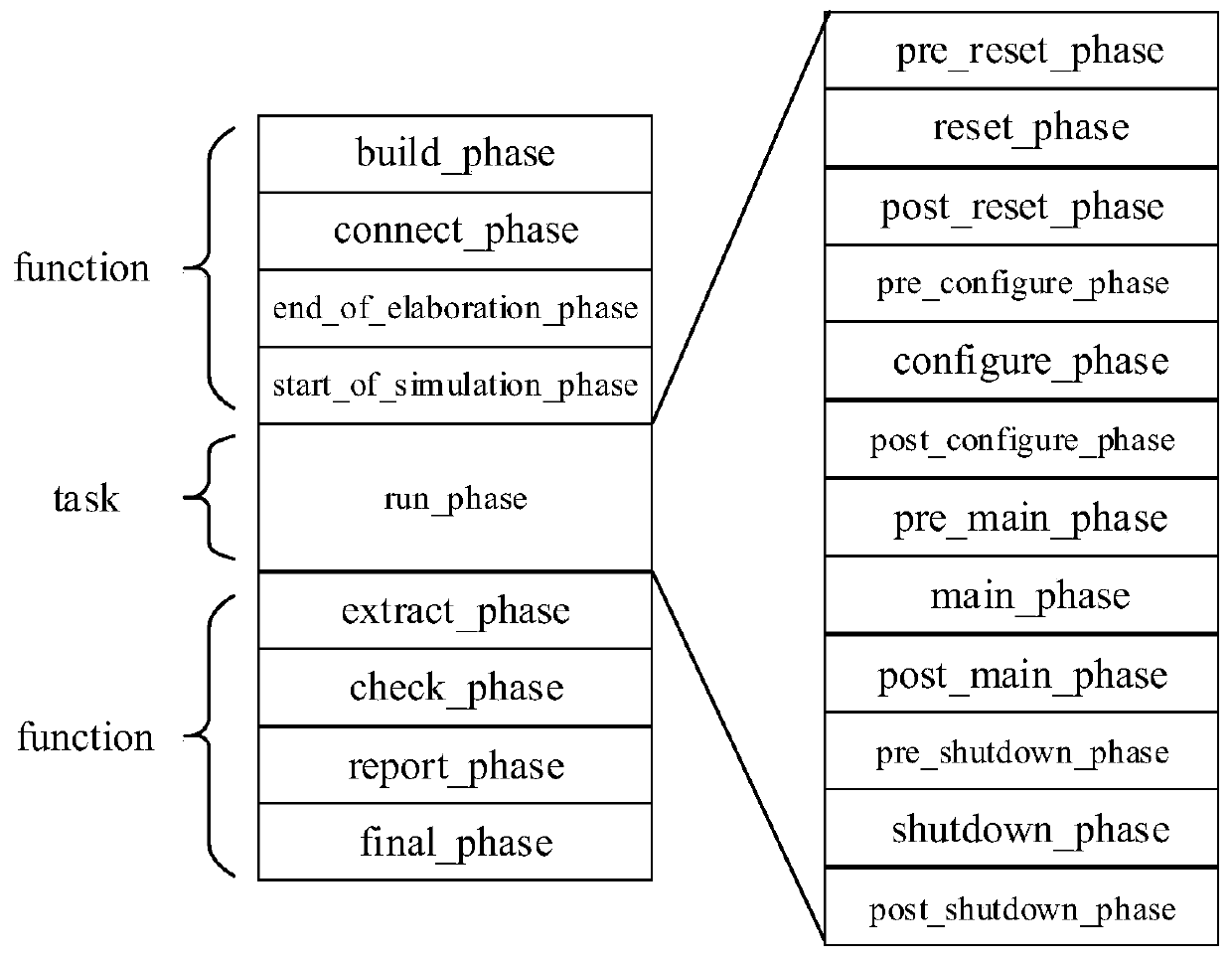

SPI verification method based on UVM verification methodology

InactiveCN109739699AVerified and reliableImprove reusabilityFunctional testingComputer architectureNetwork packet

The invention relates to an SPI verification method based on UVM verification methodology, which is characterized in that a verification platform is constructed by adopting the UVM verification methodology and a system-level hardware description language, and function verification is implemented on an SPI module. The verification platform comprises: a verification platform, a test case test, a virtual excitation generation module vsqr, the APB system environment is apb _ env; the APB configures a module apb _ master _ cfg, and the module apb _ master _ cfg is connected with the APB; the APB agent module is an apb _ master _ agt, and the APB agent module is an apb _ master _ agt; the SPI environment is spi _ env; the SPI configures a module spi _ cfg; the SPI agent module is set as spi _ agt; an SPI register model spi _ reg _ mdl, the system comprises a format conversion module, an excitation generation module, an excitation driver module, a response collection module, a monitoring module, and a result comparison module. The format conversion module comprises an adder, an excitation generation module, an excitation driver module, a response collection module, a monitoring module anda result comparison module. According to the invention, a UVM verification methodology is adopted to realize high hierarchy; a verification platform with high reusability can generate various types of randomized data packets under the constraint condition, traversal of all addresses and instructions is achieved, the self-checking functions of automatic report collection, result comparison and thelike with the function coverage rate are achieved, and the verification efficiency and the verification reliability are improved.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

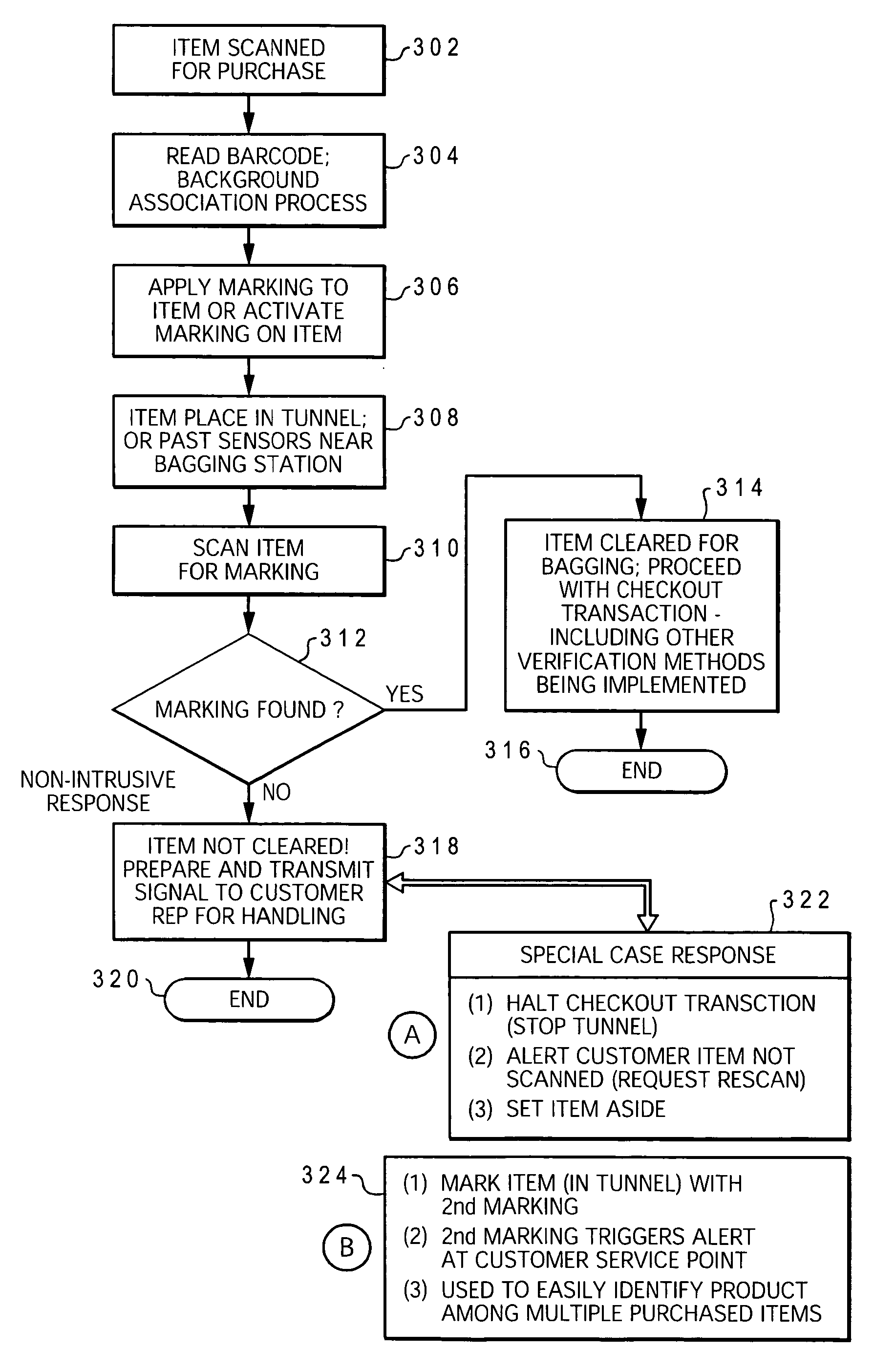

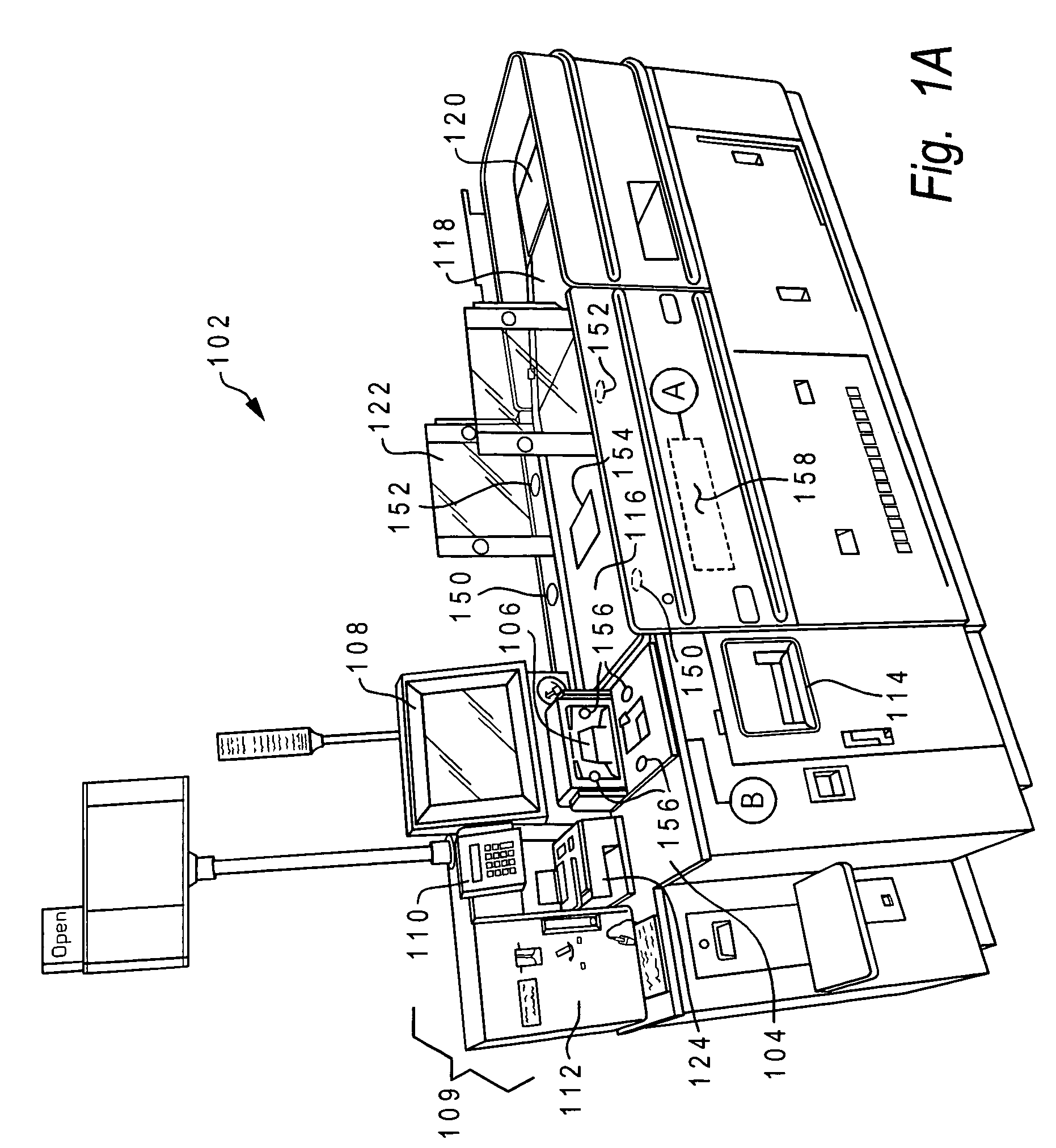

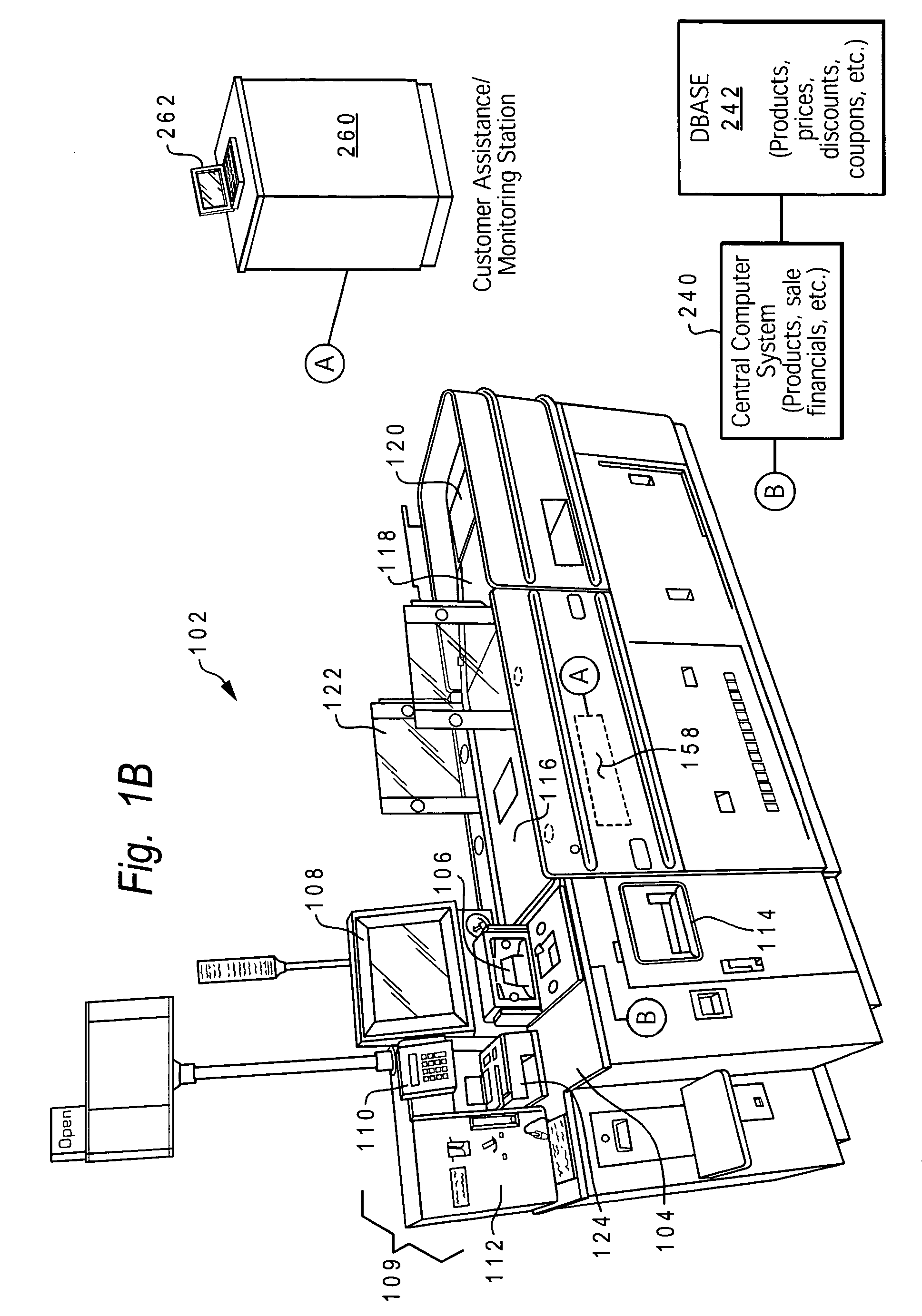

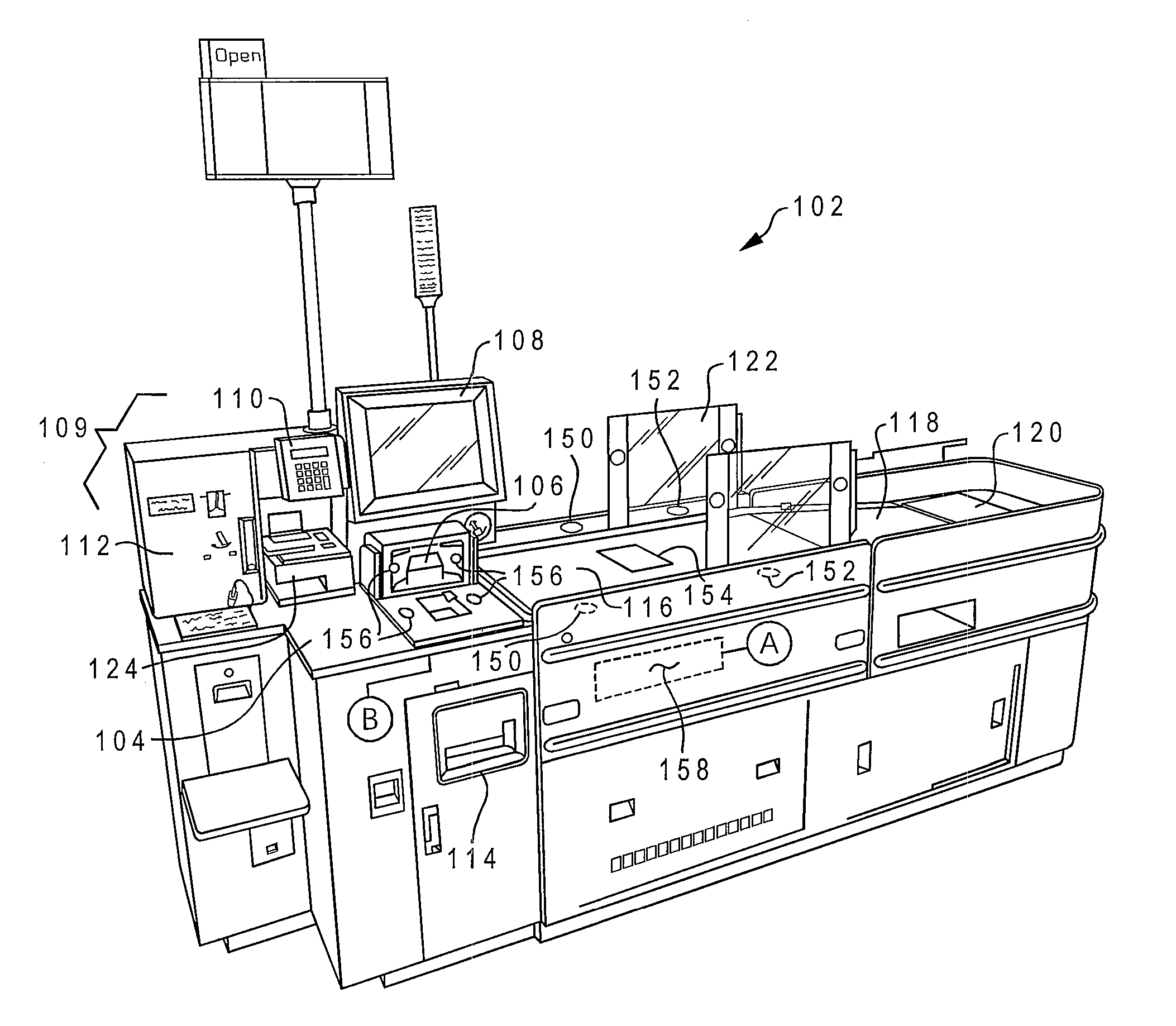

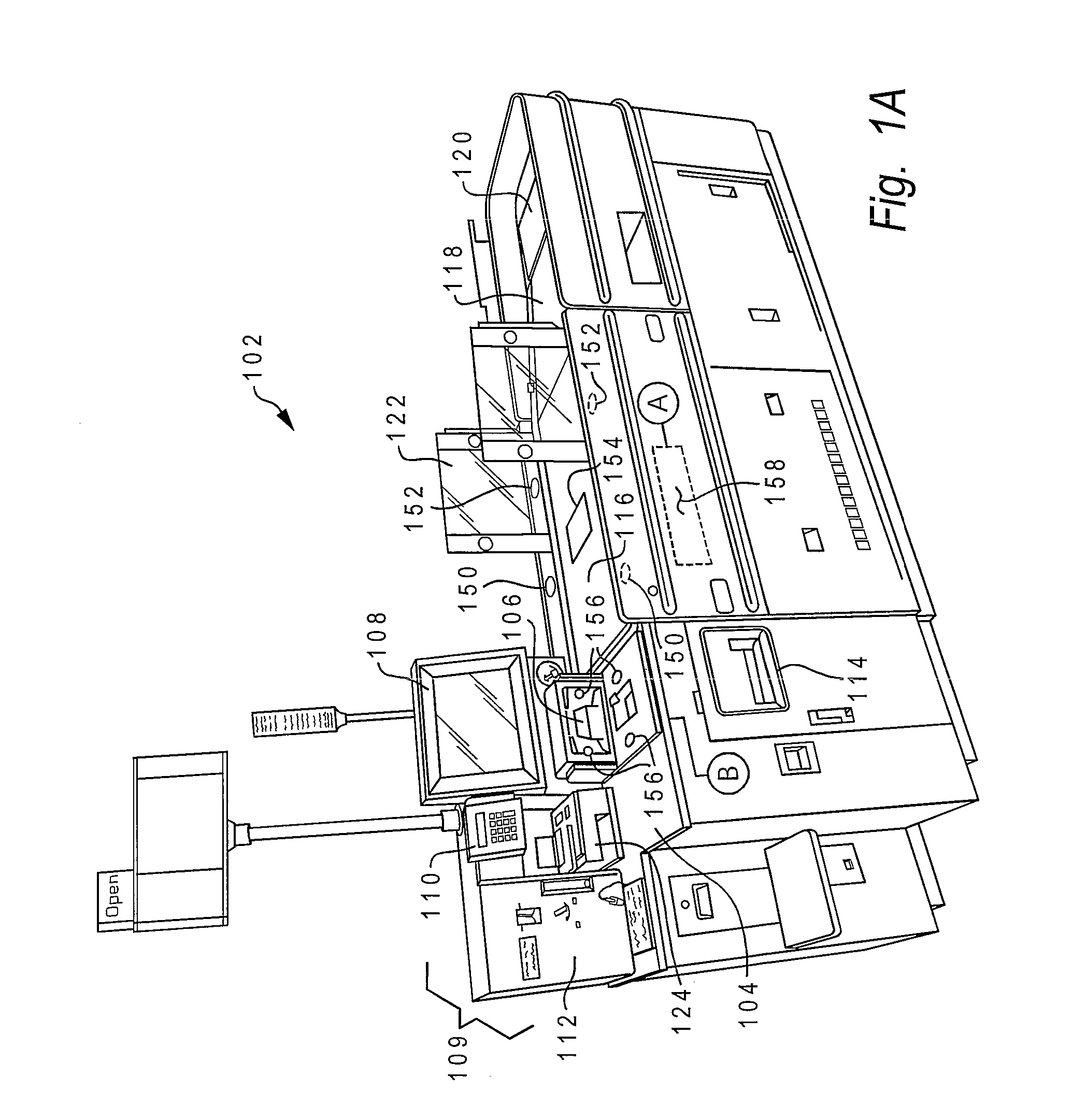

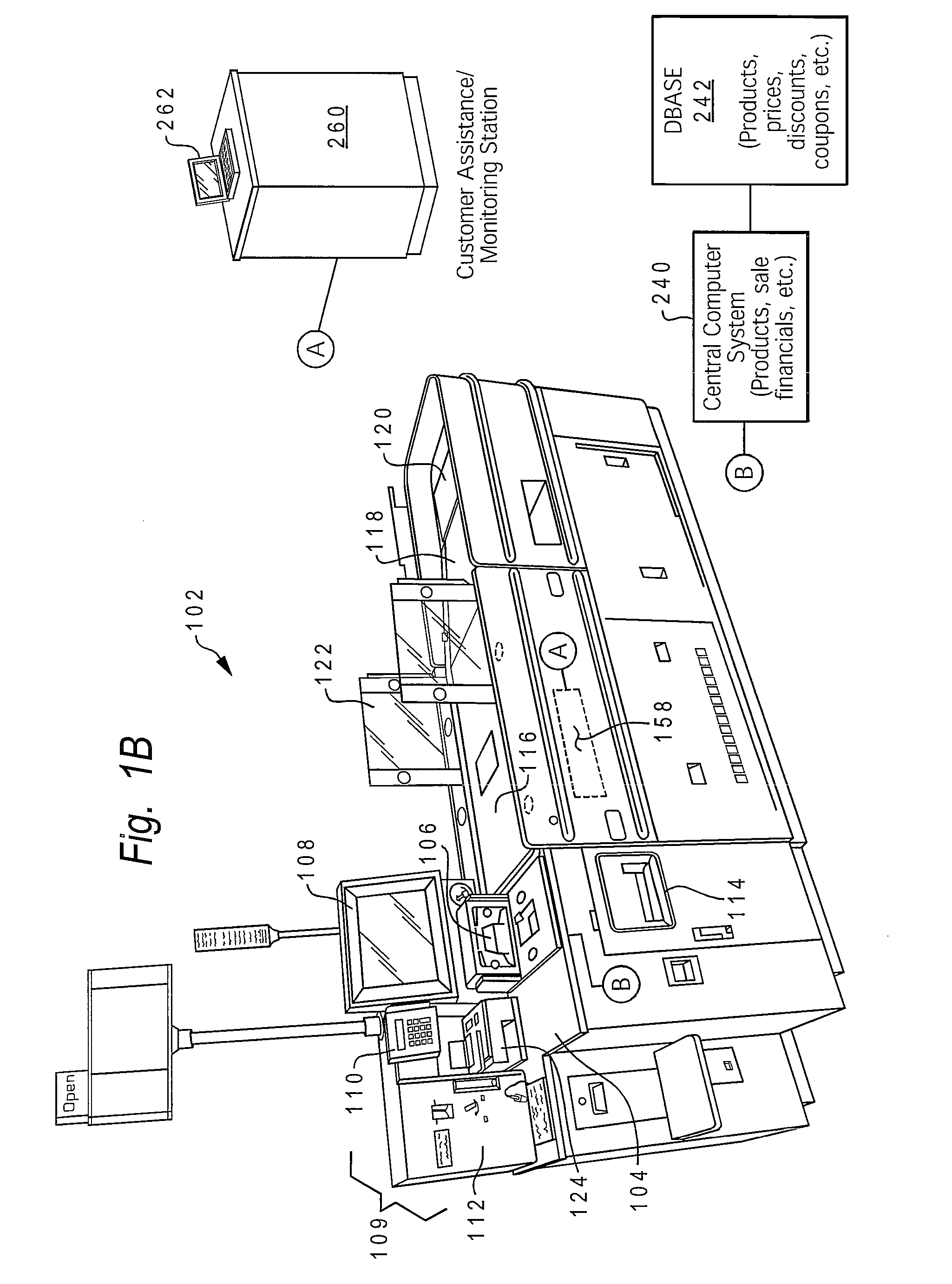

Enhanced purchase verification for self checkout system

InactiveUS7325729B2Verified and reliableCash registersAlarm indicatorsBiological activationPurchasing

A method and system for enabling reliable verification of items being purchased using a self checkout system. The self checkout system is equipped with a verification mark dispenser and verification mark detectors that respectively dispenses a mark on an item as the item is being scanned for purchasing and then verifies, by detecting the mark on the item, that the item being bagged (or passed through the tunnel) is the same item that was scanned. When a customer scans an item for purchase, the purchase transaction is processed and, if the item is successfully purchased (i.e., transaction confirmed), a mark (made of a non-reactive but detectable material or ink) is placed on the exterior packaging of the item. When the item is placed in the tunnel, the detector, sensitive to the activation of the specific marking and located at or in the tunnel, detects the marking on the item. If the activated marking is not detected by the detector, an alert condition is triggered indicating that an un-purchased product is being placed in the customer's sack.

Owner:TOSHIBA GLOBAL COMMERCE SOLUTIONS HLDG

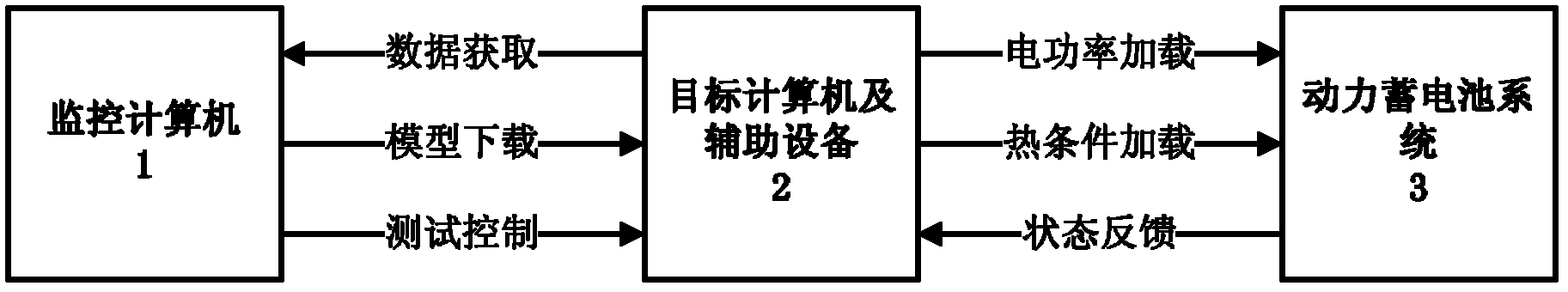

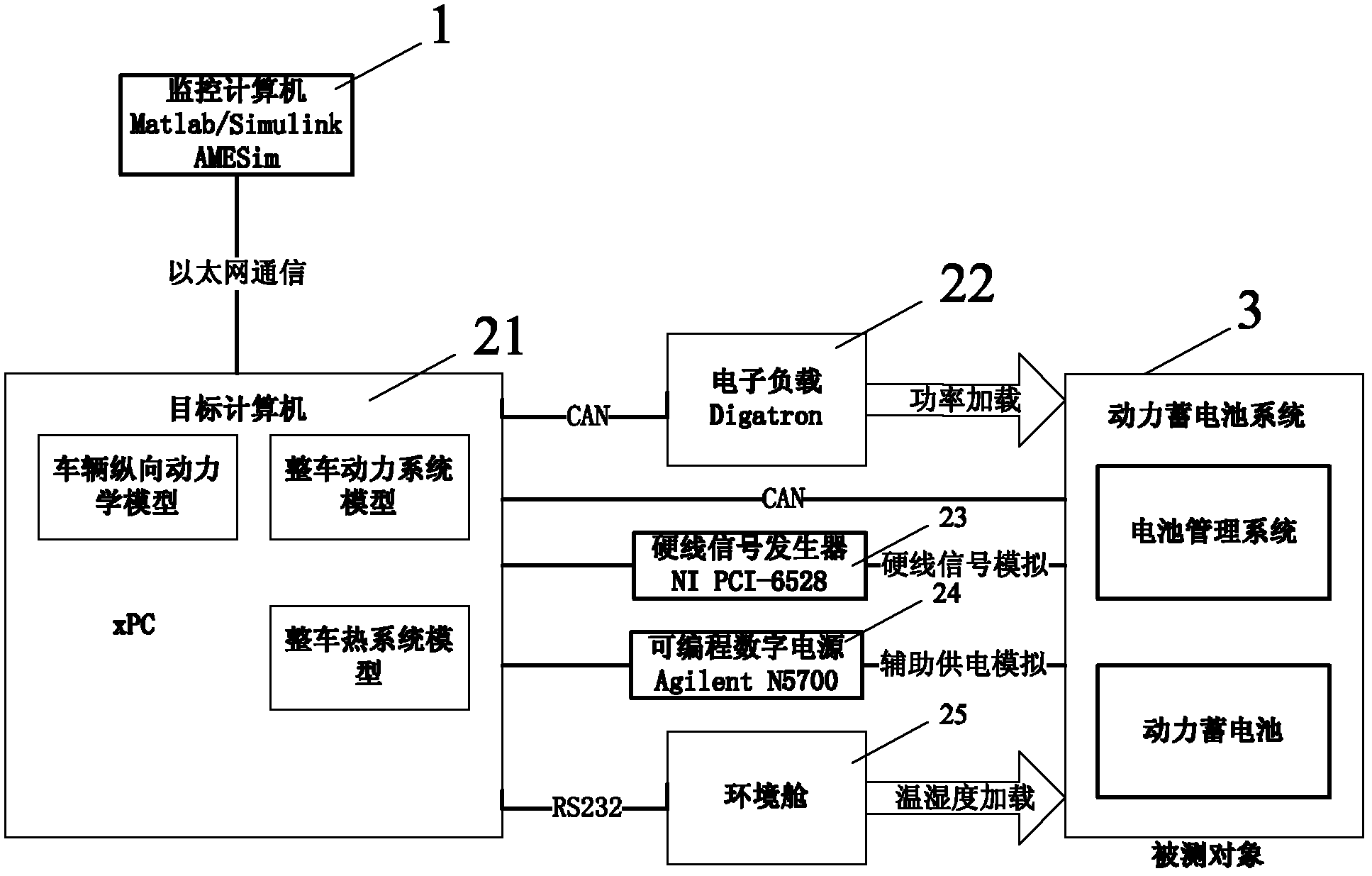

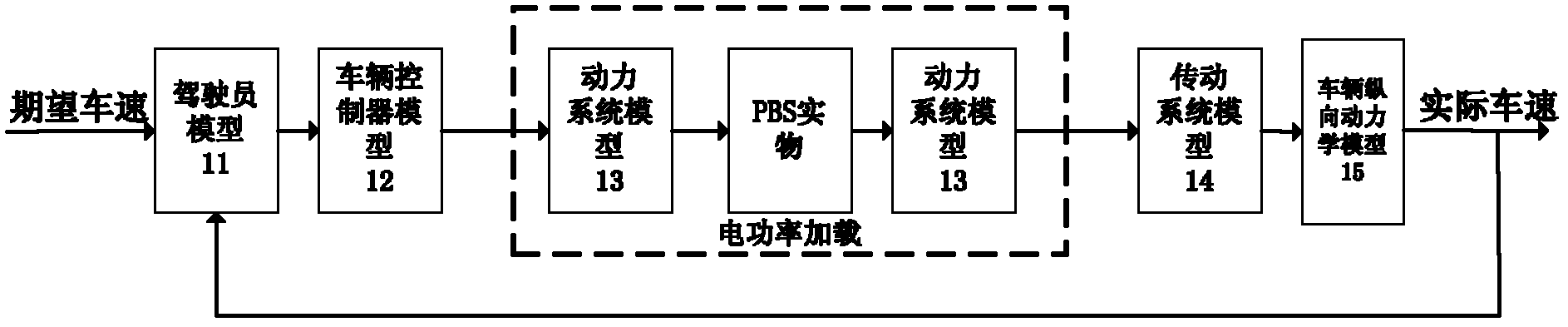

Test platform for hardware-in-the-loop simulation of power storage battery system

ActiveCN102841315AVerified and reliableReduce the number of testsElectrical testingElectronic loadTested time

The invention relates to a test platform for hardware-in-the-loop simulation of a power storage battery system. The test platform comprises a monitoring computer, an object computer, an electronic load, an environmental chamber, a programmable digital power source and a hard wire signal generator, wherein the monitoring computer and the object computer are connected, and the electronic load, the environmental chamber, the programmable digital power source and the hard wire signal generator are respectively connected between the object computer and the power storage battery system. Compared with the prior art, the test platform disclosed by the invention has the advantages that real vehicle test times are reduced, the cost of development is saved, a testing process is simplified, the automation of the testing process is realized and the like.

Owner:HUIZHOU BNET TECH CO LTD

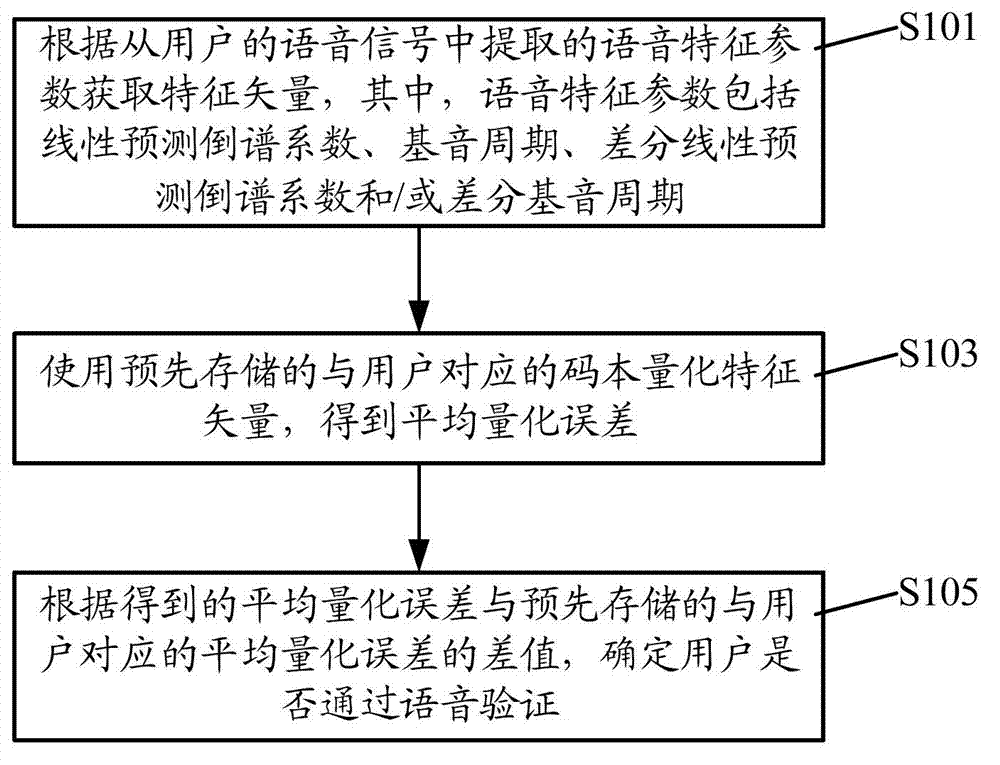

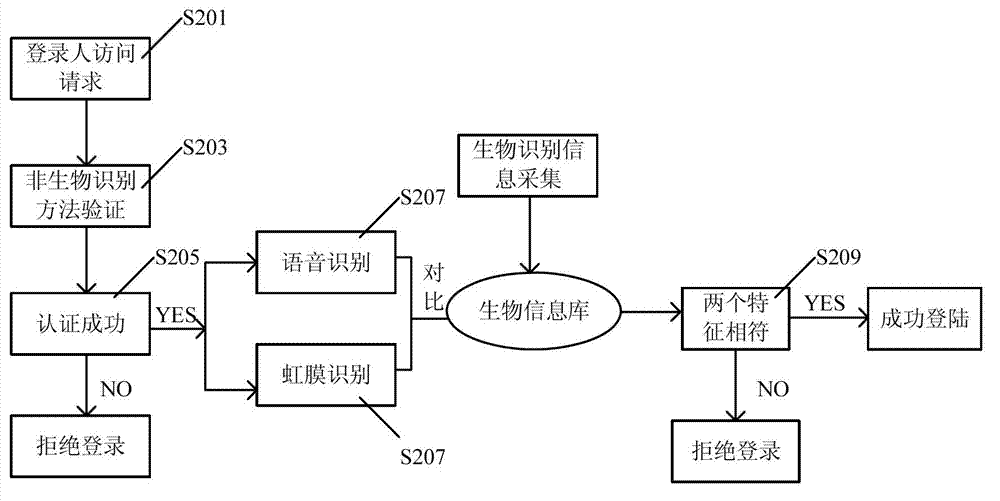

User verification method and device

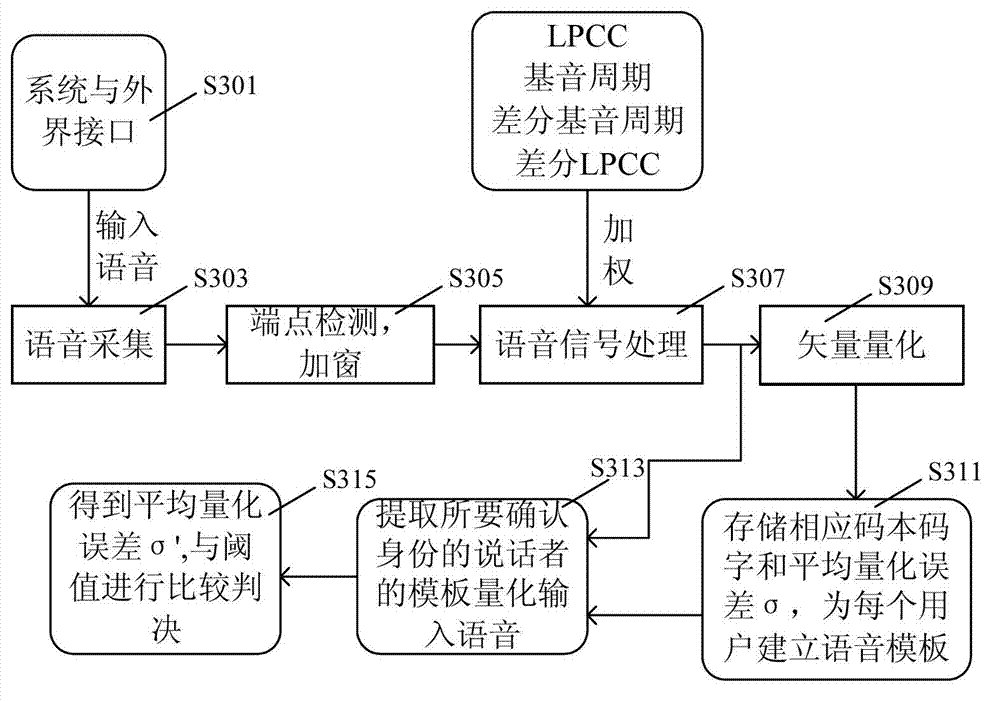

InactiveCN103207961AQuick verificationVerified and reliableDigital data authenticationSpeech recognitionUser verificationSpeech verification

The invention discloses a user verification method and device. The method comprises the following steps of: acquiring characteristic vectors from voice characteristic parameters extracted from voice signals of a user, wherein the voice characteristic parameters comprise linear prediction cepstrum coefficients, pitch periods, differential linear prediction cepstrum coefficients and / or differential pitch periods; calculating an average quantization error according to a pre-stored codebook quantization characteristic vector corresponding to the user; and determining whether the user passes voice verification according to the difference between the average quantization error and the pre-stored average quantization error corresponding to the user. The method provided by the invention can determine whether the user passes voice verification so as to quickly and reliably verify the identity of the user by processing the voice characteristic parameters extracted from the voice signals of the user and comparing the processed information with the pre-stored information, thereby improving system security in a login step.

Owner:DAWNING INFORMATION IND BEIJING

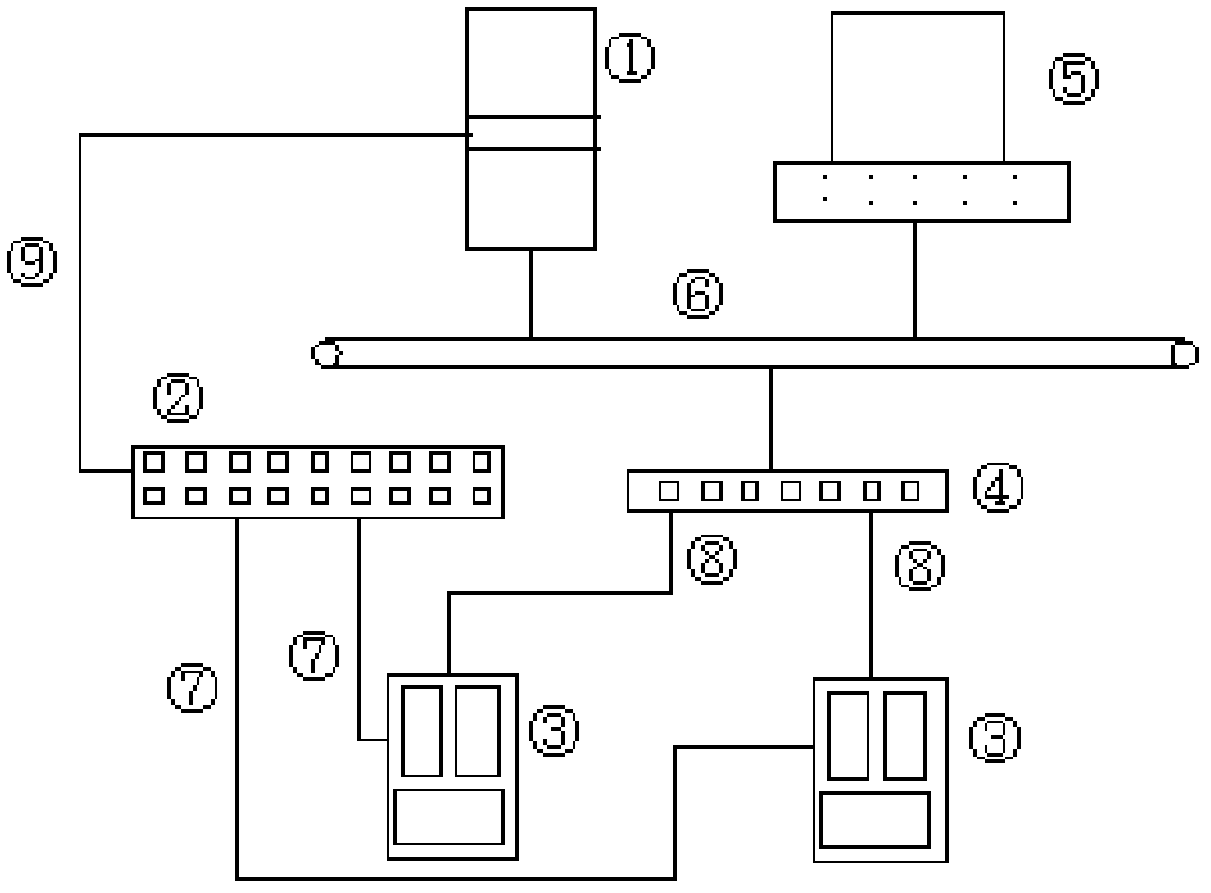

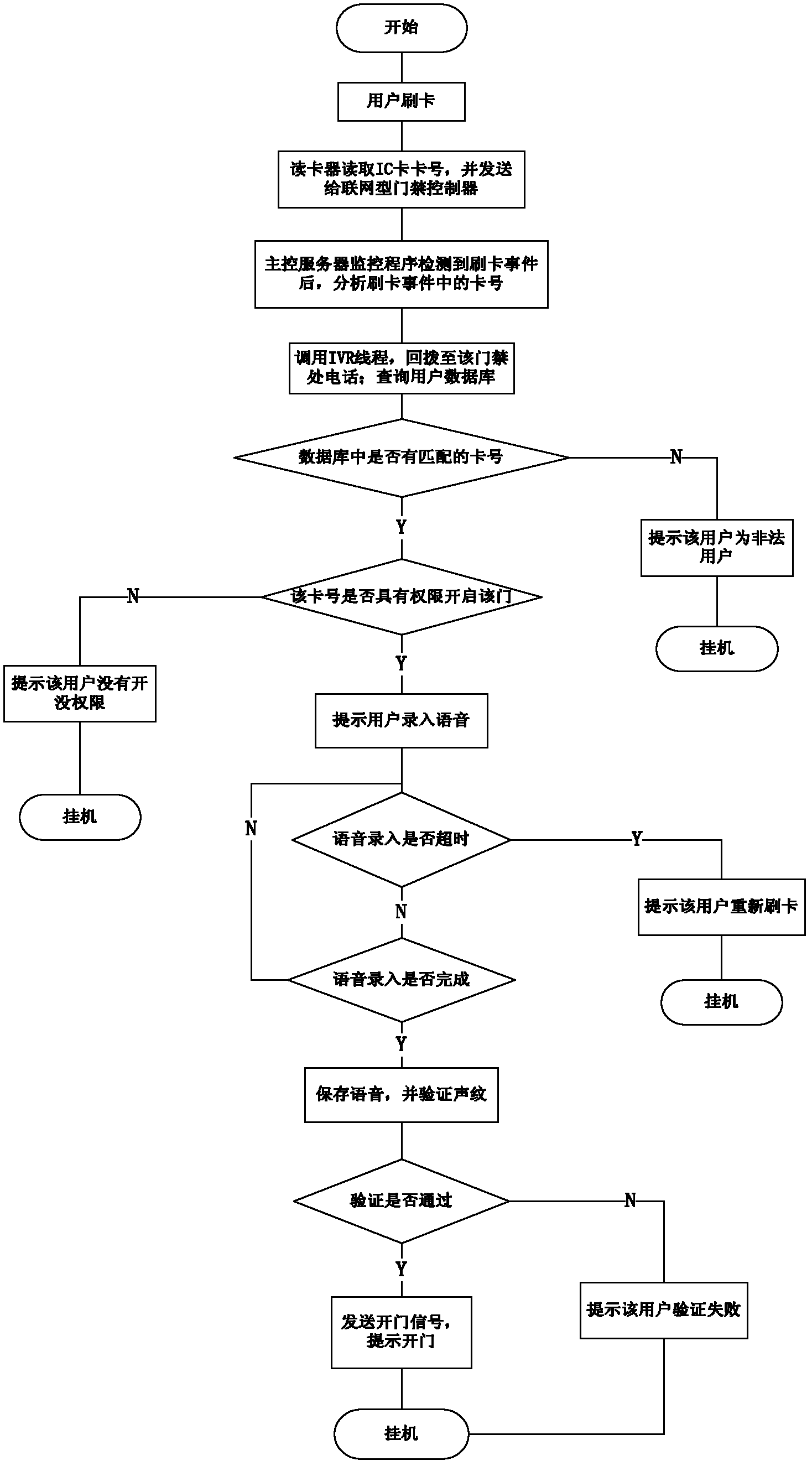

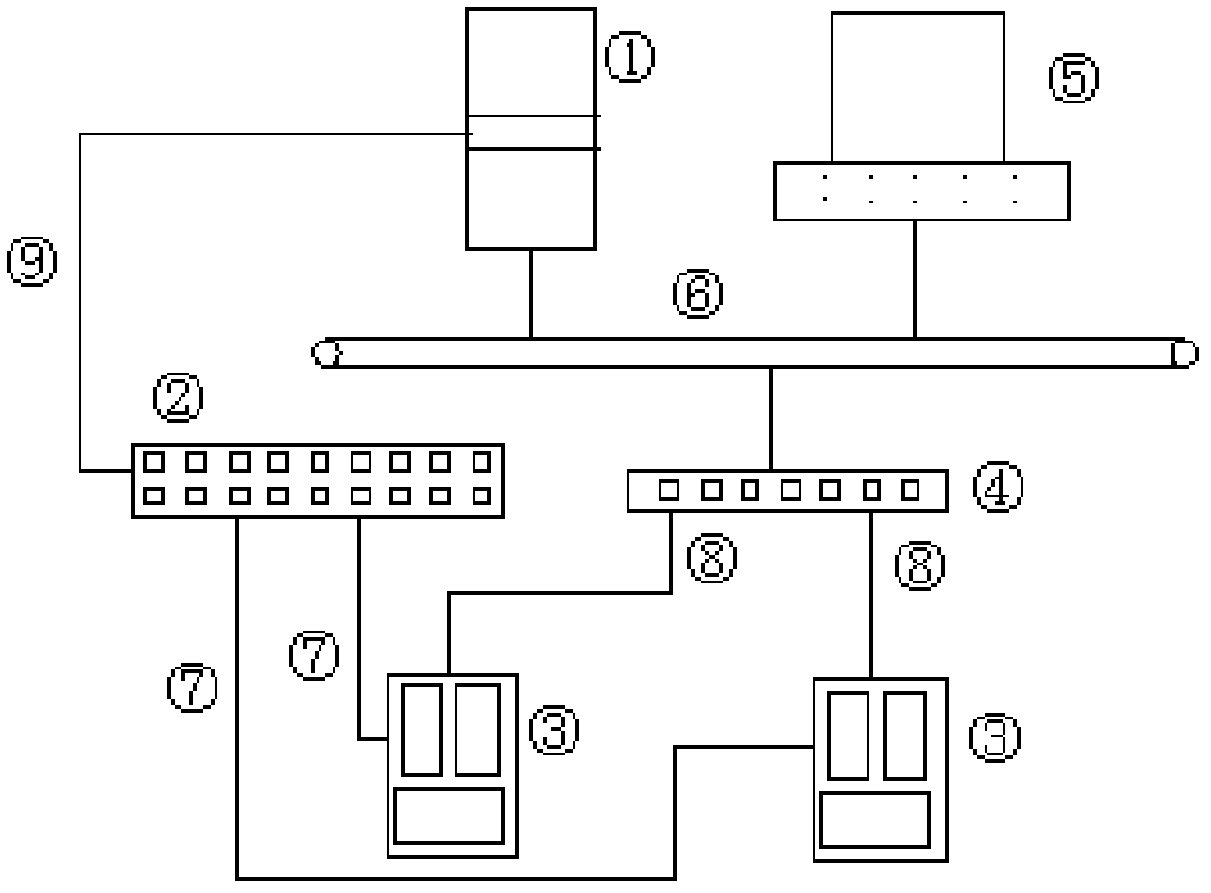

Telephone voiceprint entrance guard

InactiveCN102306412AImprove security levelOvercoming noiseTelephonic communicationIndividual entry/exit registersNetwork switchTelephone exchange

The invention relates to a telephone voiceprint entrance guard, and relates to an entrance guard apparatus. According to the invention, with the telephone voiceprint entrance guard, automatic access controlling voiceprint verification can be realized through a telephone, and jactitator identity can be easily identified. The entrance guard comprises a main controlling server, a telephone exchange, a voiceprint entrance guard controller, a network switch or a hub, a managing device, a bus, a telephone wire, a conduction-through twisted pair and a data trunk. The telephone exchange is connected to the main controlling server through the data trunk. The telephone exchange is connected to the voiceprint entrance guard controller through the telephone wire. The voiceprint entrance guard controller is connected to the network switch or the hub through the conduction-through twisted pair. The network switch or the hub is respectively connected to the main controlling server and the managing device through the bus.

Owner:XIAMEN UNIV

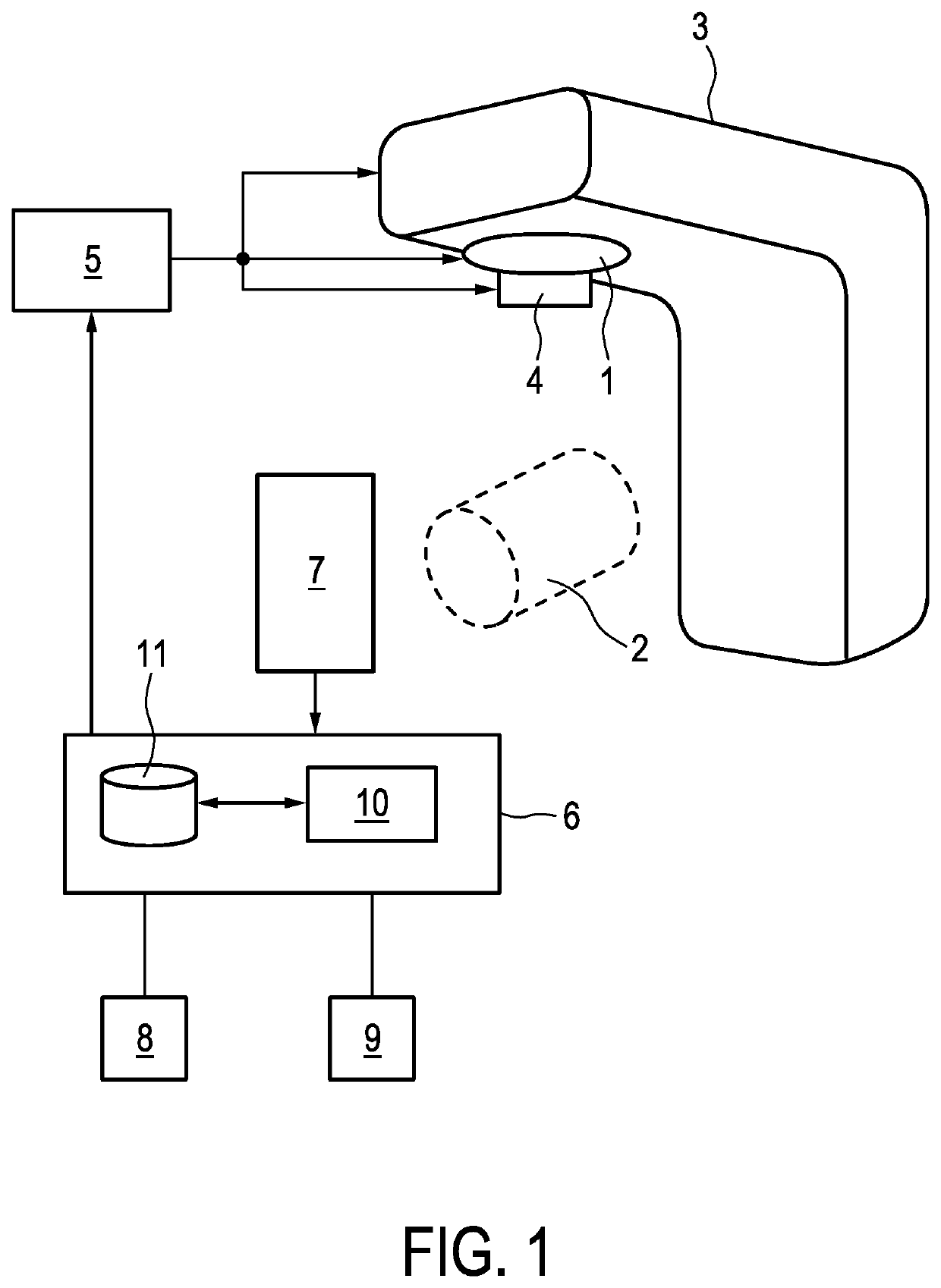

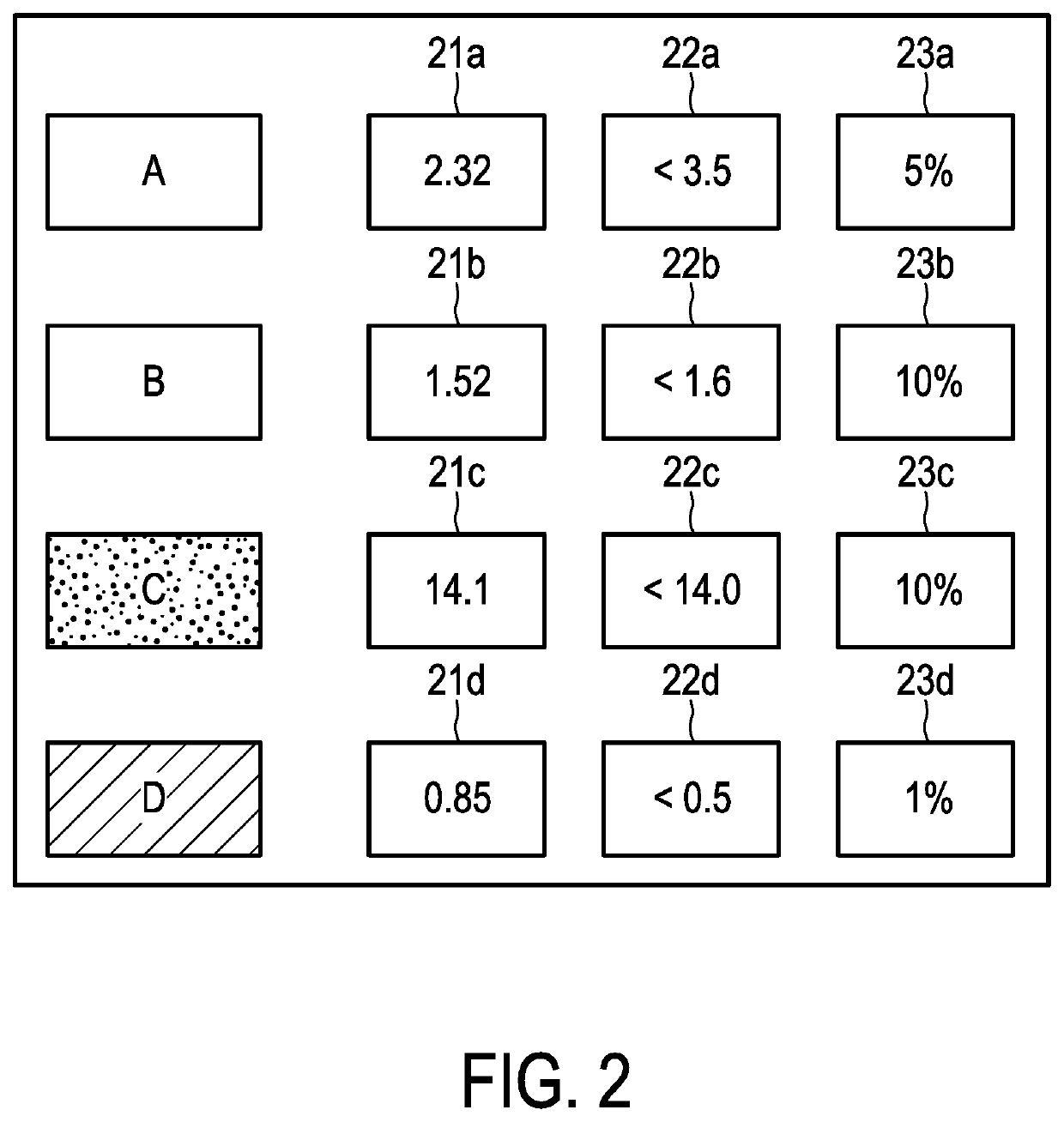

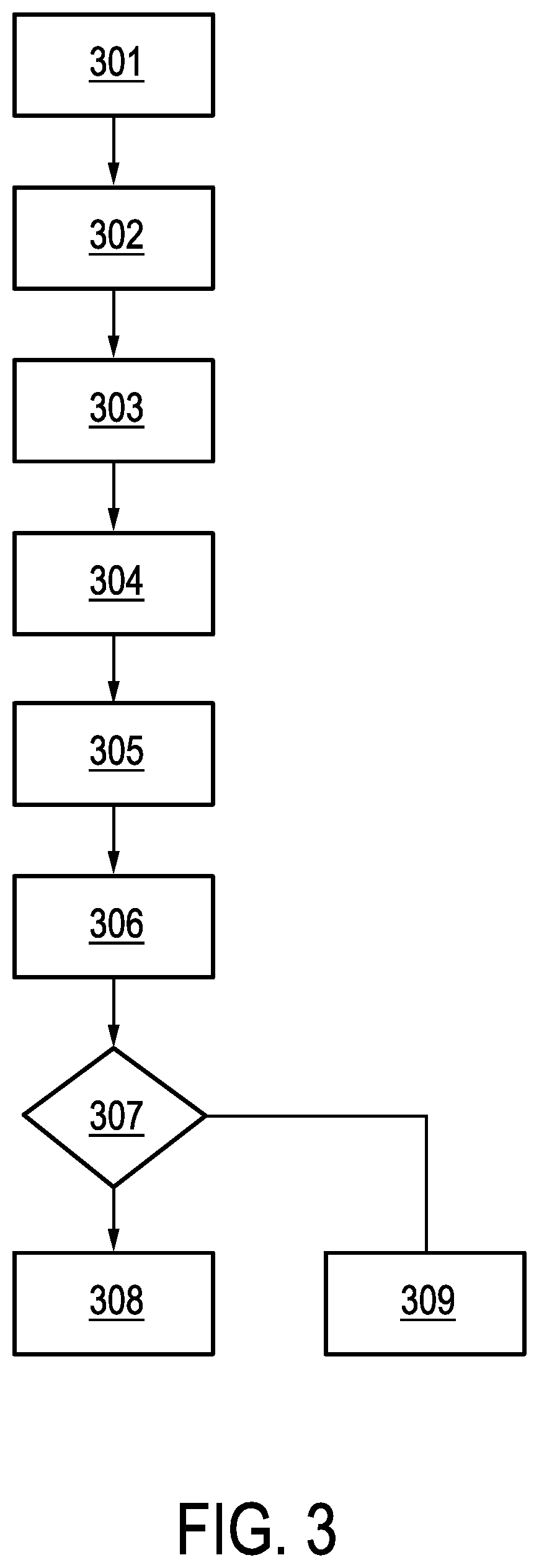

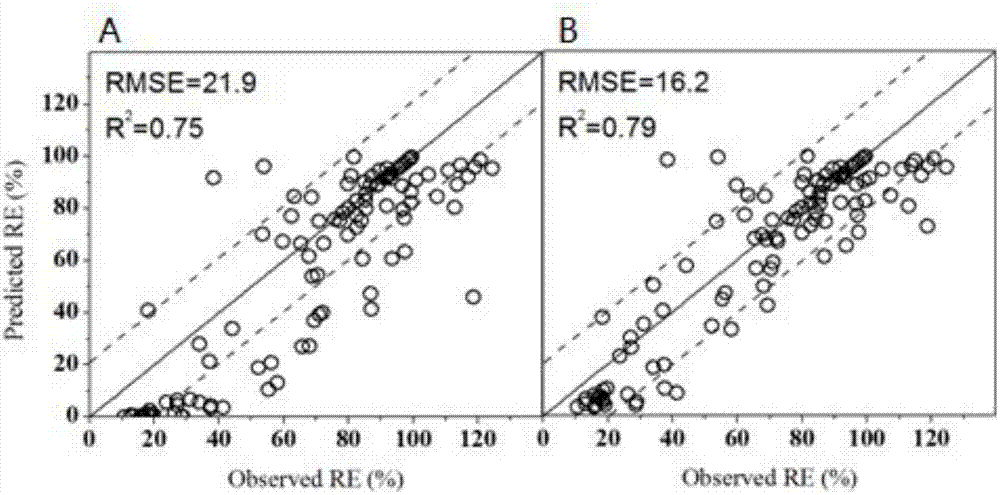

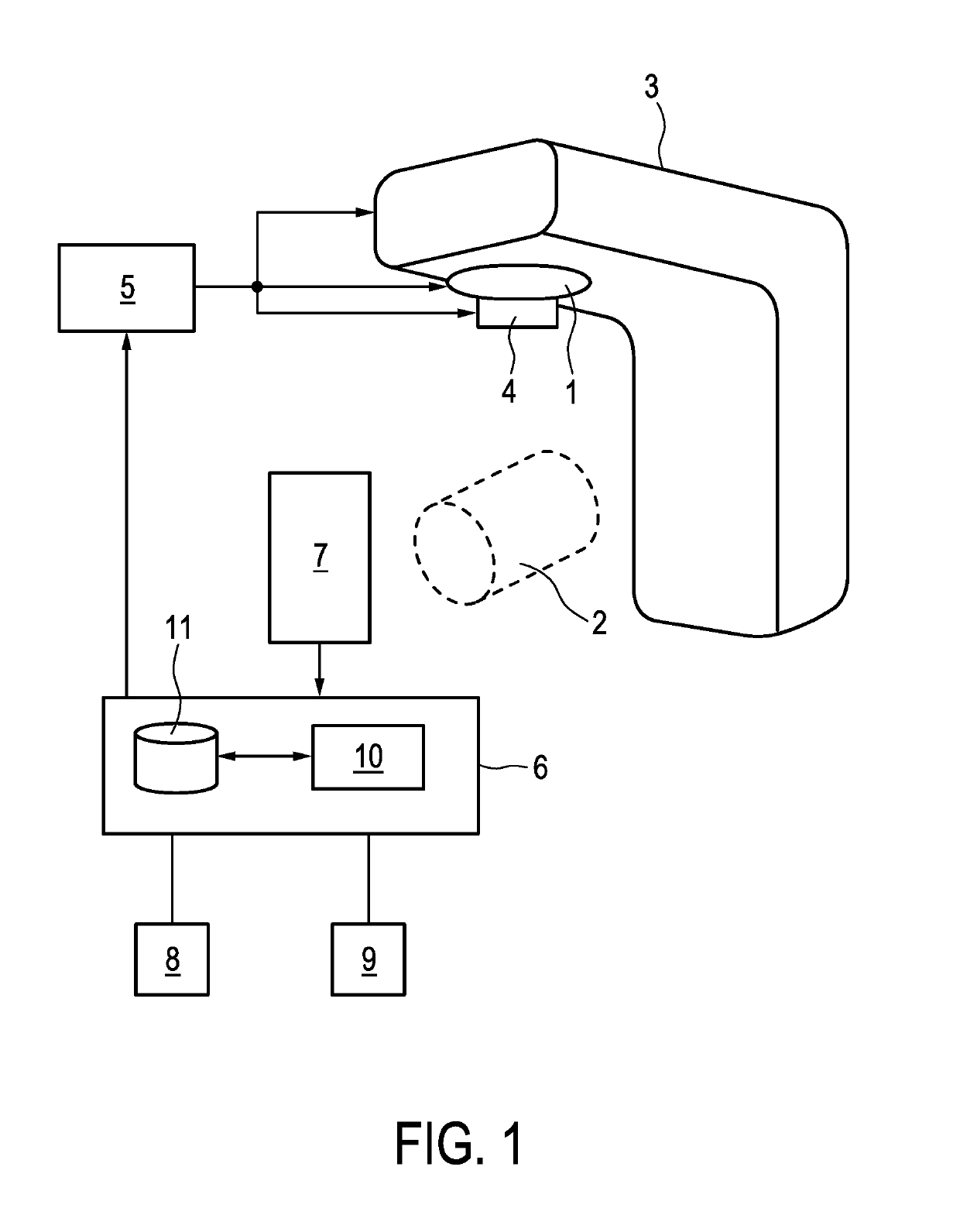

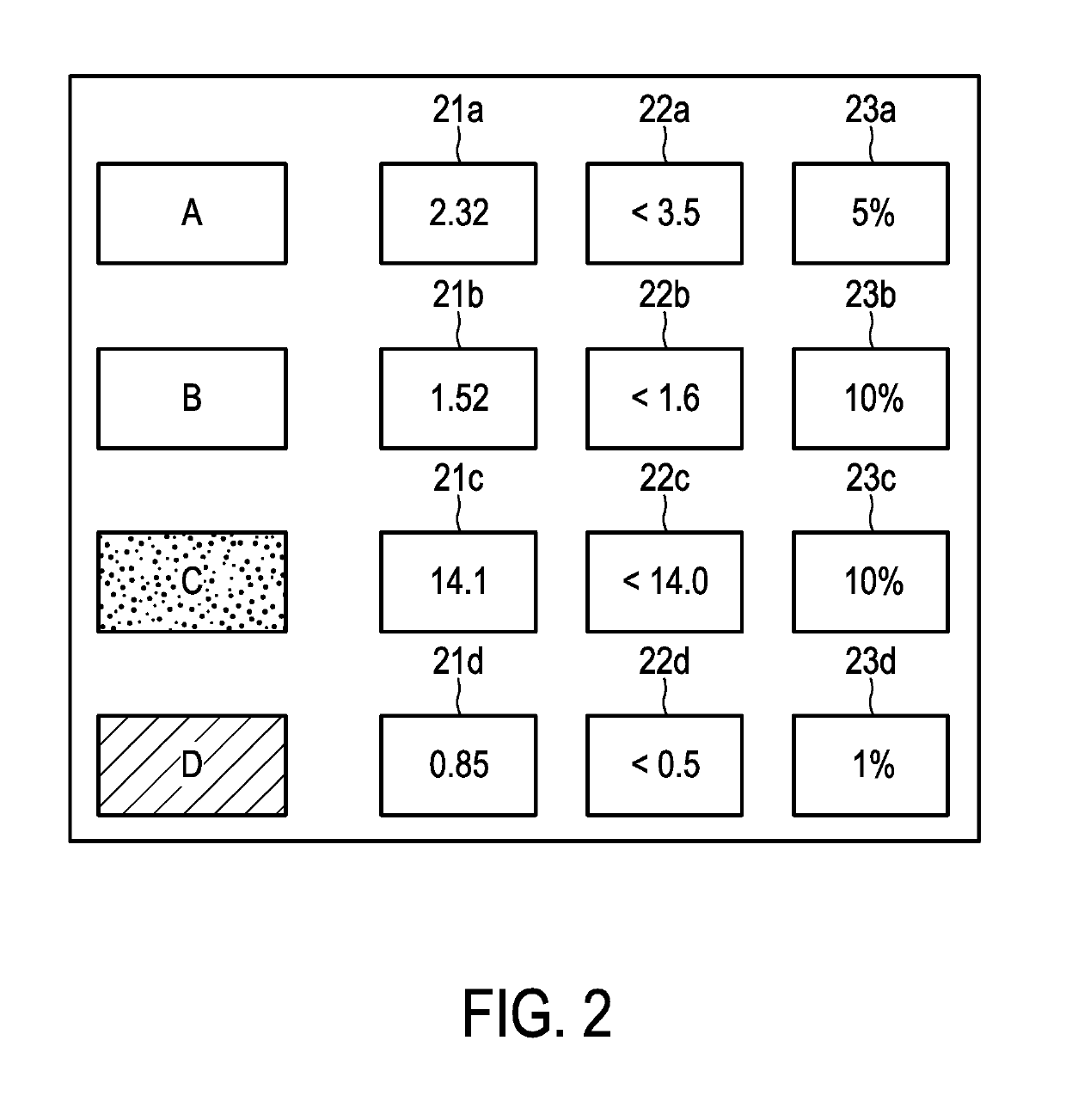

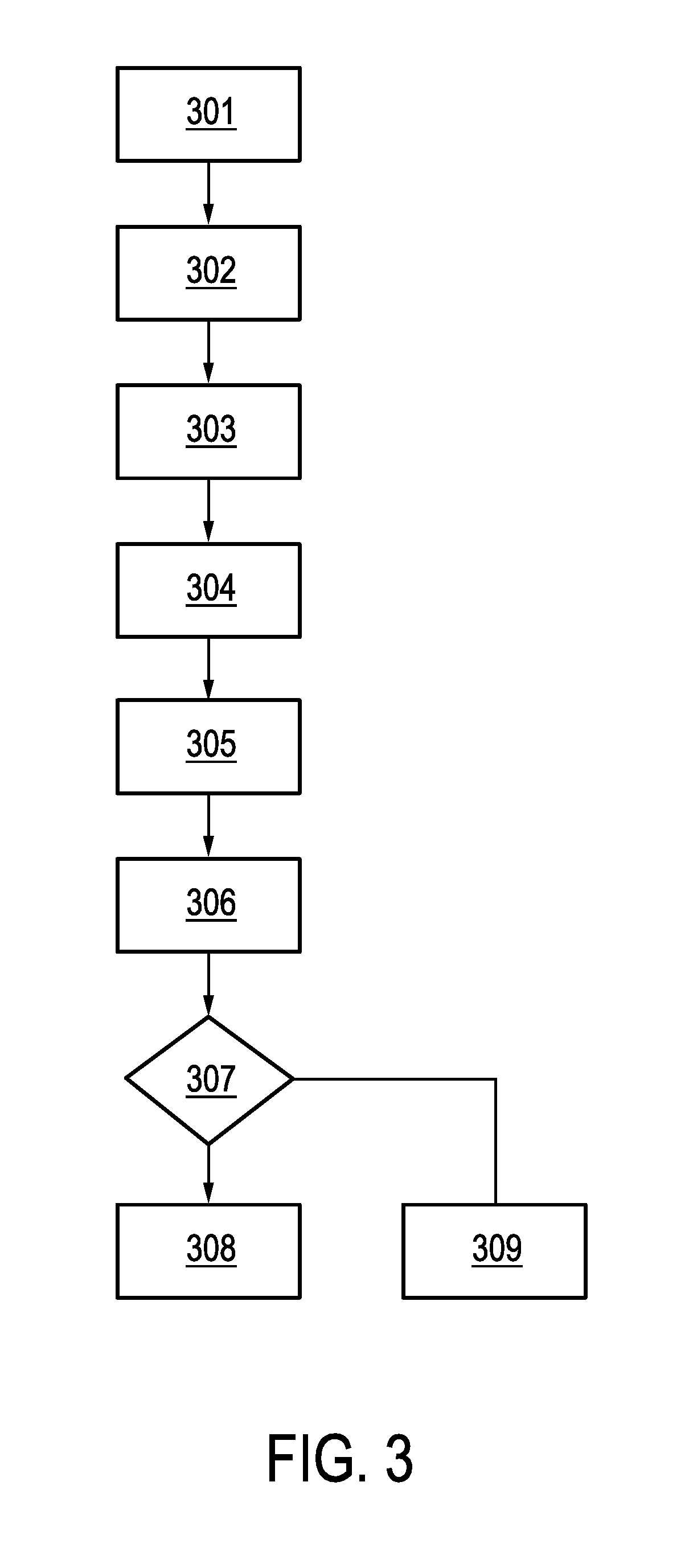

Evaluation of dose accuracy of radiation therapy treatment plans

ActiveUS10765891B2Verified and reliableReduce the numberMechanical/radiation/invasive therapiesX-ray/gamma-ray/particle-irradiation therapyEngineeringNuclear medicine

The invention relates to a system and a method for evaluating a treatment plan for an external radiation therapy treatment, the treatment plan comprising parameters for controlling an external radiation therapy apparatus during the treatment. The system comprises a database storing historic treatment plans and storing for each historic treatment plan a quality parameter indicative of whether a deviation between a planned dose distribution and a measured dose distribution resulting from an execution of the treatment plan is within an acceptable limit. An evaluation unit determines a threshold value for each of a plurality of treatment plan metrics based on the historic treatment plans and the associated quality parameters. Further, the evaluation unit calculates a value of each of the metrics for the treatment plan and compares the value of each of the metrics with the threshold value determined for the respective metric.

Owner:KONINKLJIJKE PHILIPS NV

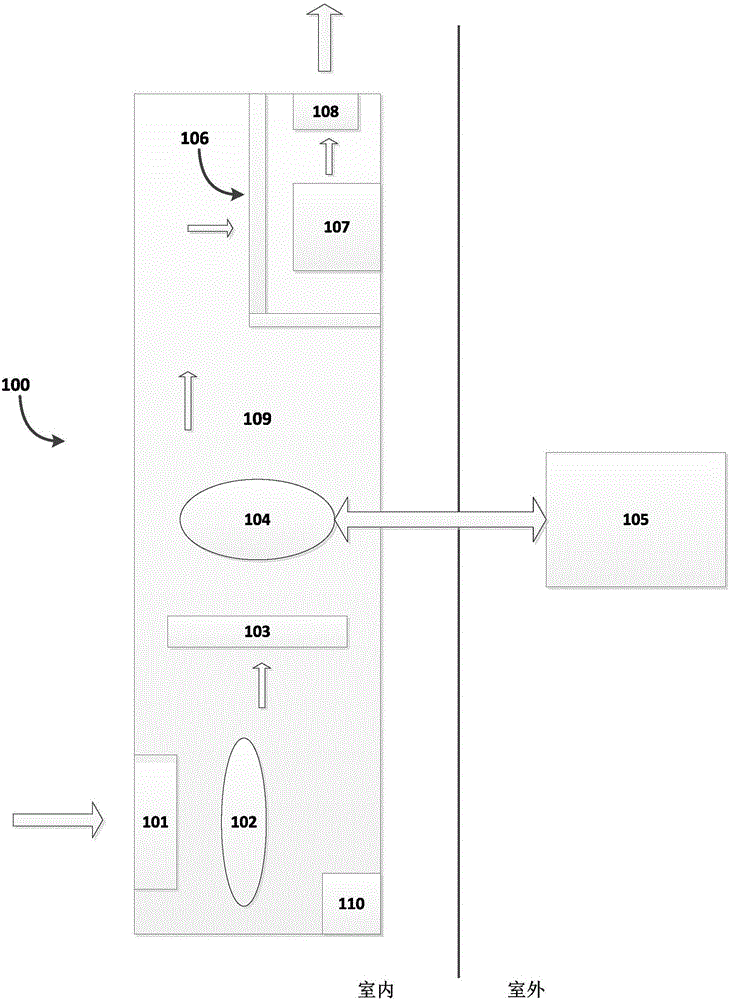

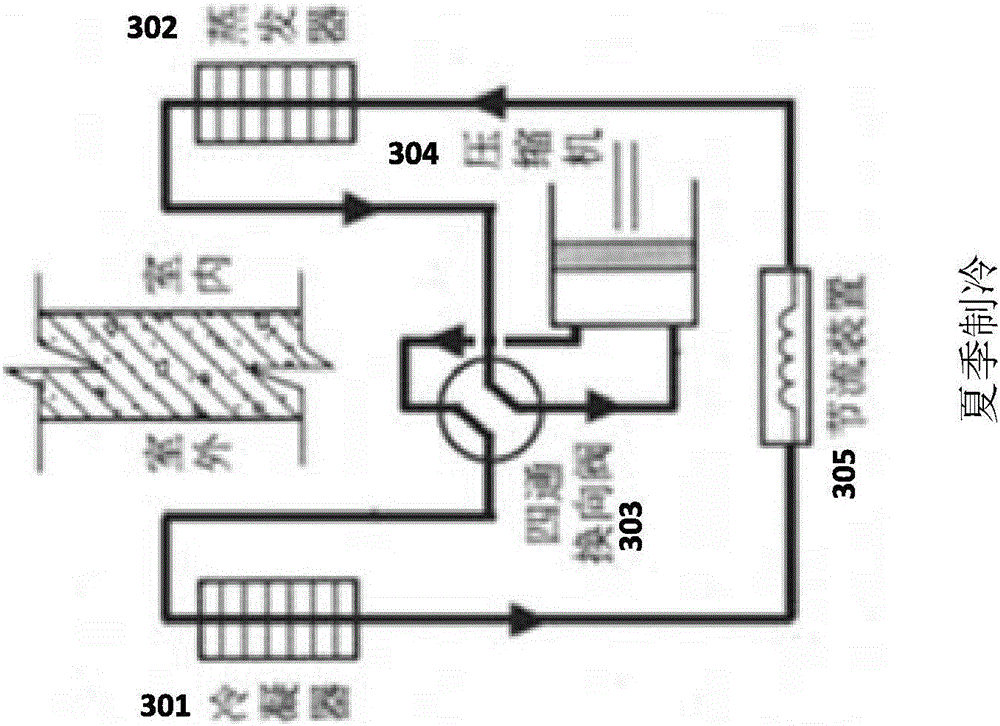

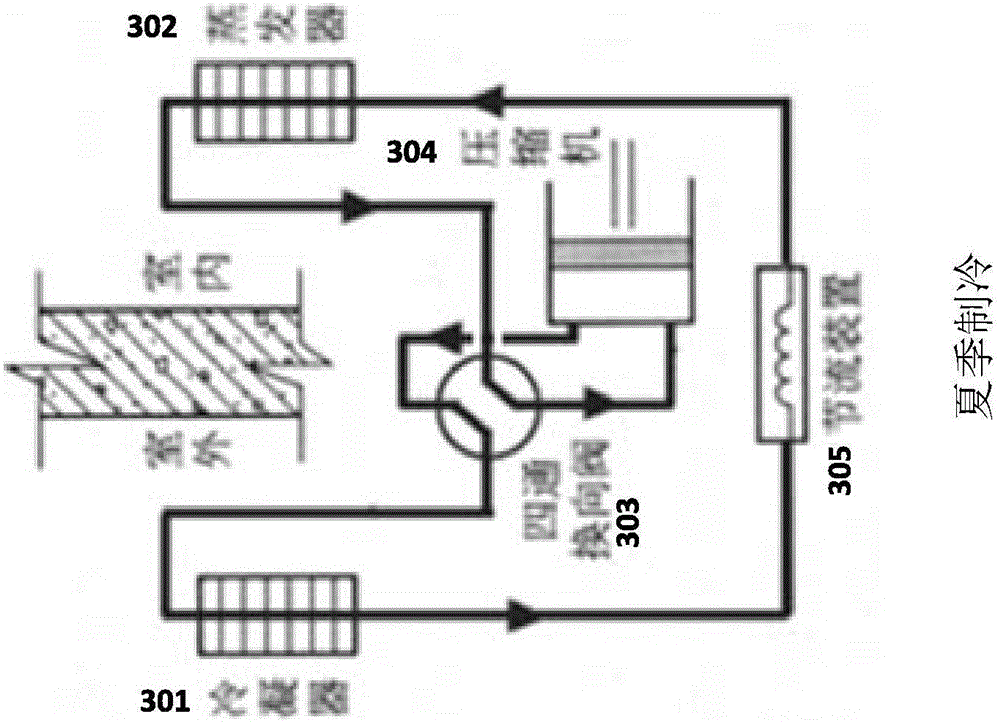

Air-conditioning air purification system with remote control function

InactiveCN105910266ALow powerReduced Power RequirementsMechanical apparatusSpace heating and ventilation safety systemsAir filtrationAir filter

The invention relates to an air-conditioning air purification system with a remote control function. The air-conditioning air purification system with the remote control function comprises an air inlet device, an air outlet device, an air duct, an air filtering device, an air conditioning device and a remote control device, wherein the air inlet device is provided with an air inlet and an axial flow fan, and the air inlet device is used for guiding air into the air-conditioning air purification system; the air outlet device is provided with an air outlet and a centrifugal ventilator, and the air outlet device is used for exhausting air out of the air-conditioning air purification system; the air inlet device and the air outlet device are connected through the air duct, and the air duct is used for guiding air between the air inlet device and the air outlet device; the air filtering device is arranged in the air duct and used for filtering air; an evaporator of the air-conditioning device is arranged in the air duct; and the remote control device is configured to receive a remote control command from a user so that the user can remotely start the air-conditioning air purification system and control the operation of the air-conditioning air purification system. By the adoption of the air-conditioning air purification system, noise can be lowered, heat can be dissipated, the energy utilization rate is increased, and remote control is achieved.

Owner:殷晓冬

Enhanced Purchase Verification for Self Checkout System

InactiveUS20080048029A1Verified and reliableCash registersAlarm indicatorsFinancial transactionBiological activation

A method and system for enabling reliable verification of items being purchased using a self checkout system. The self checkout system is equipped with a verification mark dispenser and verification mark detectors that respectively dispenses a mark on an item as the item is being scanned for purchasing and then verifies, by detecting the mark on the item, that the item being bagged (or passed through the tunnel) is the same item that was scanned. When a customer scans an item for purchase, and if purchase transaction is successful, a mark (made of a non-reactive but detectable material or ink) is placed on the exterior packaging of the item. When the item is placed in the tunnel, the detector, sensitive to the activation of the specific marking and located at or in the tunnel, detects the marking on the item. If the activated marking is not detected by the detector, an alert condition is triggered.

Owner:TOSHIBA GLOBAL COMMERCE SOLUTIONS HLDG

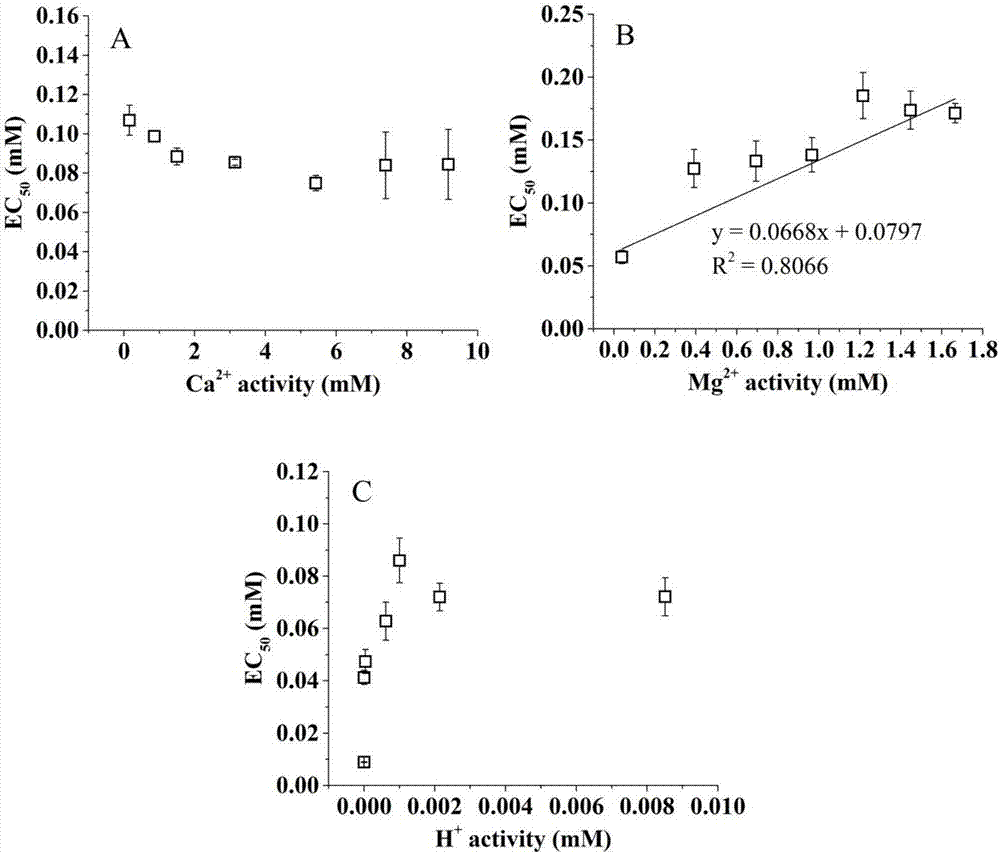

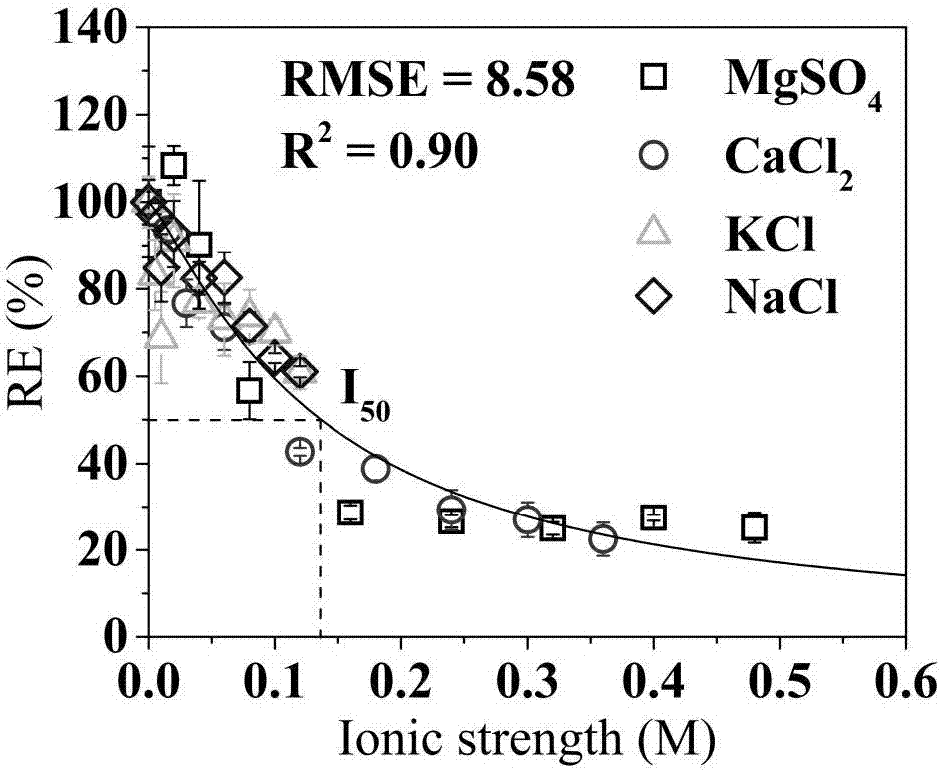

Method for predicting wheat root elongation toxicity of nickel ions in soil, and application thereof

InactiveCN106932538ASolve problems that cannot be accurately predictedValid and reliable toxicity parametersTesting plants/treesAir quality improvementSoil typeSoil heavy metals

The invention discloses a method for predicting wheat root elongation toxicity of nickel ions in soil, and an application thereof, and belongs to the field of ecological heavy metal toxicity assessment. According to the method disclosed by the invention, the toxicity competitive inhibition effect of Ca<2+> and other cations on the nickel ions is considered, the influence of the osmotic pressure effect in soil conditions to the toxicity is corrected, and meanwhile the toxic effect of nickel is calculated by obtaining the activity of the nickel ions by using the visual MINTEQ program. Firstly, biological toxicity suppression parameters of the cations to the nickel ions, and the toxic effect parameters and the osmotic pressure parameters of the nickel are determined under a sand culture condition, the obtained parameters can be applied to the prediction of the wheat root toxicity of the nickel ions under different soil types, and the method is also applicable to predicting the root elongation toxicity of nickel ions to other crops and can provide reference for soil heavy mental ecological risk assessment and soil pollution abatement.

Owner:NANJING UNIV

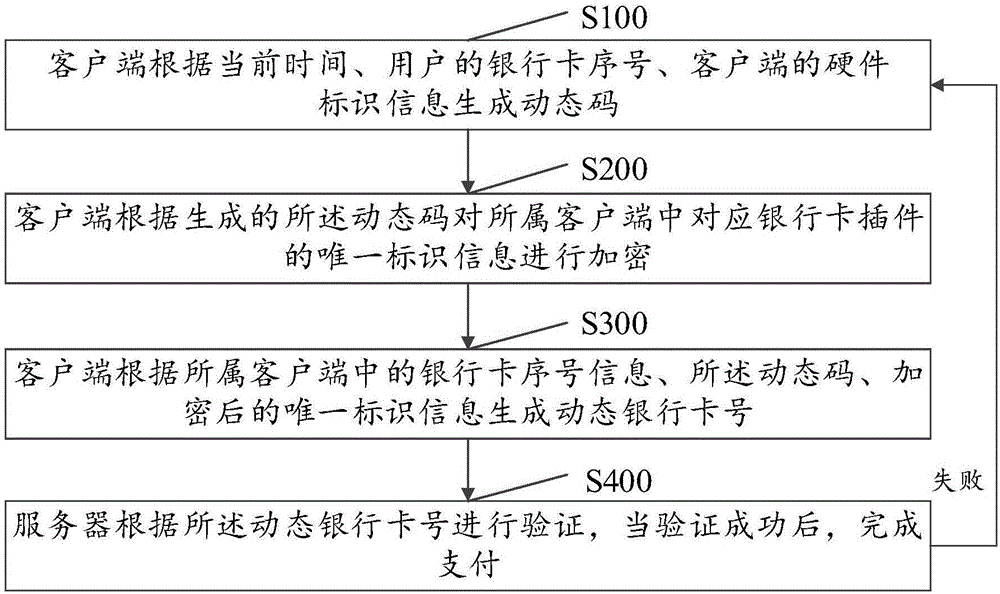

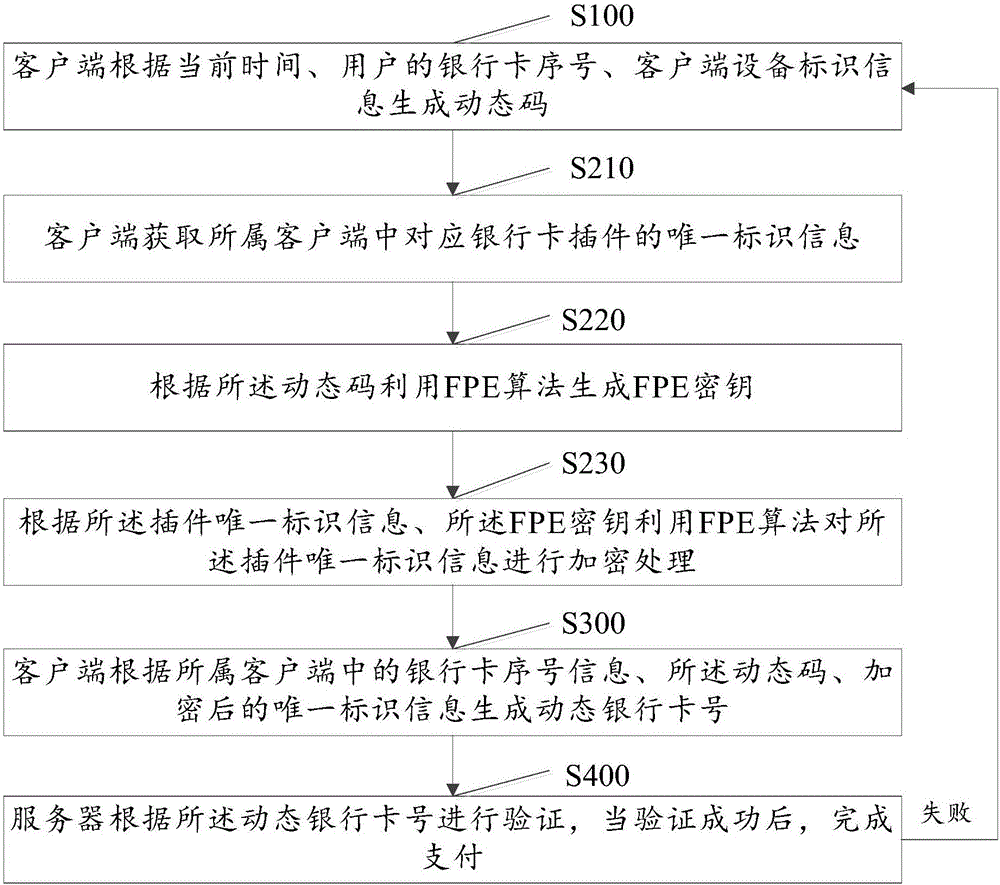

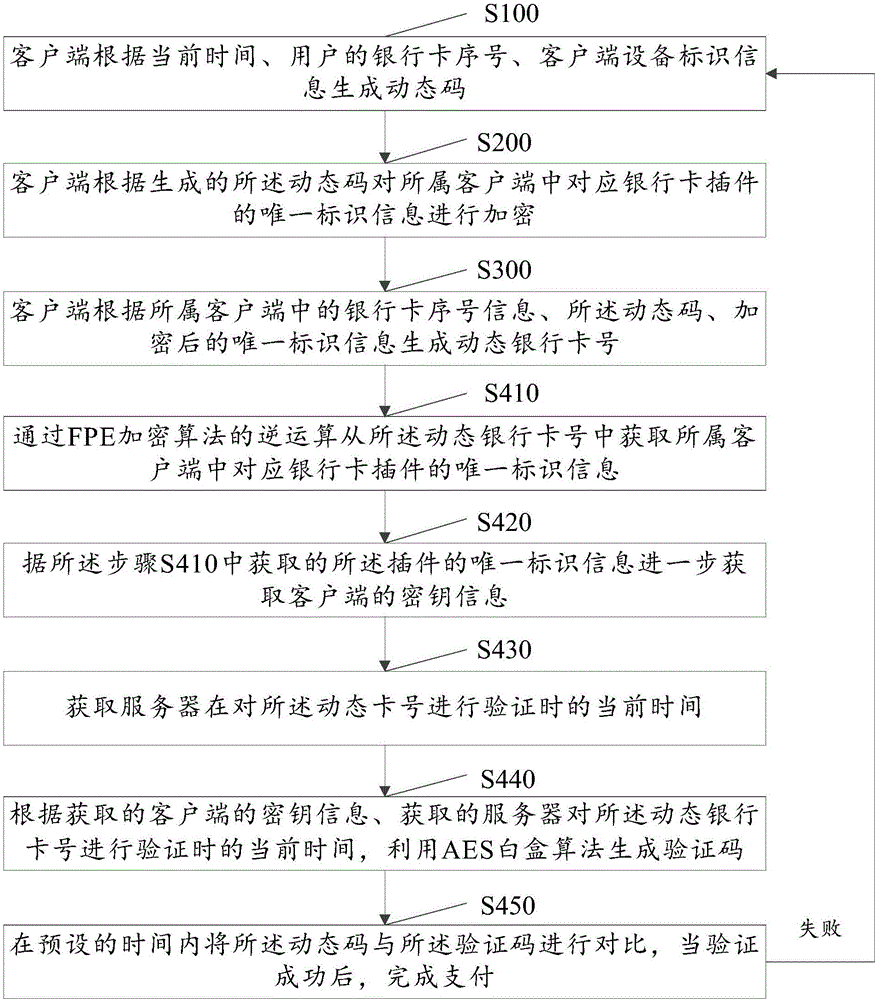

Dynamic payment method and system

The invention discloses a dynamic payment method and system. The method comprises the steps that S100, a client generates a dynamic code according to current time, a bank card serial number of a user and device identifier information of a client; S200, the client encrypts unique identifier information corresponding to a bank card plug-in in the client according to the generated dynamic code; S300, the client generates a dynamic bank card number according to the bank card serial number information in the client, the dynamic code and the encrypted unique identifier information in the step S200; and S400, a server performs verification according to the dynamic bank card number, and finishes payment when the verification succeeds, otherwise, returns to and executes the step S100. The purpose of the method is to generate the dynamic bank card number, and an offline authentication mode is adopted, so that the payment efficiency is improved and the use convenience is brought for users.

Owner:SHANGHAI PEOPLENET SECURITY TECH

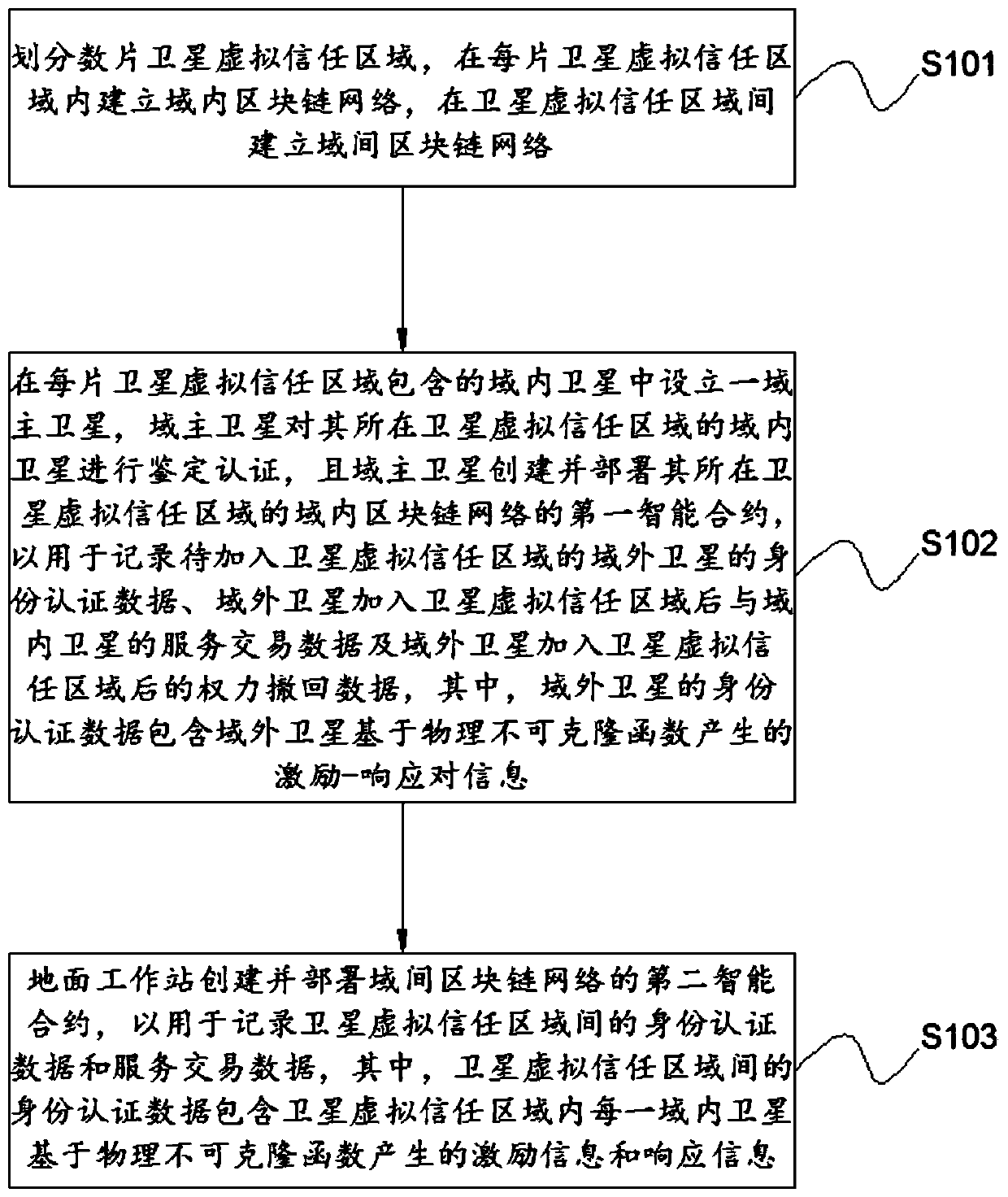

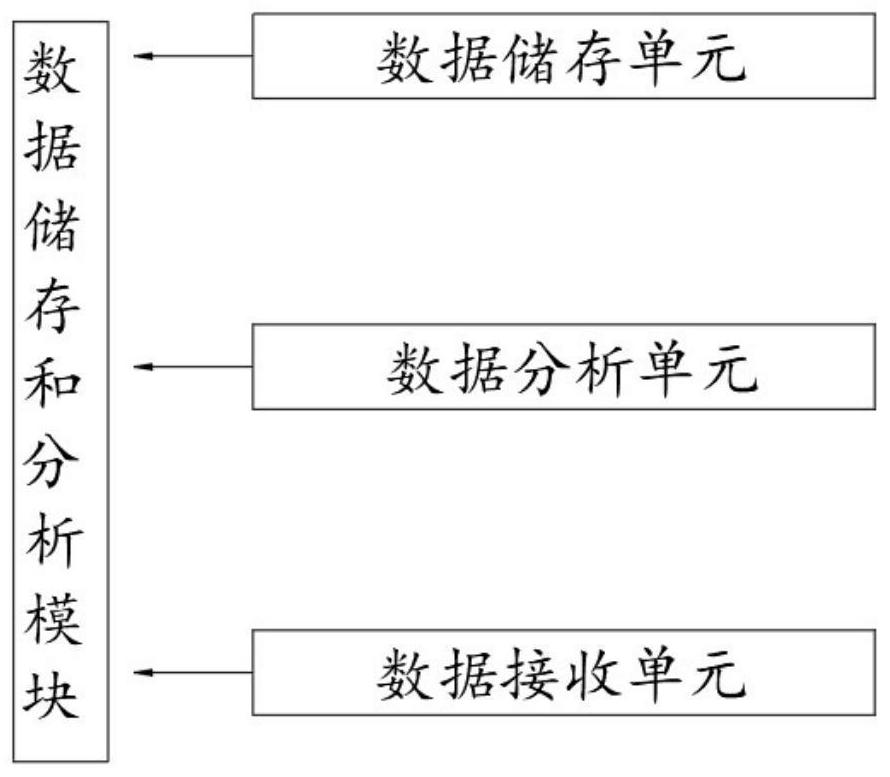

Satellite management method based on blockchain and physical unclonable function

ActiveCN111200500AAvoiding Zero Trust ProblemsThe certification process is reliableFinanceUser identity/authority verificationData domainEngineering

The invention discloses a satellite management method based on a blockchain and a physical unclonable function. The method comprises the steps of dividing a plurality of satellite virtual trust regions, building an intra-domain blockchain network in each satellite virtual trust region, and building an inter-domain blockchain network between the satellite virtual trust regions; setting a domain main satellite in intra-domain satellites contained in each satellite virtual trust area; enabling the domain main satellite to create and deploy a first intelligent contract of the intra-domain block chain network so as to record identity authentication data of an out-domain satellite to be added into the satellite virtual trust area, service transaction data of the out-domain satellite and the intra-domain satellite and power withdrawal data of the out-domain satellite; and enabling a ground workstation to create and deploy a second smart contract of the inter-domain blockchain network so as torecord identity authentication data and service transaction data between the satellite virtual trust areas. According to the method, the performance defects of a traditional satellite network can beovercome, and better safety performance can be obtained.

Owner:GUANGXI UNIV +1

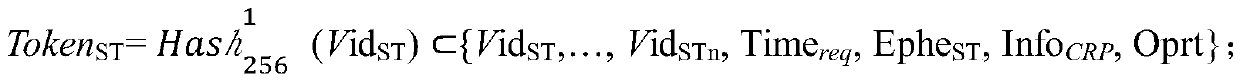

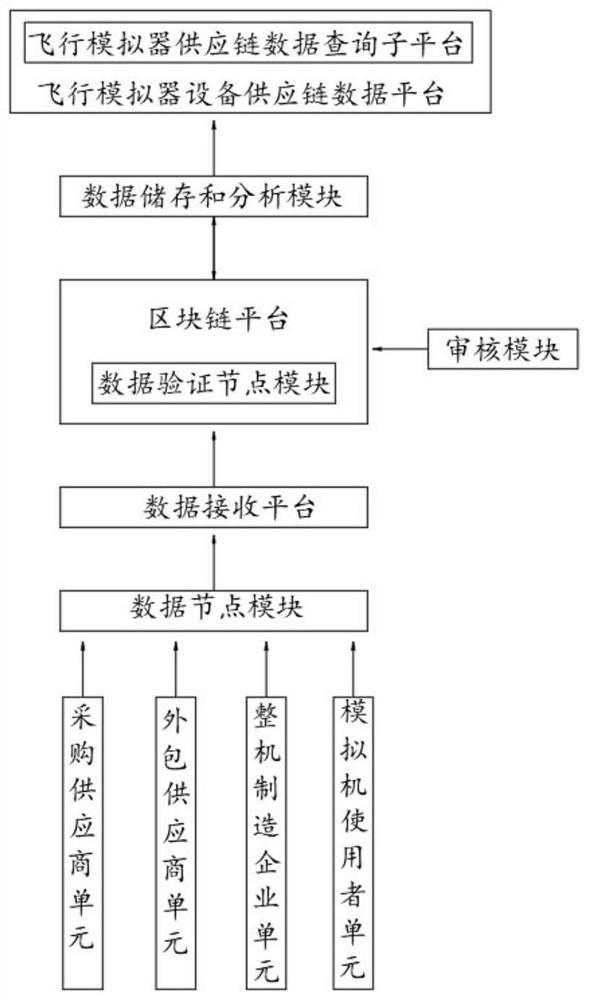

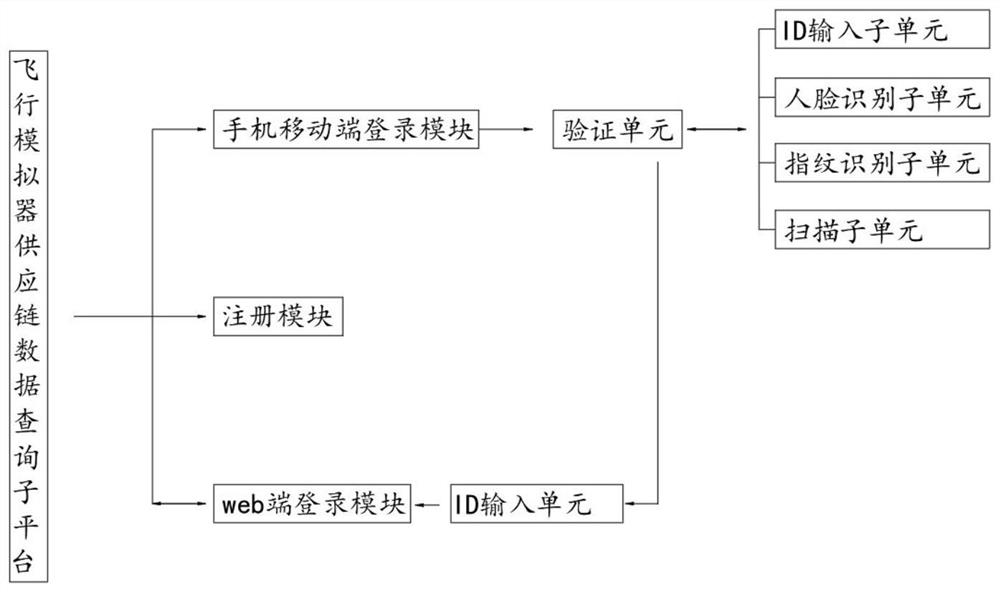

Flight simulator equipment supply chain system based on block chain

PendingCN114491483AEnsure safetyIntelligent Supply Chain ManagementDatabase management systemsDatabase distribution/replicationData platformSource Data Verification

The invention discloses a flight simulator equipment supply chain system based on a block chain, which comprises a flight simulator equipment supply chain data platform, a block chain platform and a data receiving platform, and is characterized in that the flight simulator equipment supply chain data platform and the block chain platform are jointly connected with a data storage and analysis module; the block chain platform is connected with a data verification node module, the data receiving platform is connected with the data verification node module, the data receiving platform is connected with a data node module, and the data node module comprises a purchase supplier unit, an outsourcing supplier unit, a complete machine manufacturing enterprise unit and an analog machine user unit. According to the invention, a complete honesty system is established based on the block chain, so that the data is more transparent, the evidence is more complete, traceable and verifiable, accurate identification and data verification query can be carried out on the full-life-cycle record of the outsourcing processed or purchased equipment parts, and intelligent flight simulator equipment part supply chain management can be realized.

Owner:安胜(天津)飞行模拟系统有限公司

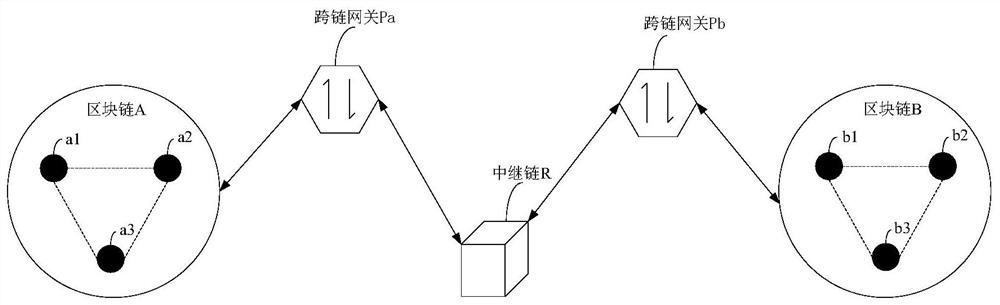

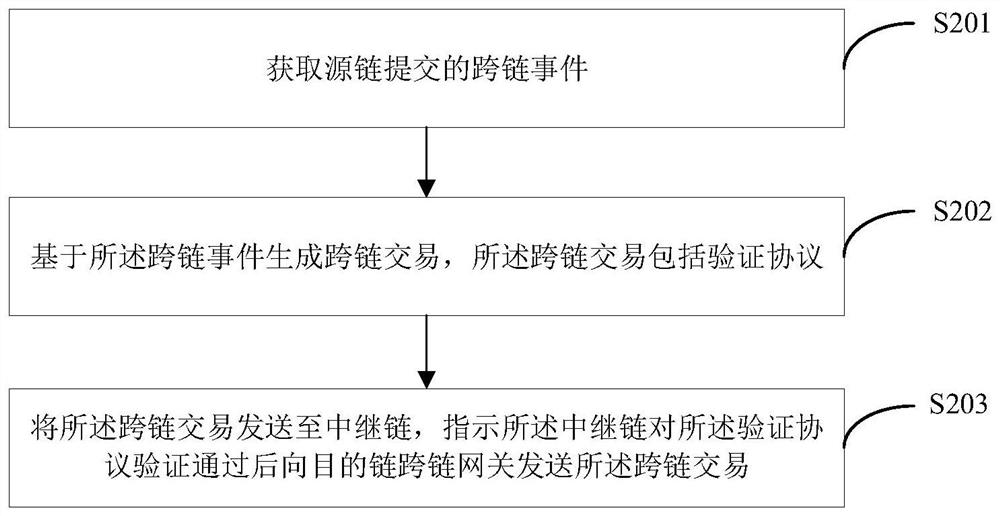

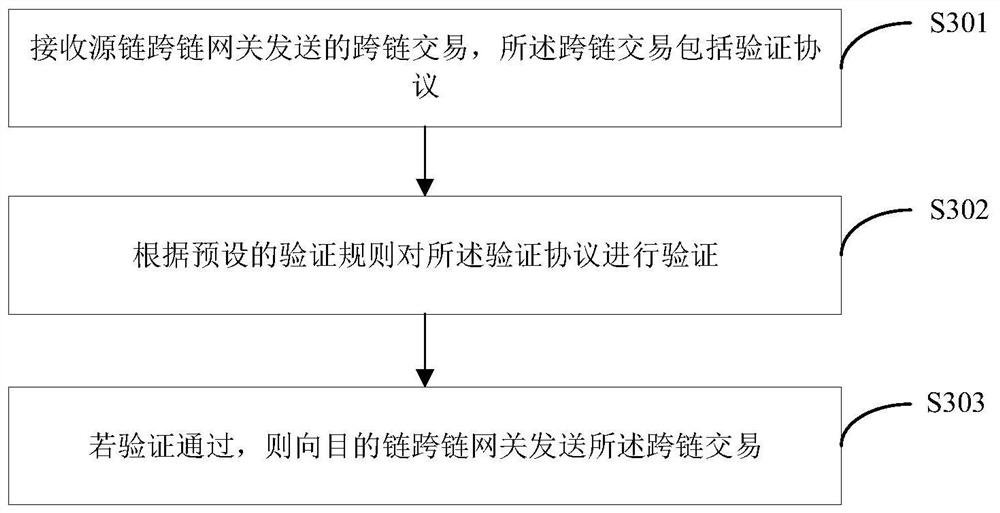

Cross-chain transaction verification method, terminal equipment and readable storage medium

ActiveCN112822181AVerified and reliableEase of useUser identity/authority verificationDigital data protectionTrunkingOperating system

The invention is suitable for the technical field of computer application, and provides a cross-chain transaction verification method, terminal equipment and a readable storage medium; the method comprises the steps: obtaining a cross-chain event submitted by a source chain; generating a cross-chain transaction based on the cross-chain event, wherein the cross-chain transaction comprises a verification protocol; and sending the cross-chain transaction to a relay chain, and indicating the relay chain to send the cross-chain transaction to a target chain cross-chain gateway after verification of the verification protocol is passed. According to the embodiment of the invention, the cross-chain transaction is sent to the relay chain, and the relay chain is indicated to only verify the verification protocol in the cross-chain transaction, so that the problem that the processing burden of the cross-chain gateway is increased due to the fact that the cross-chain gateway of the target chain verifies the cross-chain transaction at present can be solved on the premise of ensuring privacy.

Owner:HANGZHOU QULIAN TECH CO LTD

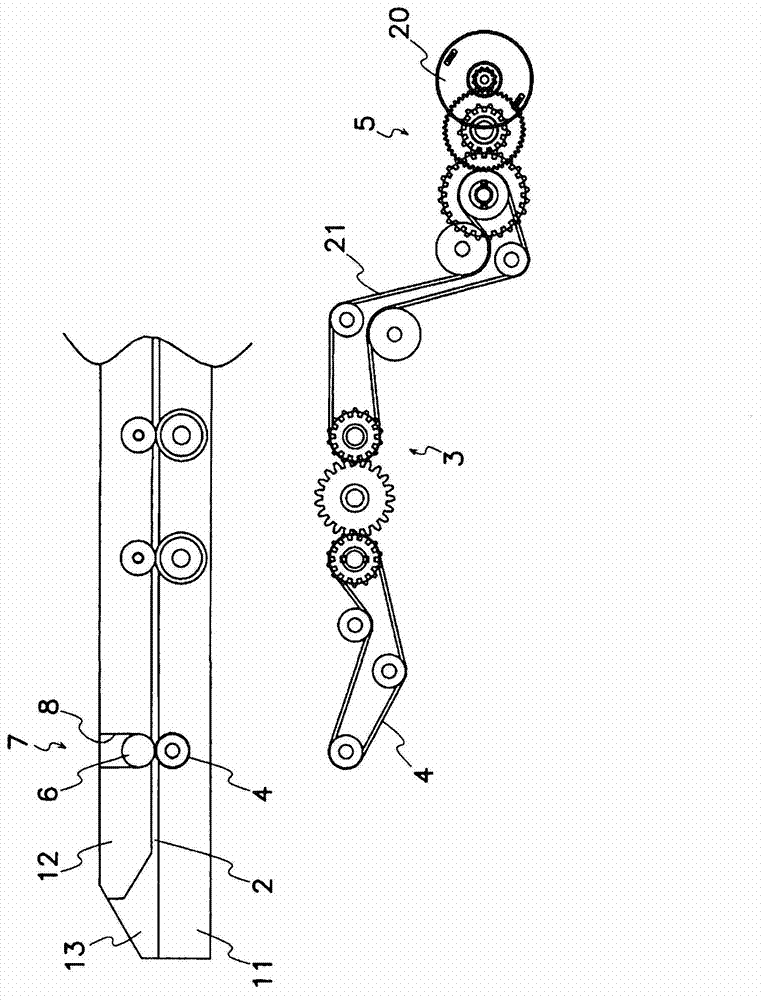

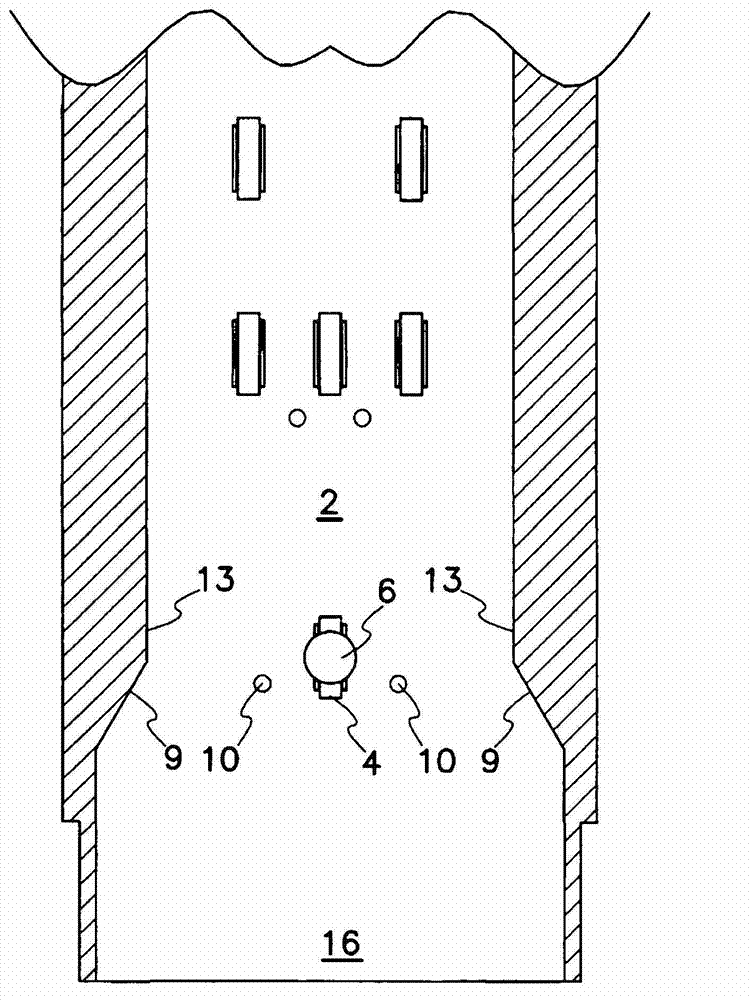

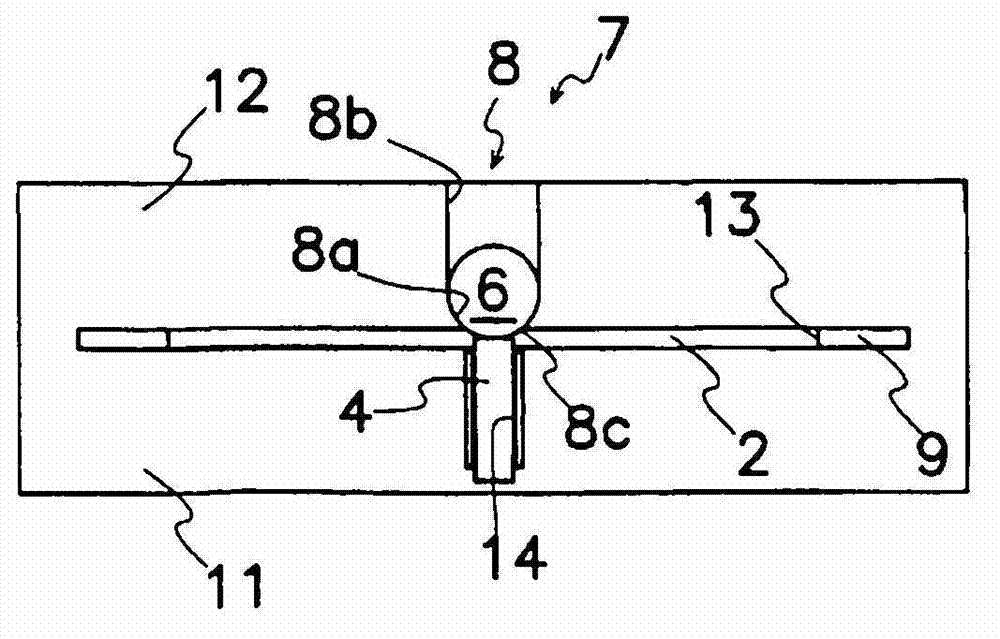

Document transporter

InactiveCN103025635ASimple structureAutomatic alignmentRegistering devicesArticle feedersPaper documentDocument preparation

A document transporter has a roller or conveyor belt (4) for driving a bill (1) and a weighting device (7) for pressing the bill (1) against the roller / belt (4). The weighting device (7) includes a ball (6) weighting the bill (1) and a holder (8) rotatably holding the ball (6). The device (7) may further include a spring (15) pressing the ball (6) against the roller / belt (4). The passageway (2) into which the bill (1) is inserted is enclosed by a bottom wall (11), a top wall (12) and side walls (13). The side walls (13) have tapered surfaces (9) at the inlet (16) to the passageway (2). A pair of guide rollers (22) rotatably mounted on the side walls (13) guides the bill (1) by engaging the side edges of the bill (1). The bill (1) fed to the transporter is automatically centered.

Owner:JAPAN CASH MASCH CO LTD

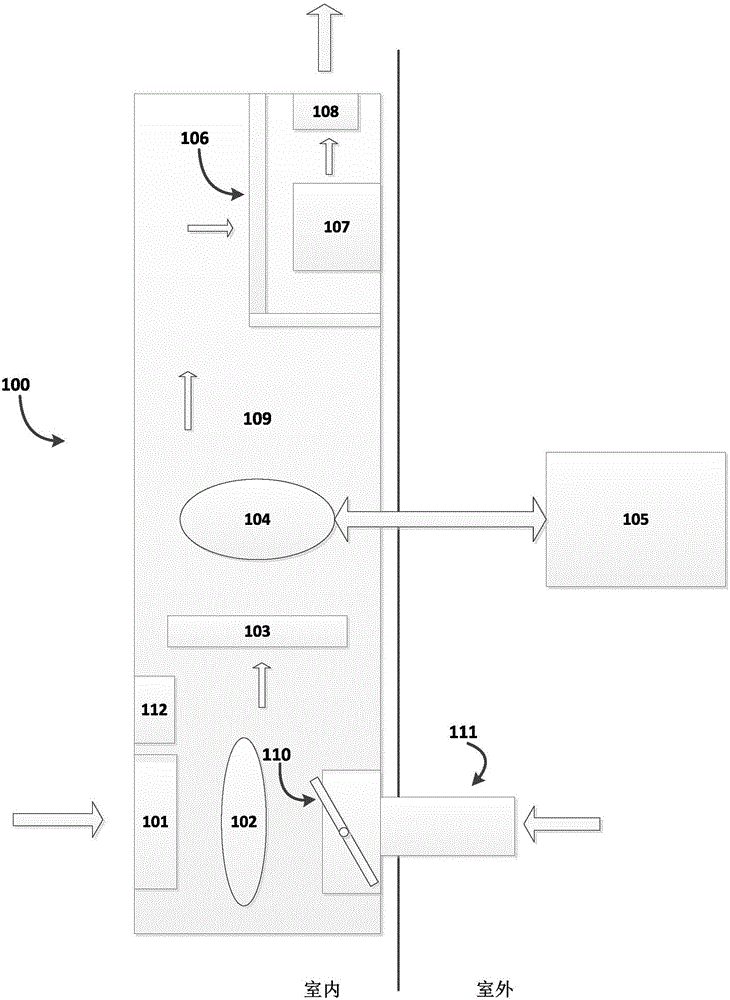

Fresh air purification system with remote control function

ActiveCN106016569ALow powerReduced Power RequirementsMechanical apparatusSpace heating and ventilation safety systemsAir filtrationAir volume

The invention relates to a fresh air purification system with a remote control function. The fresh air purification system with the remote control function comprises an air inlet device which is provided with an air inlet and an axial flow fan, an air outlet device which is provided with an air outlet and a centrifugal fan, an air duct connecting the air inlet device with the air outlet device and used for guiding air between the air inlet device and the air outlet device, an air filtering device arranged in the air duct and used for filtering air, a fresh air device opposite to the air inlet and comprising a multipurpose air port and an air amount adjusting plate rotationally arranged in the multipurpose air port, and a remote control device configured to receive a remote control command from a user. By means of the fresh air purification system, noise can be reduced, heat can be dissipated, the fresh air amount is flexibly adjusted between zero fresh air and pure fresh air, and the fresh air purification system is further allowed to be remotely controlled.

Owner:中科朗劢技术有限公司

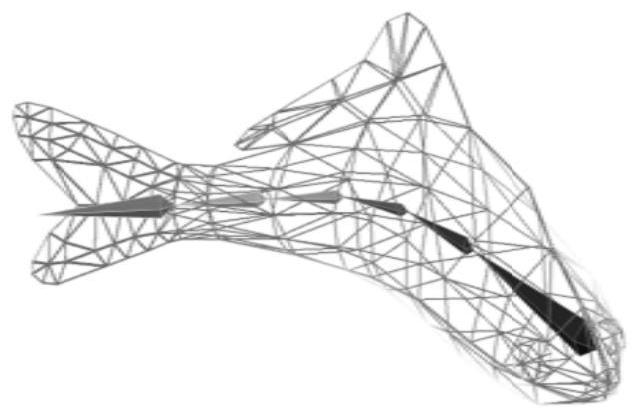

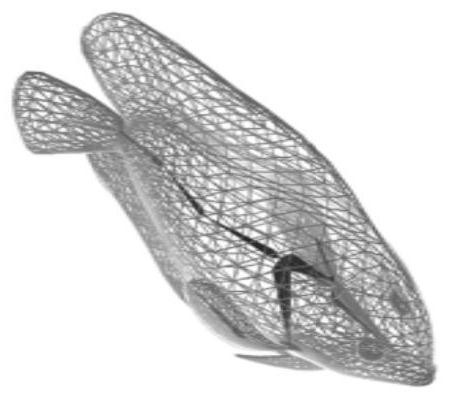

Physics-based high-performance bionic underwater robot simulation training platform construction method

PendingCN114792028ASave storage spaceImprove computing efficiencyGeometric CADDesign optimisation/simulationPhysicsFluid solid coupling

The invention provides a physics-based high-performance bionic underwater robot simulation training platform construction method which can be used for training a fish-shaped underwater robot. The platform is composed of a robotic fish modeling module using a joint body with skin, a GPU-based high-performance local bidirectional fluid-solid coupling simulation module (capable of processing a finite field and an infinite field), and a reinforcement learning module. A plurality of bionic robot models are provided, a series of underwater reference control tasks are formulated, and an existing reinforcement learning training method is applied to obtain a corresponding control strategy. According to the method, high-performance fluid simulation requirements of a finite domain and an infinite domain can be processed, a model of any bionic underwater robot can be built, an underwater control task can be customized, and intelligent strategy training, migration and integration can be realized.

Owner:SHANGHAI TECH UNIV

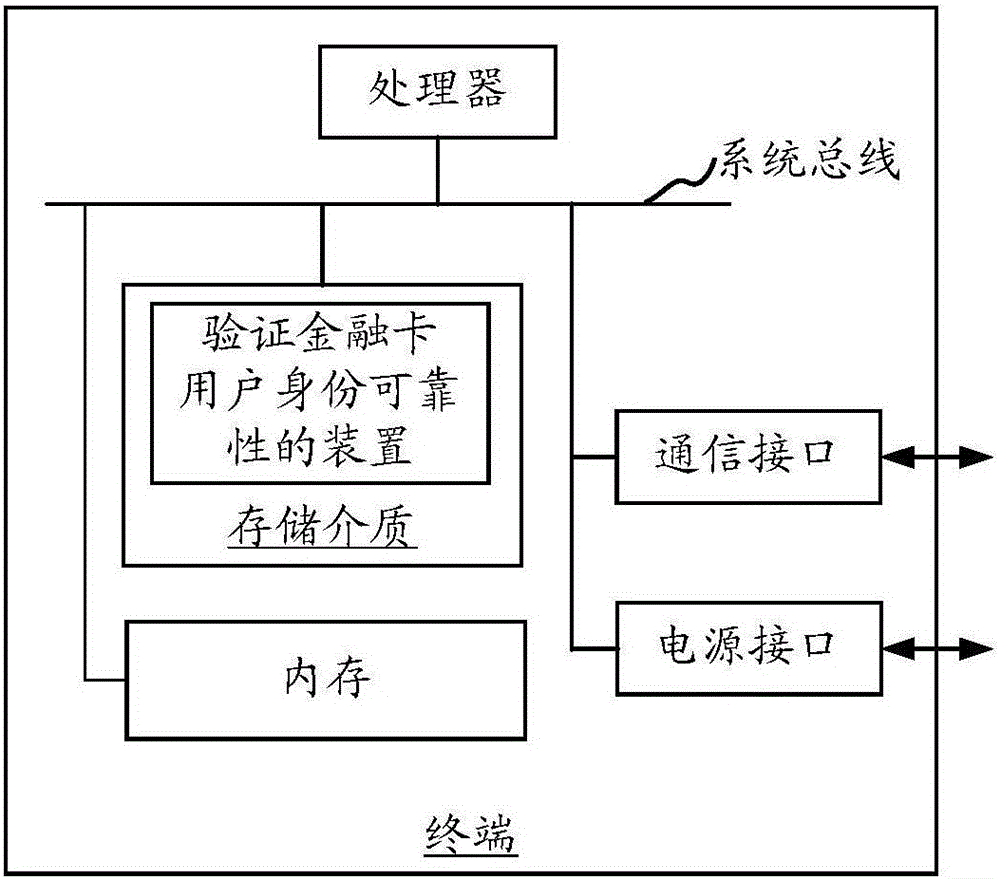

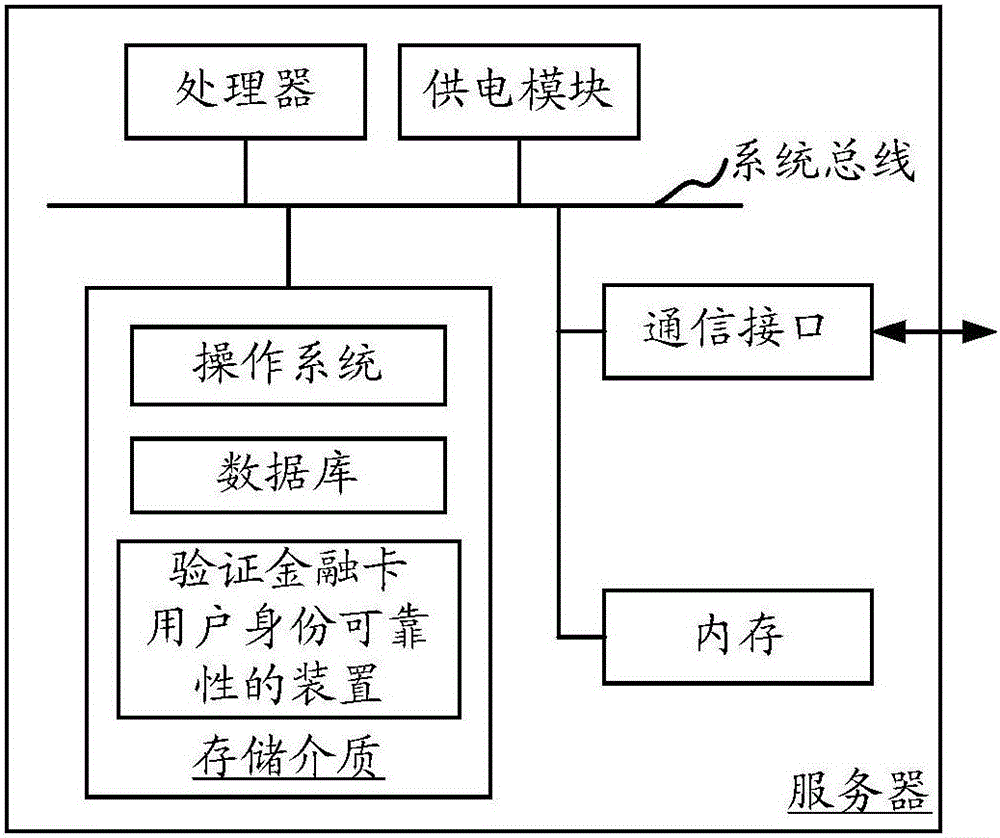

Method and device for verifying reliability of identity of financial card user

ActiveCN105897721AAvoid security risksProtection securityTransmissionProtocol authorisationInternet privacyCiphertext

The invention provides a method and device for verifying reliability of an identity of a financial card user. The method comprises the steps that response data required by a financial card is sent to the financial card; interactions are implemented to the financial card, so that card number information and ciphertext response information of first application ciphertext are obtained; transaction password information input by the user is received; the ciphertext response information, the transaction password information and the response data are sent to a card issuer server; interactions are carried out to the card issuer server, so that a first authentication result and first authentication data are obtained; the first authentication data is sent to the financial card; a second authentication result is obtained after verification of the financial card based on the first authentication data; and legality of the user identity is determined according to the first authentication result and the second authentication result. The scheme provided by the embodiment of the invention has the advantages that the verification of the user identity and issuance can be carried out conveniently, rapidly and reliability without use of extra hardware equipment; safety ricks caused by frauds are avoided; and information safety is protected.

Owner:GRG BAKING EQUIP CO LTD

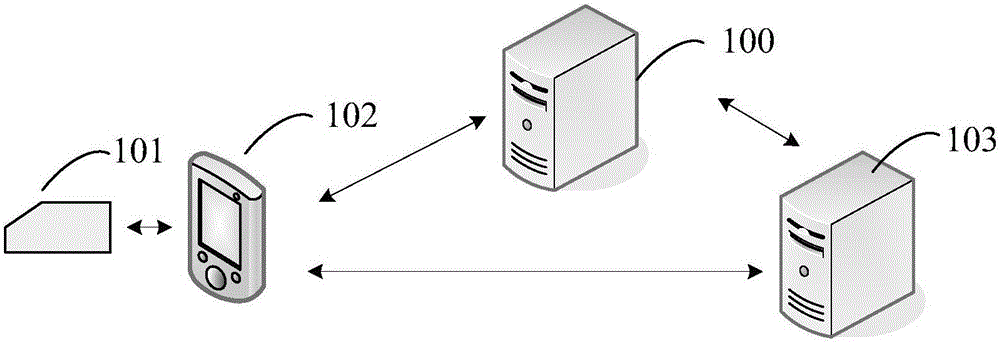

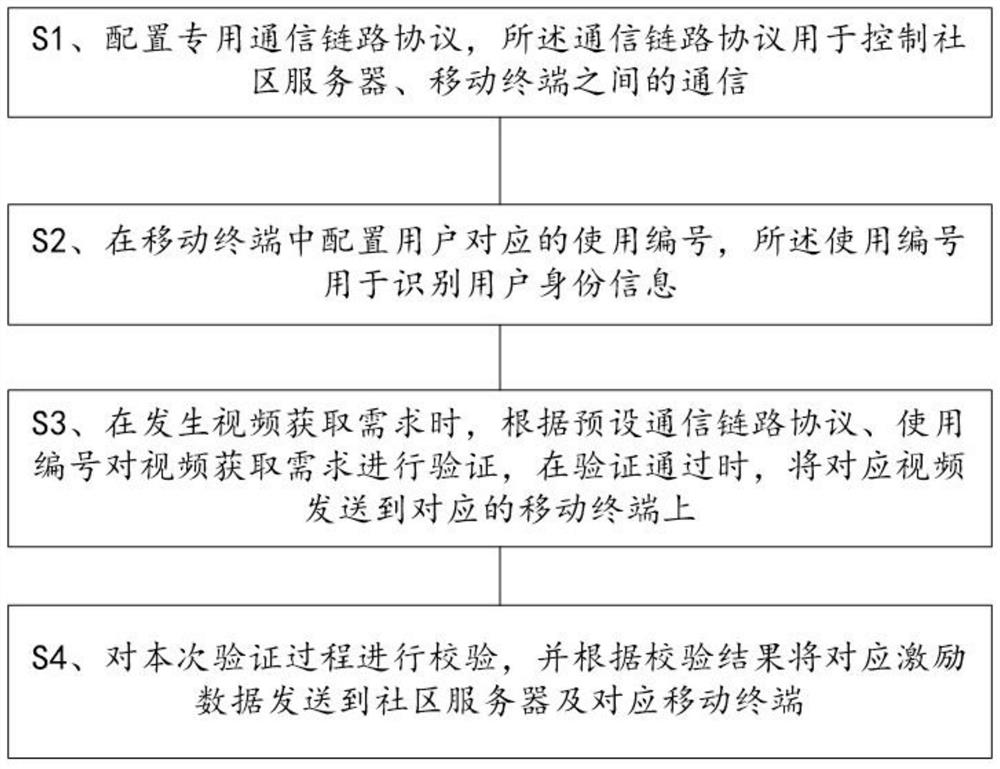

Smart community security and protection method based on Internet of Things

ActiveCN111918027APersonal privacy is not disclosedIncrease motivationDigital data protectionClosed circuit television systemsTelecommunications linkInternet privacy

A smart community security and protection method based on the Internet of Things is characterized by comprising the following steps that S1, configuring a special communication link protocol and the communication link protocol is used for controlling communication between a community server and a mobile terminal; S2, configuring a use number corresponding to the user in the mobile terminal, wherein the use number is used for identifying user identity information; S3, when a video acquisition demand occurs, verifying the video acquisition demand by using the serial number according to a presetcommunication link protocol, and sending the corresponding video to the corresponding mobile terminal when the verification is passed; and S4, verifying the verification process, and sending the corresponding excitation data to the community server and the corresponding mobile terminal according to the verification result.

Owner:杭州齐圣科技有限公司

Evaluation of dose accuracy of radiation therapy treatment plans

ActiveUS20190143147A1Reduce in quantityVerified and reliableMechanical/radiation/invasive therapiesX-ray/gamma-ray/particle-irradiation therapyMass parameterPlanned Dose

The invention relates to a system and a method for evaluating a treatment plan for an external radiation therapy treatment, the treatment plan comprising parameters for controlling an external radiation therapy apparatus during the treatment. The system comprises a database storing historic treatment plans and storing for each historic treatment plan a quality parameter indicative of whether a deviation between a planned dose distribution and a measured dose distribution resulting from an execution of the treatment plan is within an acceptable limit. An evaluation unit determines a threshold value for each of a plurality of treatment plan metrics based on the historic treatment plans and the associated quality parameters. Further, the evaluation unit calculates a value of each of the metrics for the treatment plan and compares the value of each of the metrics with the threshold value determined for the respective metric.

Owner:KONINKLJIJKE PHILIPS NV

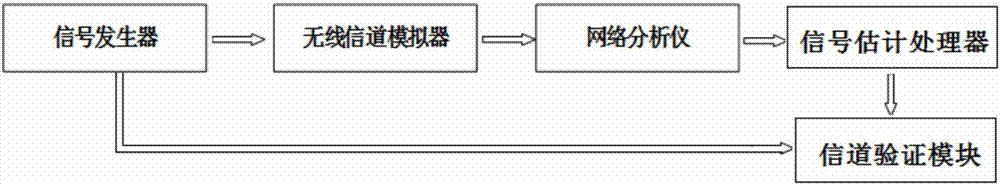

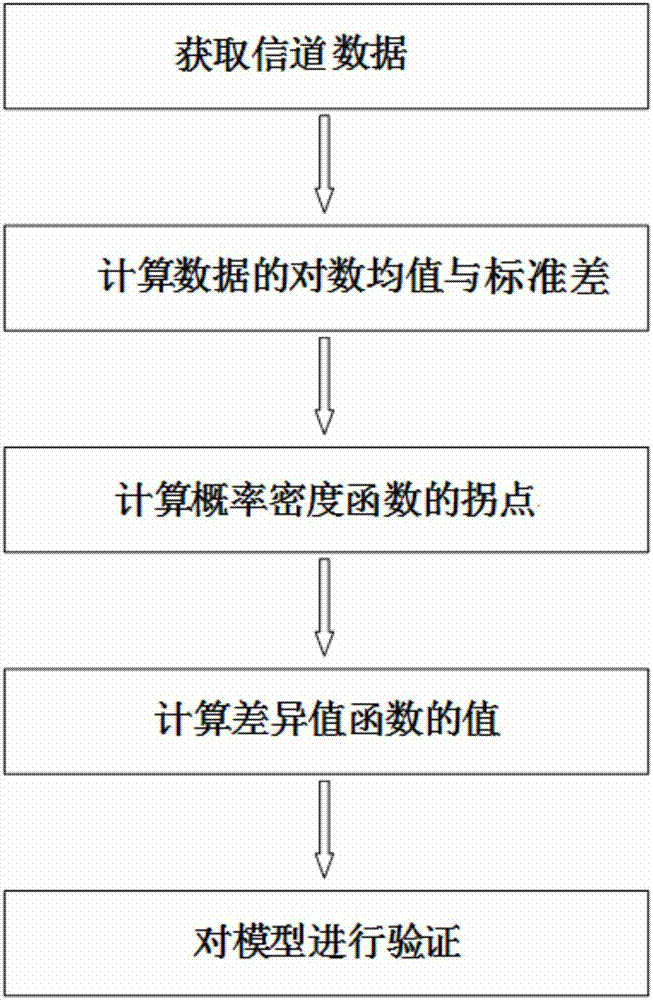

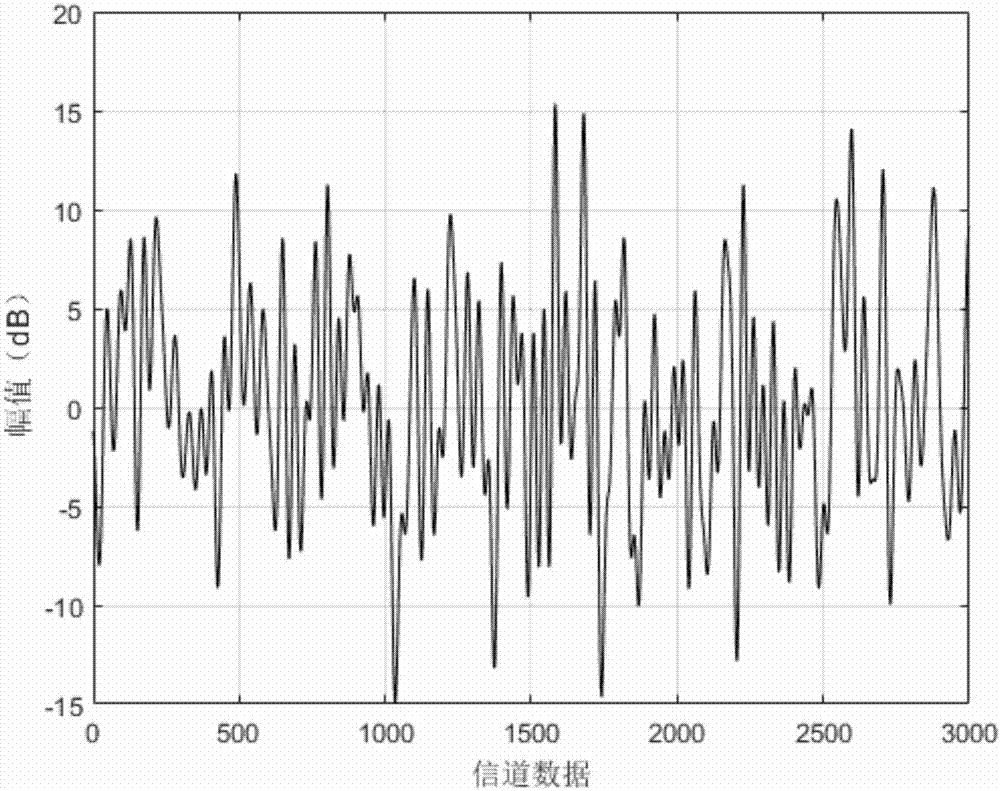

Lognormal channel model verification system

ActiveCN107994965AConvenient verificationVerified and reliableTransmission monitoringChannel dataSignal generator

The invention discloses a lognormal channel model verification system, comprising a signal generator, a wireless channel simulator, a network analyzer, a channel estimation processor and a channel verification module. The signal generator, the wireless channel simulator, the network analyzer, the channel estimation processor and the channel verification module are unidirectionally connected in sequence. The signal generator is also directly and unidirectionally connected with the channel estimation processor. The signal generator, the wireless channel simulator, the network analyzer and the channel estimation processor are mainly used for acquiring channel data. The channel verification module is mainly used for verifying the acquired channel data. According to the system, the channel datagenerated by the channel simulator submits to lognormal distribution or not can be judged conveniently and simply, whether a lognormal channel simulator model is accurate or not is effectively verified, the foundation for the channel research such as channel estimation is laid, and the guarantee for a receiving end to extract sending data accurately and effectively is provided.

Owner:HEFEI UNIV OF TECH

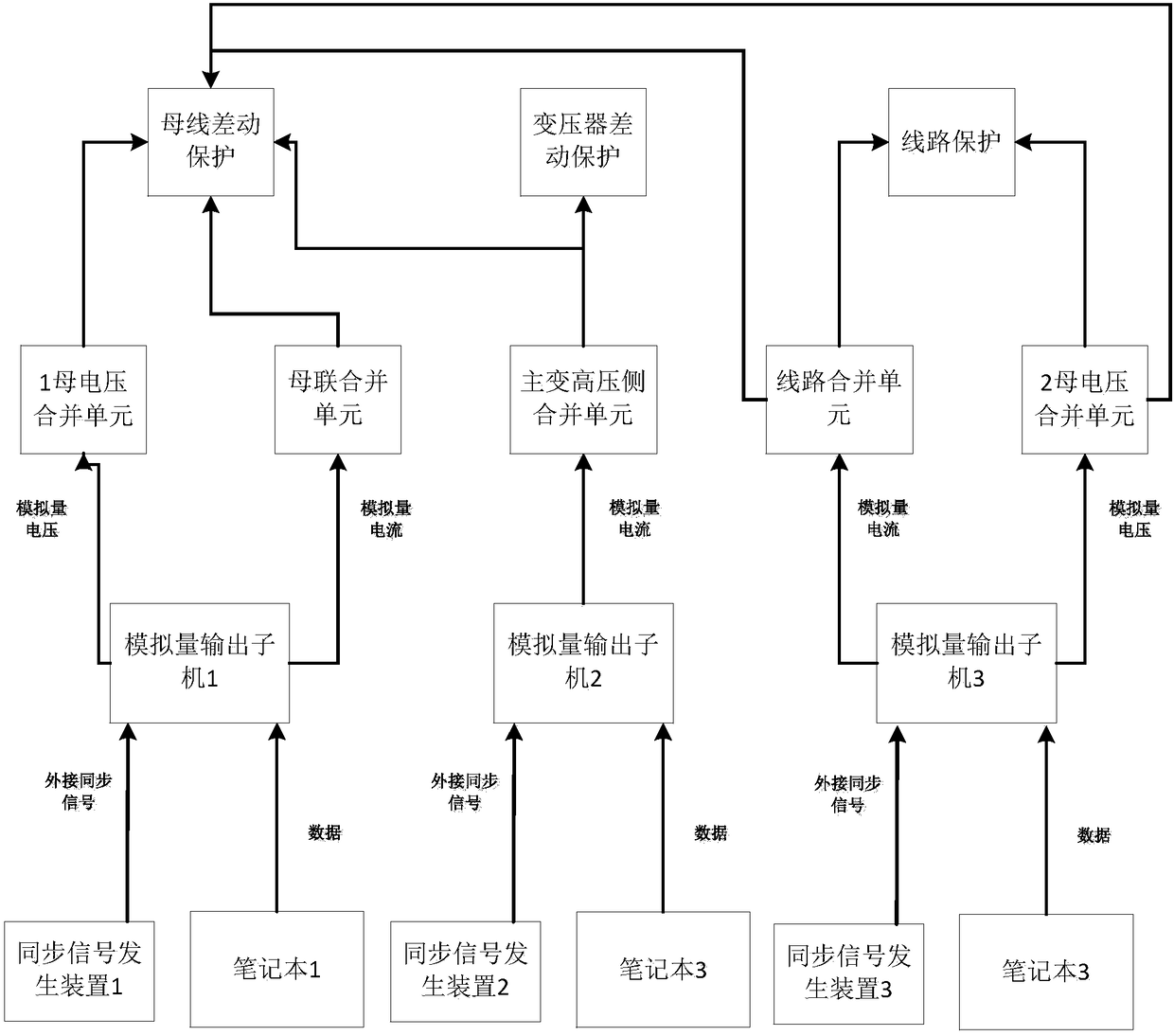

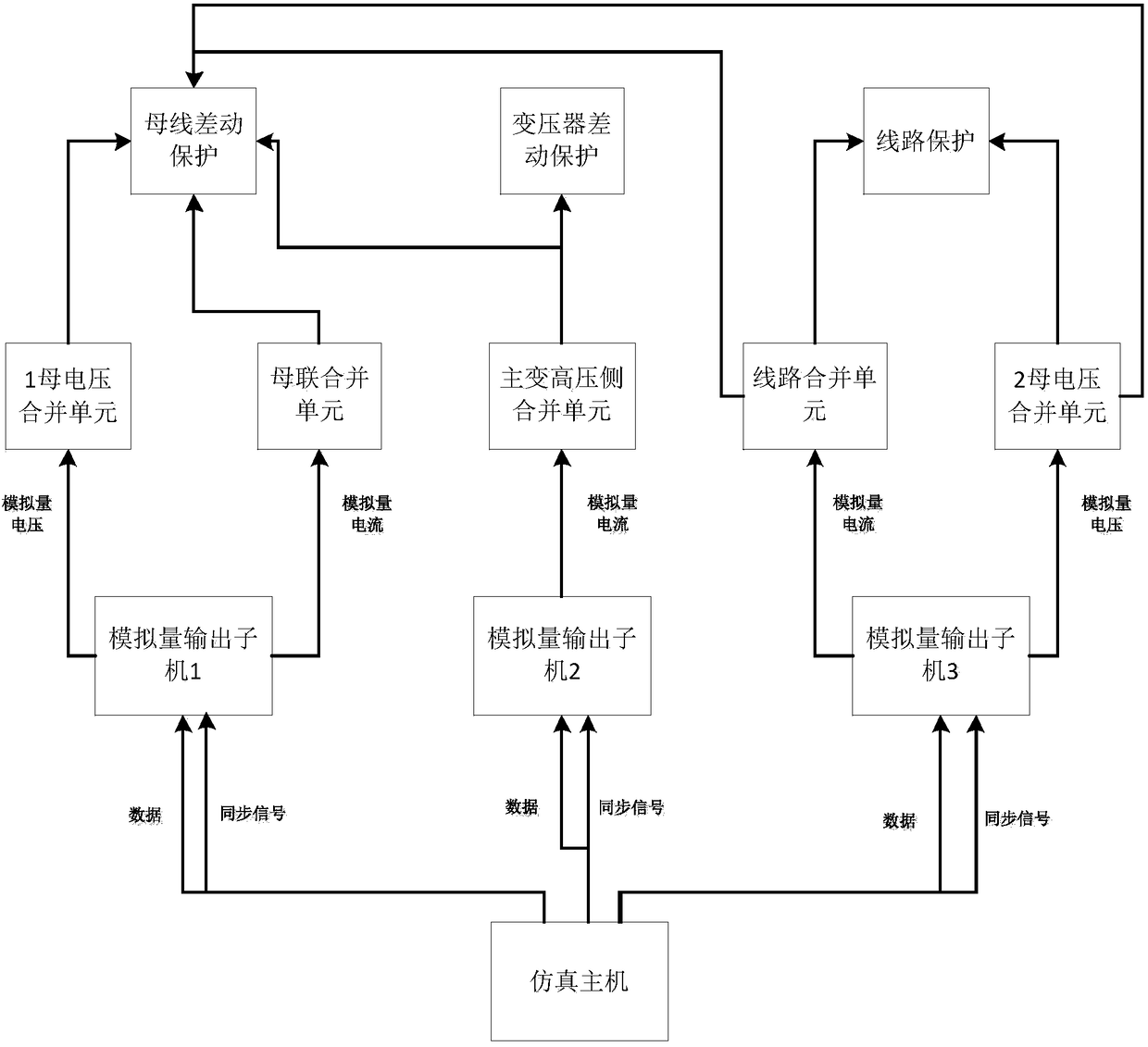

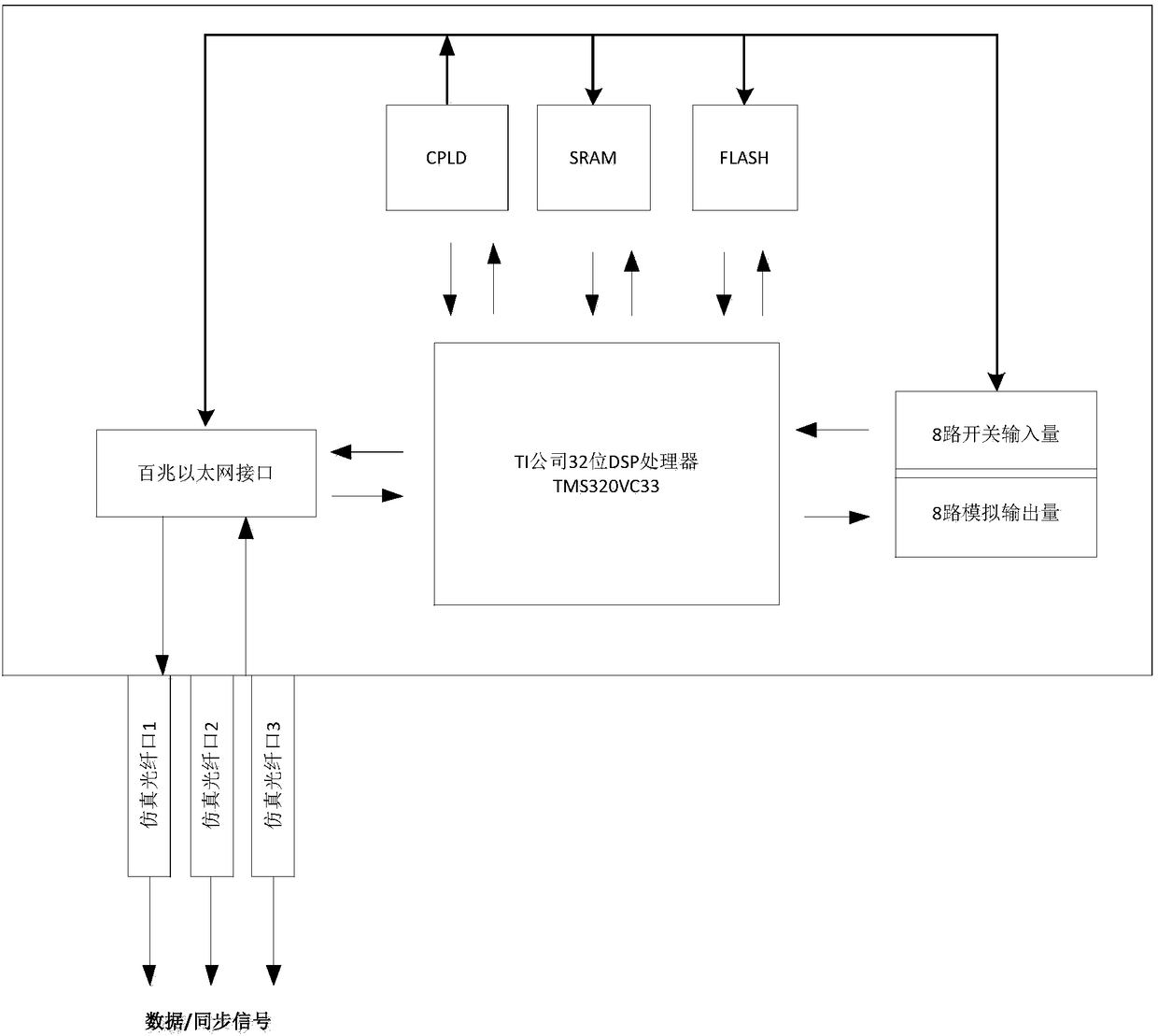

Synchronous control method based on distributed simulation testing of transformer substation

The invention discloses a synchronous control method based on distributed simulation testing of a transformer substation. A testing system utilizes DSP technology for performing simulation testing onaction logic between a fault point and a protecting device thereof in a power line. The testing system comprises a simulating host computer and analog amount output sub-computers. The simulating hostcomputer is connected with the analog amount output sub-computers through fibers. According to a testing method which is utilized in the invention, before a plurality of analog amount output sub-computers in front of combining unit devices with different intervals, the simulating host computer is utilized for performing long-distance synchronous controlling of simulated output through the fibers;adding testing is simultaneously performed on a plurality of combining units; a Goose signal returned from the protecting device through action can be received and a switching amount action node can be received for realizing closed-loop testing; joint debugging of an intelligent power grid system is realized; and the working condition of a total-station system in real operation is truly reflected.

Owner:STATE GRID CORP OF CHINA +1

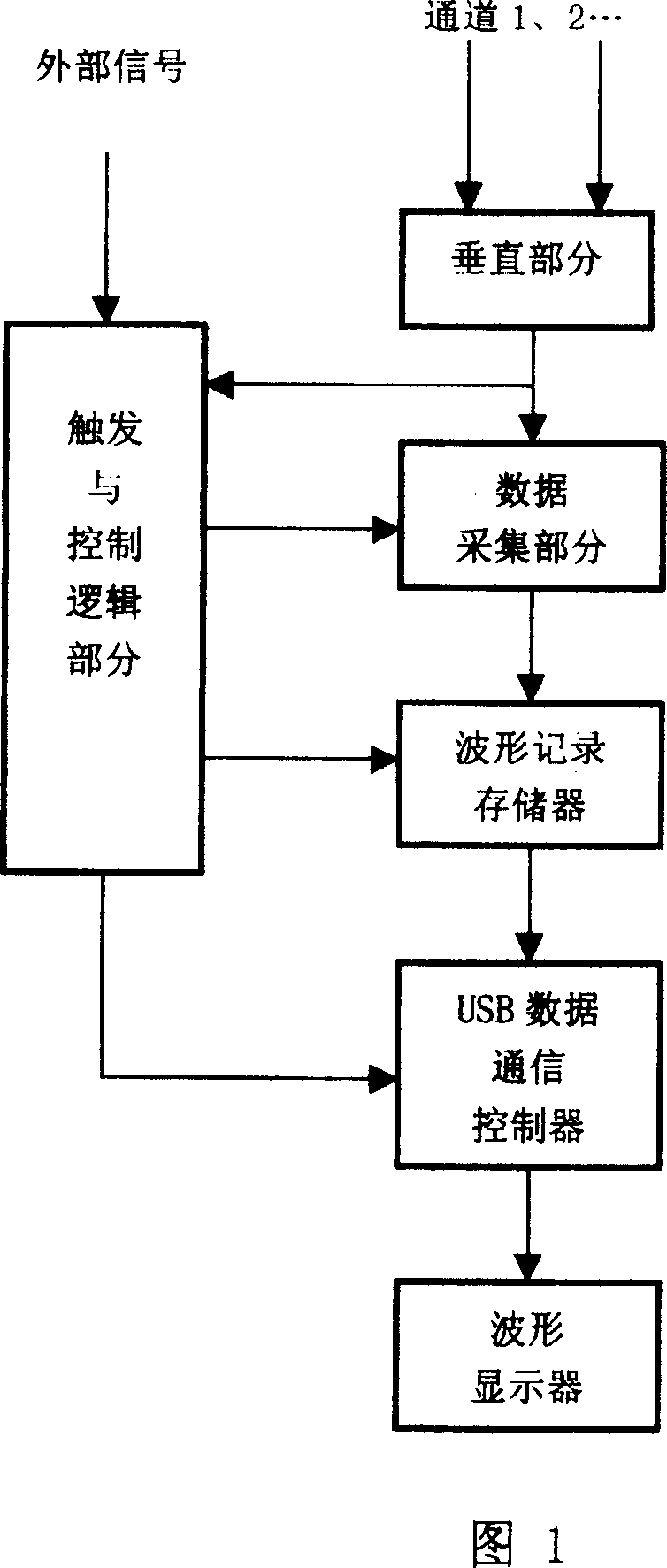

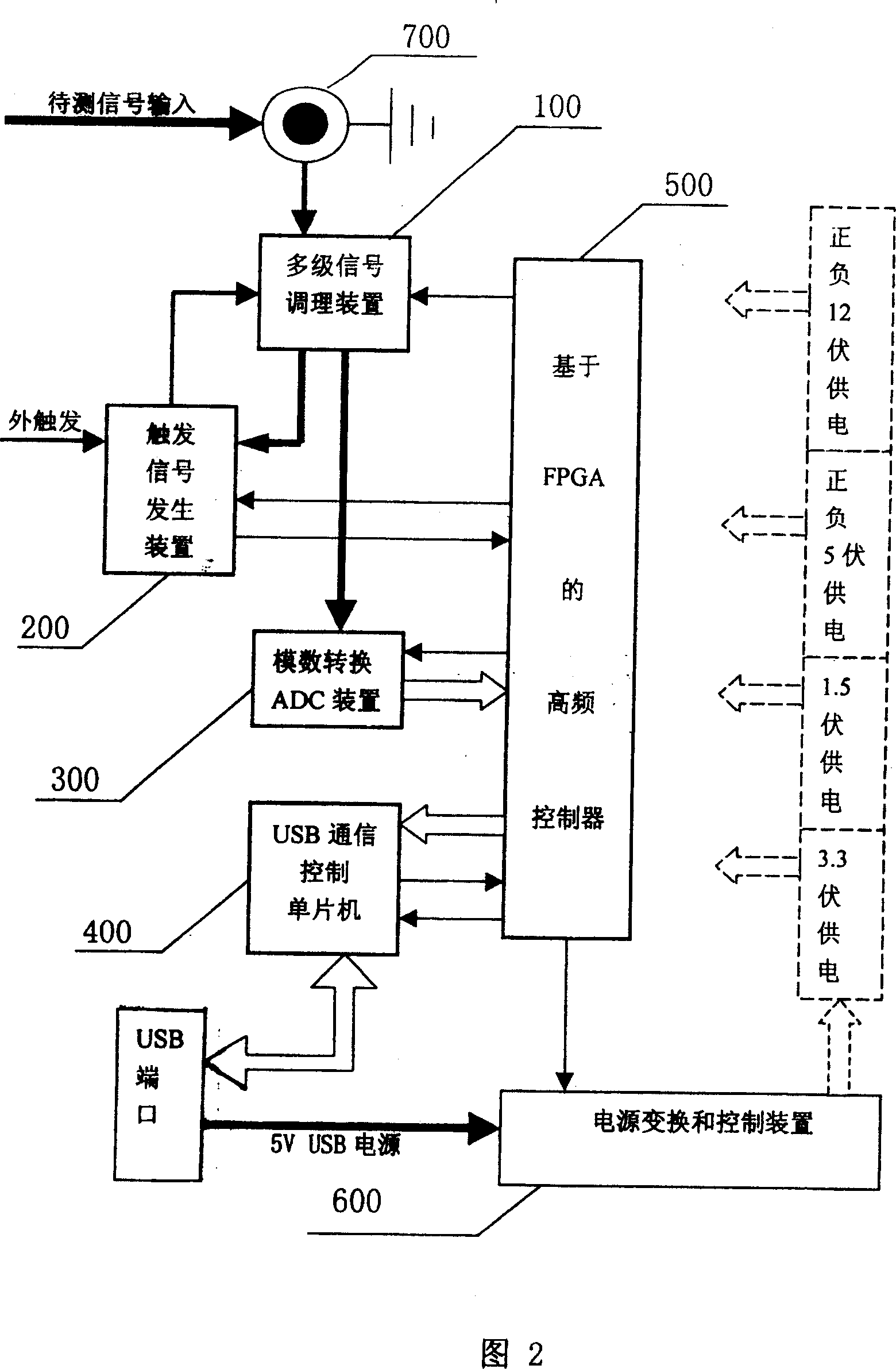

Palm sized universal oscillograph with USB bus power supply

InactiveCN100362352CFlexible combinationReduce volumeCathode-ray oscilloscopesMicrocontrollerMeasuring instrument

A portable univerval oscillascope consists of multistage signal nursing device, signal generating device, A / D converting ADC device, high frequency control device, USB communication control monolithic computer and a set of power supply control and switch device. It is featured as only using power supply from USB bus to realize oscillascope function of detecting AC power signal, rectifying waveform, digital logic, serial data, etc.

Owner:ZHEJIANG DAHUA TECH CO LTD

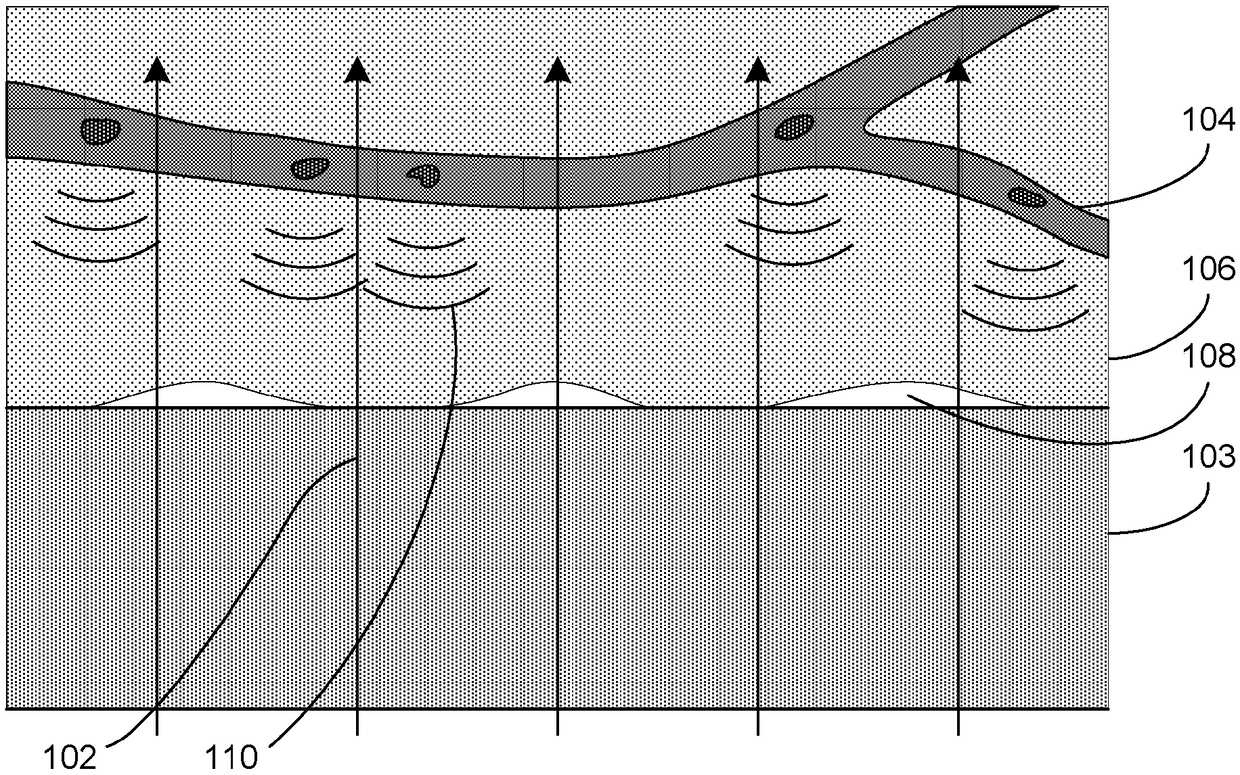

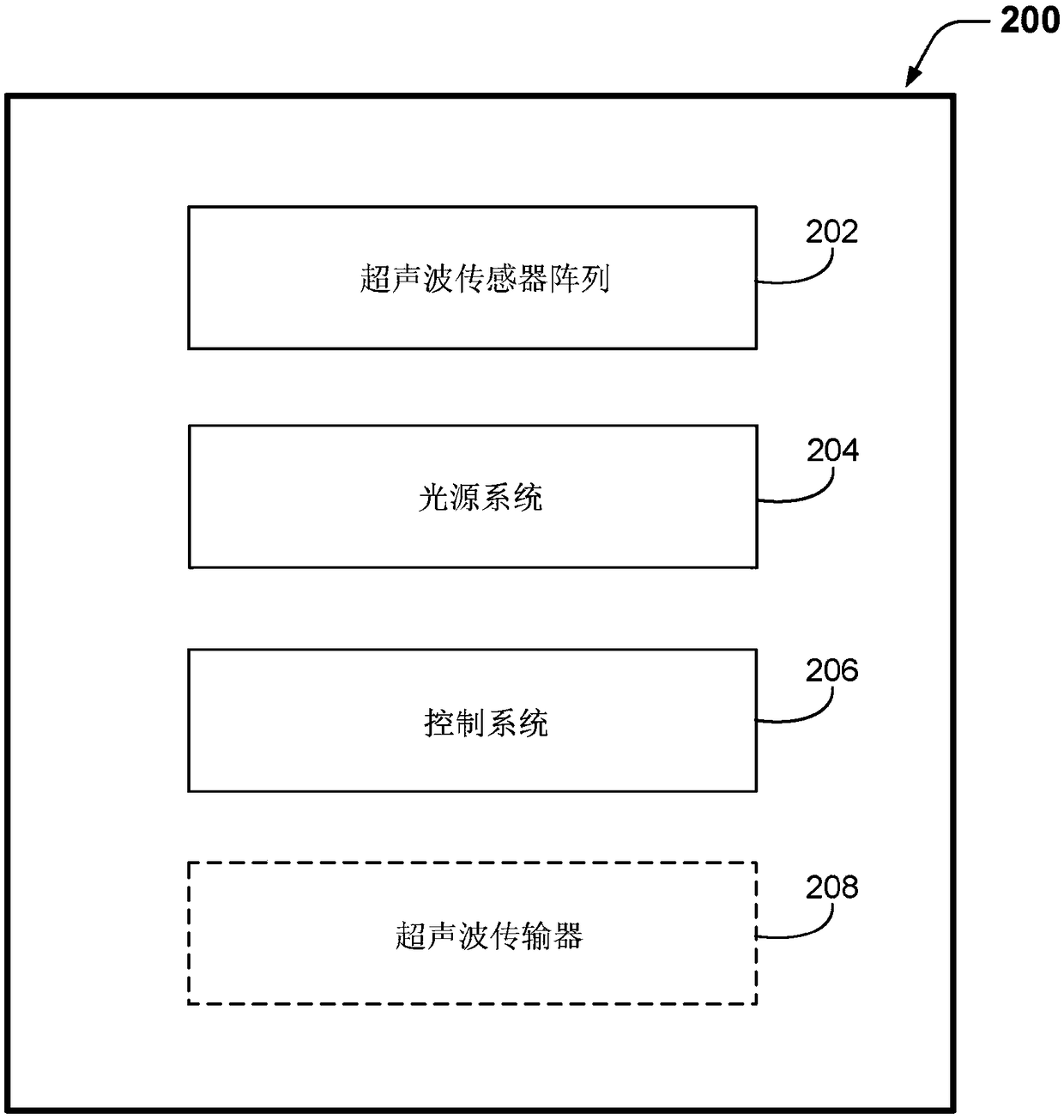

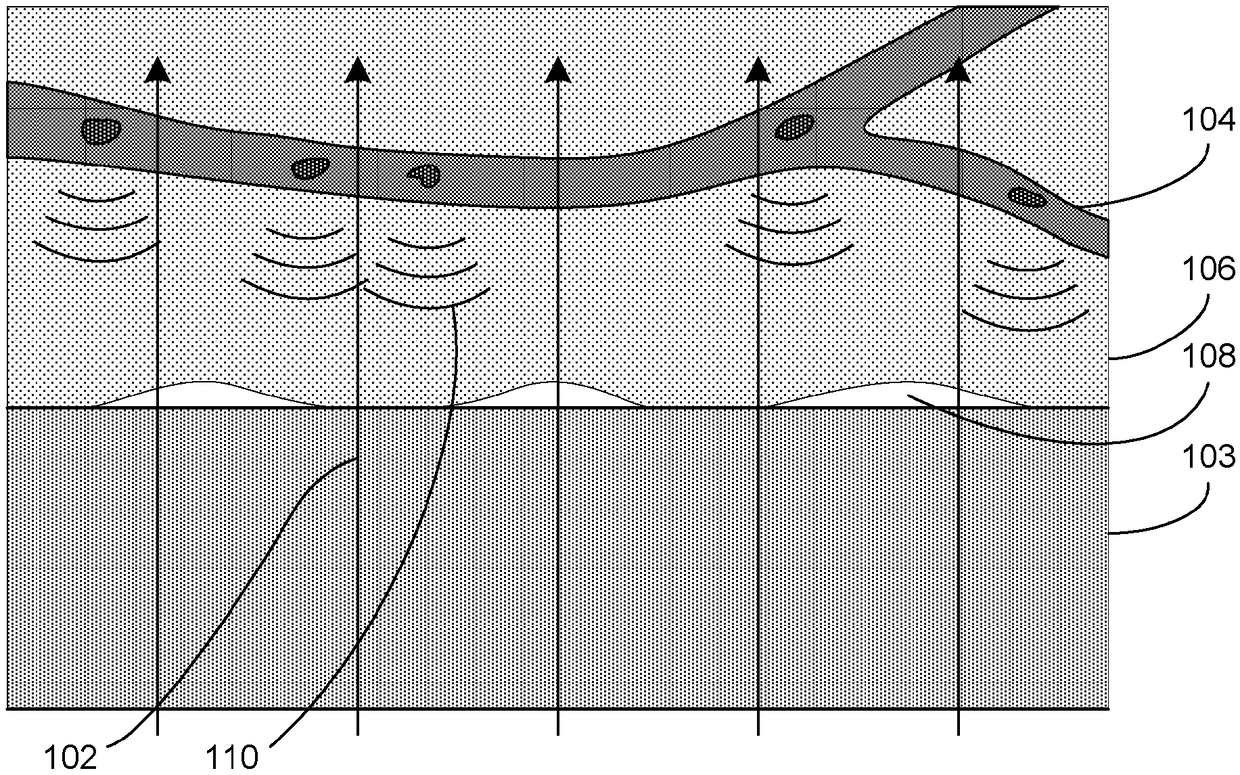

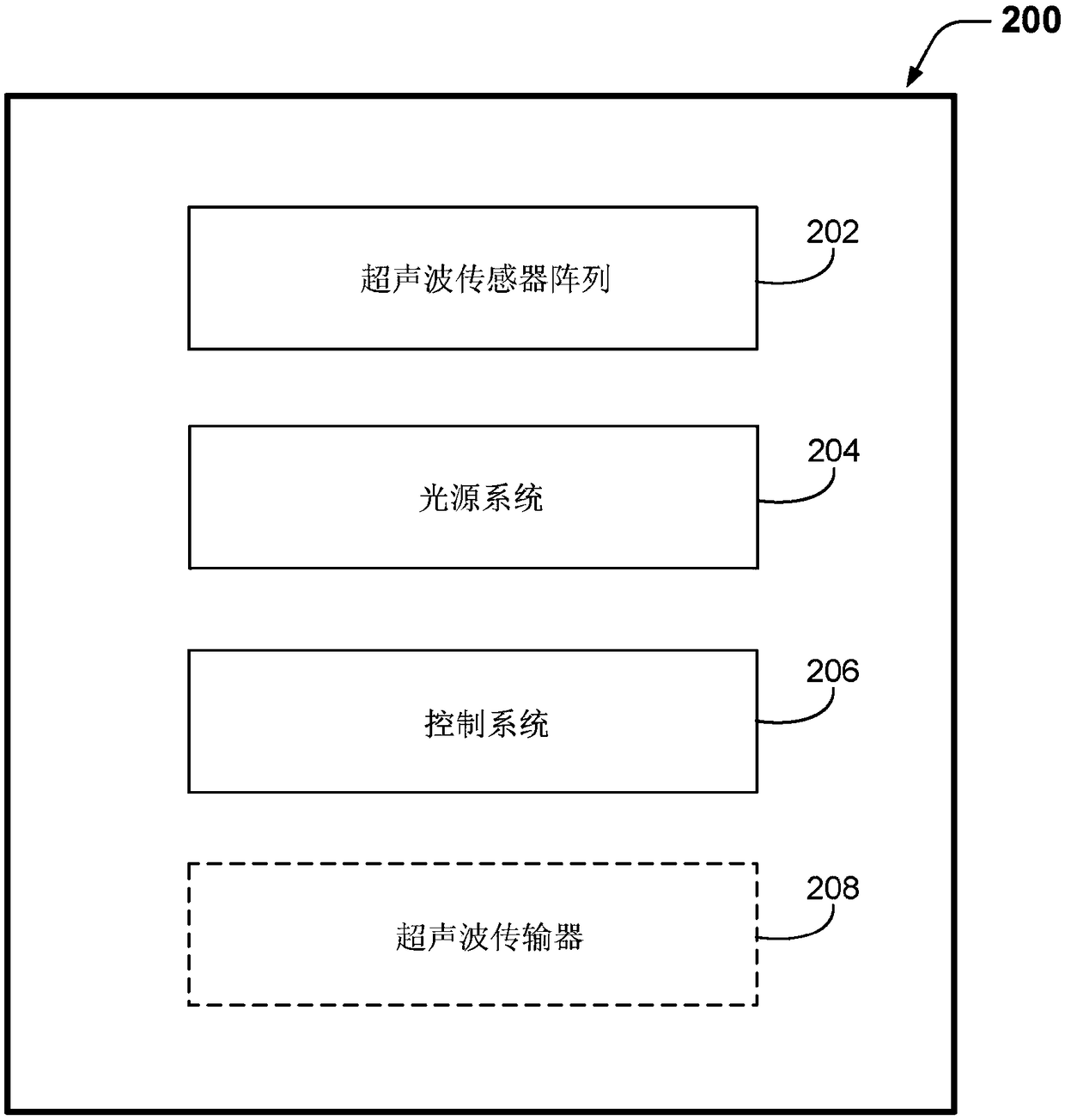

Biometric system with photoacoustic image processing

ActiveCN109069001AVerified and reliableAcoustic sensorsDiagnostic recording/measuringEngineeringUltrasonic transmission

Disclosed is an apparatus. The apparatus may include an ultrasonic sensor array, a light source system and a control system. Some implementations may include an ultrasonic transmitter. The control system may be operatively configured to control the light source system to emit light that induces acoustic wave emissions inside a target object. The control system may be operatively configured to select a first acquisition time delay for the reception of acoustic wave emissions primarily from a first depth inside the target object. The control system may be operatively configured to acquire firstultrasonic image data from the acoustic wave emissions received by the ultrasonic sensor array during a first acquisition time window. The first acquisition time window may be initiated at an end timeof the first acquisition time delay.

Owner:QUALCOMM INC

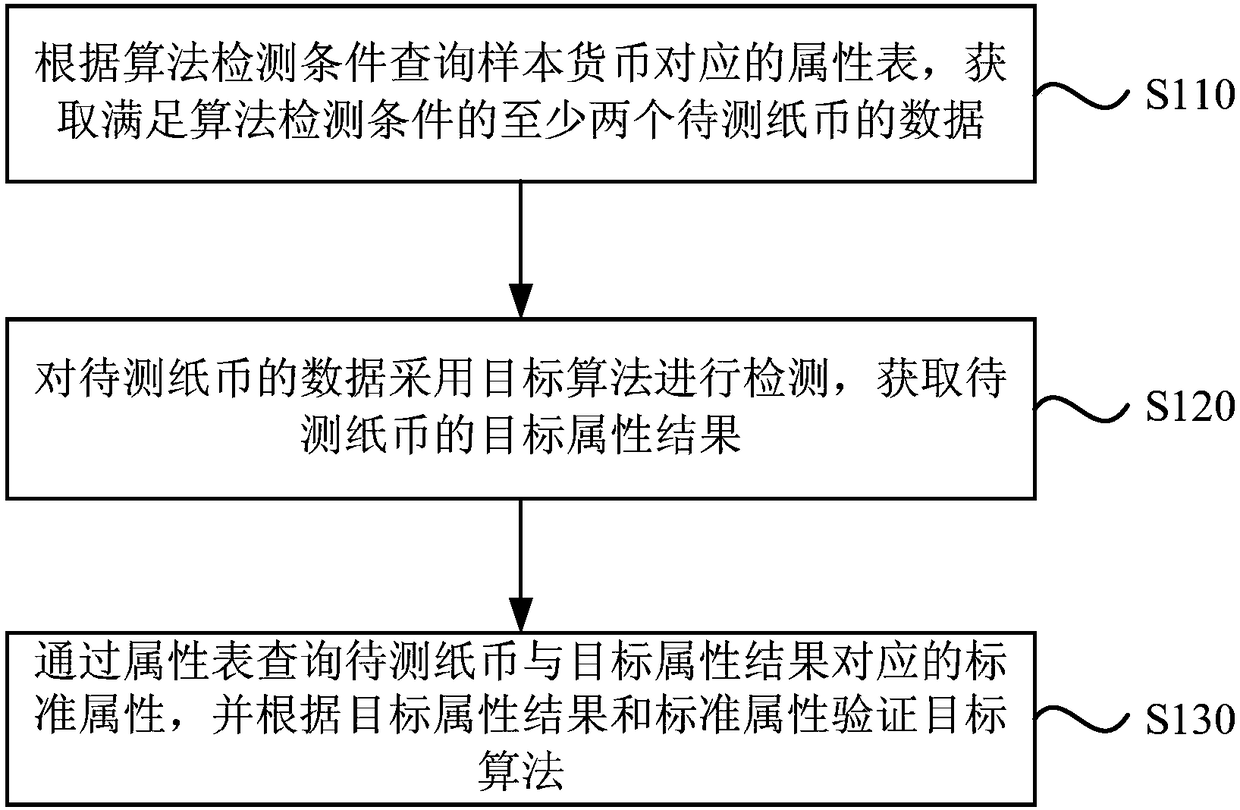

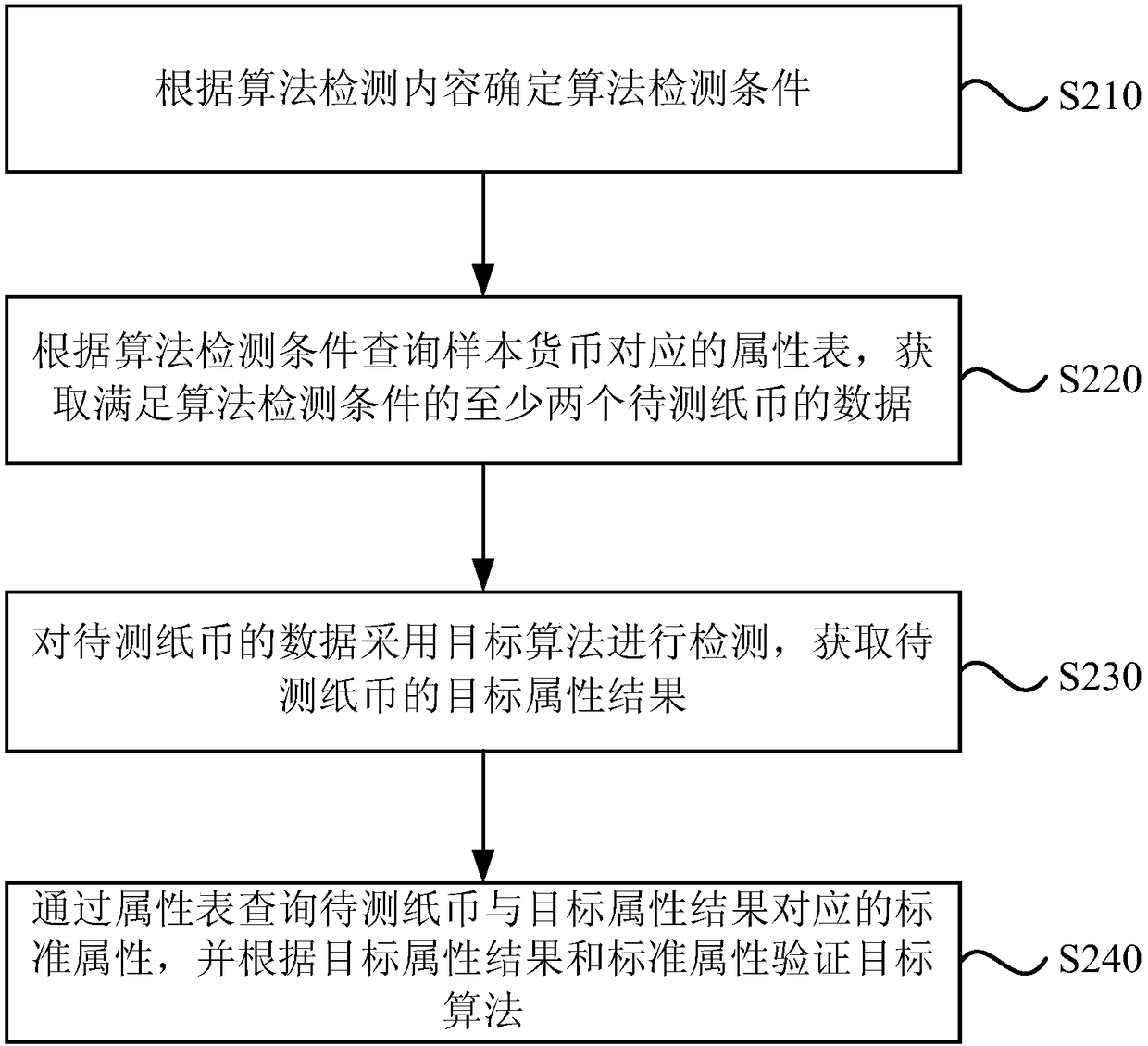

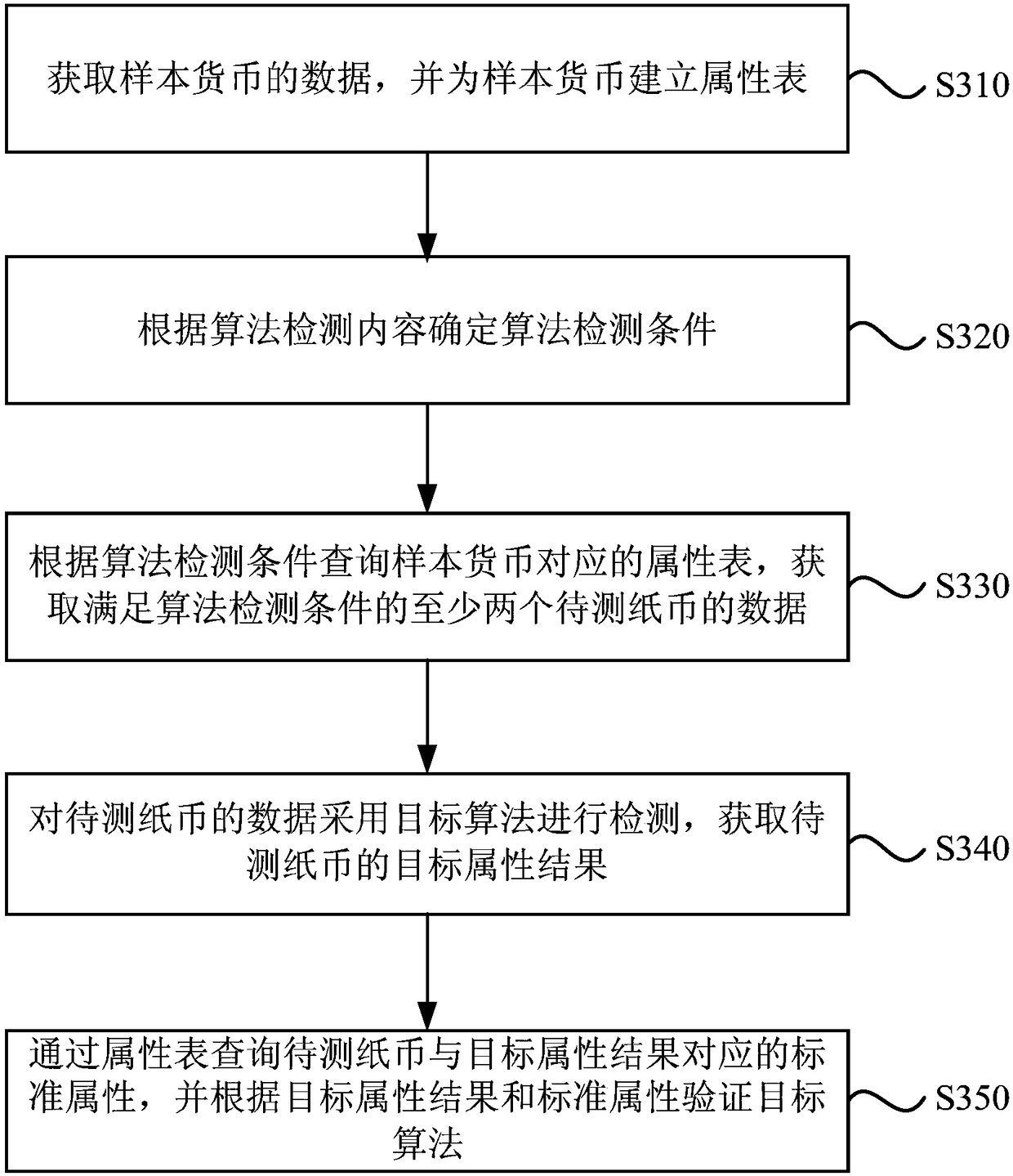

Paper currency data-based algorithm verification method and device

InactiveCN108415915AEasy to manageVerify stablePaper-money testing devicesSpecial data processing applicationsData miningMagnetism

Embodiments of the invention disclose a paper currency data-based algorithm verification method and device. The method comprises the following steps of: detecting an attribute table corresponding to asample currency according to an algorithm detection condition, and obtaining data of at least two to-be-tested paper currencies satisfying the algorithm detection condition, wherein the data comprises an image, an area thickness and / or magnetism; detecting the data of the to-be-tested paper currencies by adoption of a target algorithm, and obtaining target attribute results of the to-be-tested paper currencies; and querying standard attributes, corresponding to the target attribute results, of the to-be-tested paper currencies through the attribute table, and verifying the target algorithm according to the target attribute results and the standard attributes. Through the method and device, algorithm verification can be carried out rapidly, conveniently, stably and reliably.

Owner:SHENZHEN YIHUA COMP +2

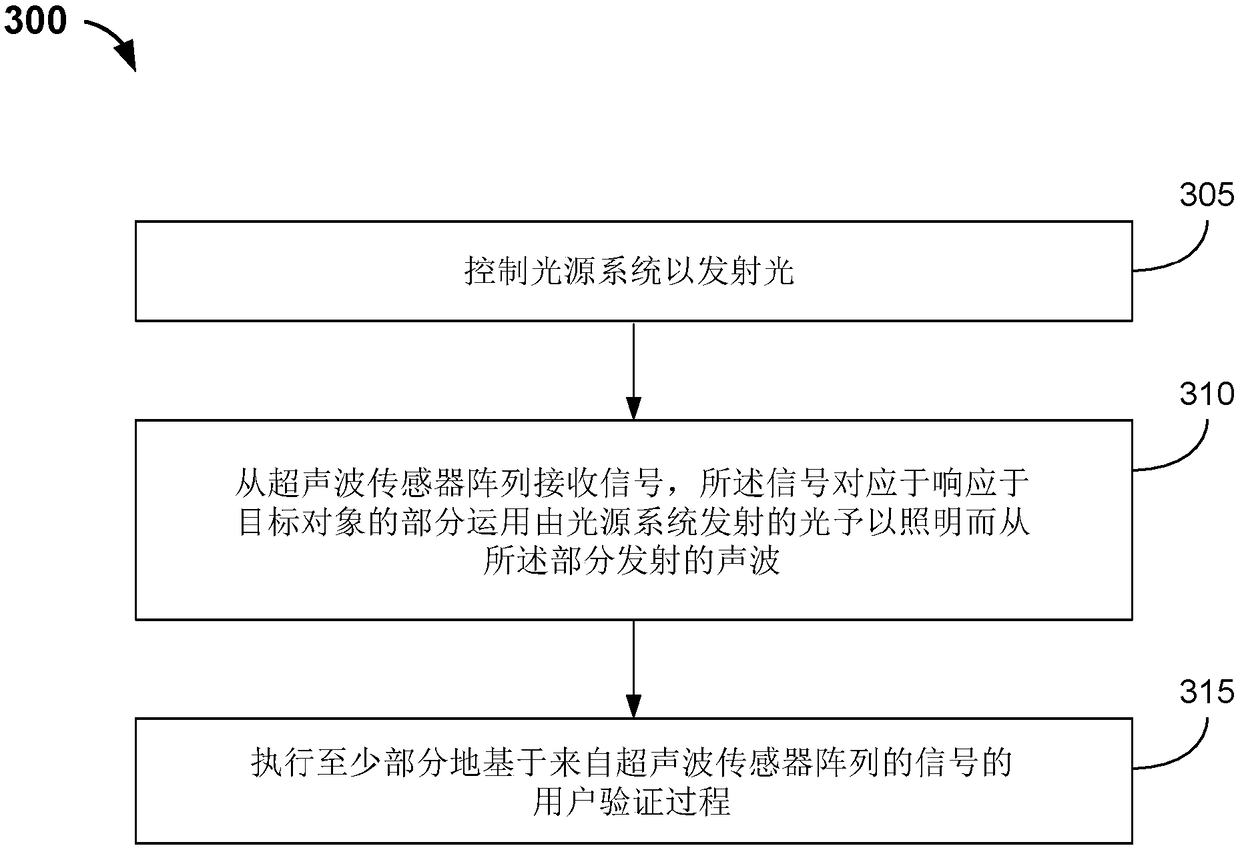

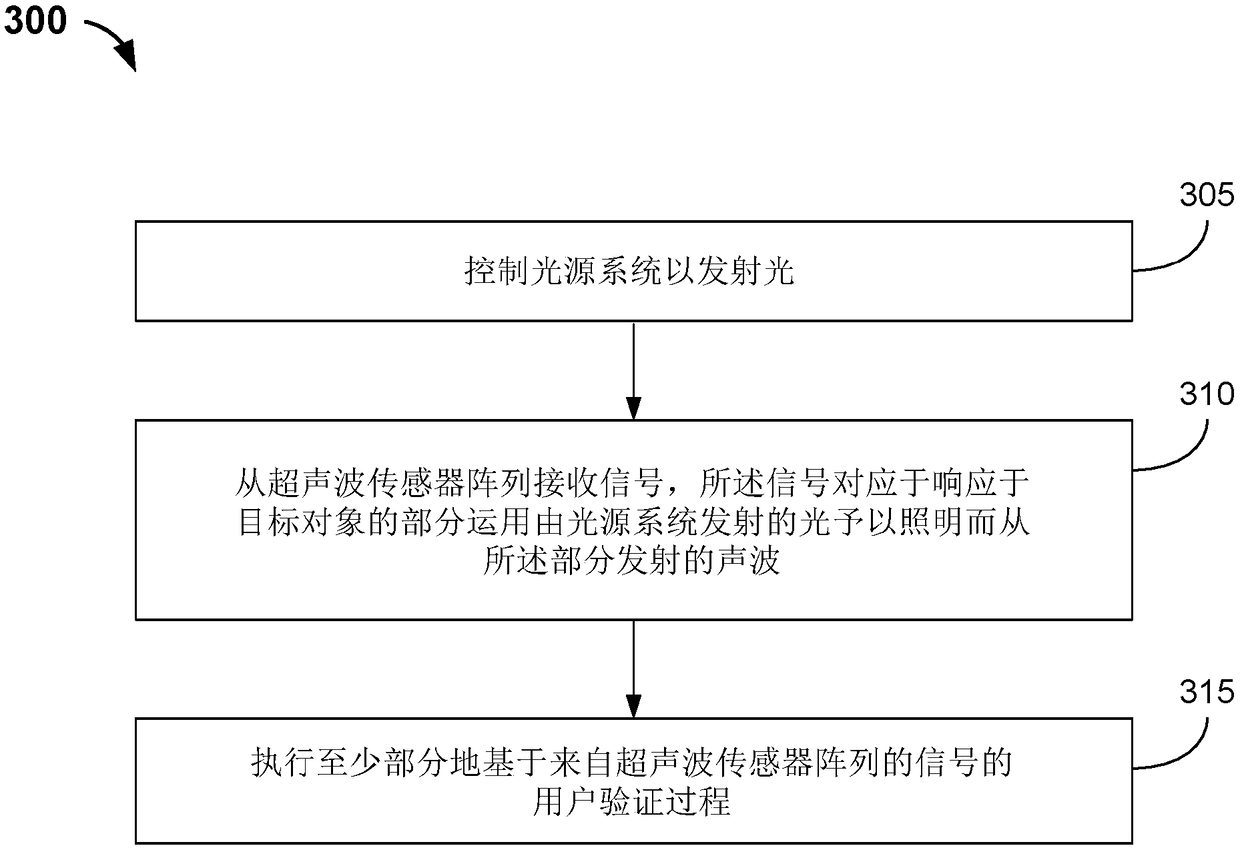

Biometric system with photoacoustic imaging

ActiveCN109328354AVerified and reliableMaterial analysis using acoustic emission techniquesDigital data authenticationUser verificationUser authentication

The invention discloses a biometric system which may include an ultrasonic sensor array, a light source system and a control system. Some implementations may include an ultrasonic transmitter. The control system may be capable of controlling the light source system to emit light and of receiving signals from the ultrasonic sensor array corresponding to acoustic waves emitted from portions of a target object in response to being illuminated with the light emitted by the light source system. The control system may be capable of performing a user authentication process that is based, at least inpart, on the signals from the ultrasonic sensor array.

Owner:QUALCOMM INC

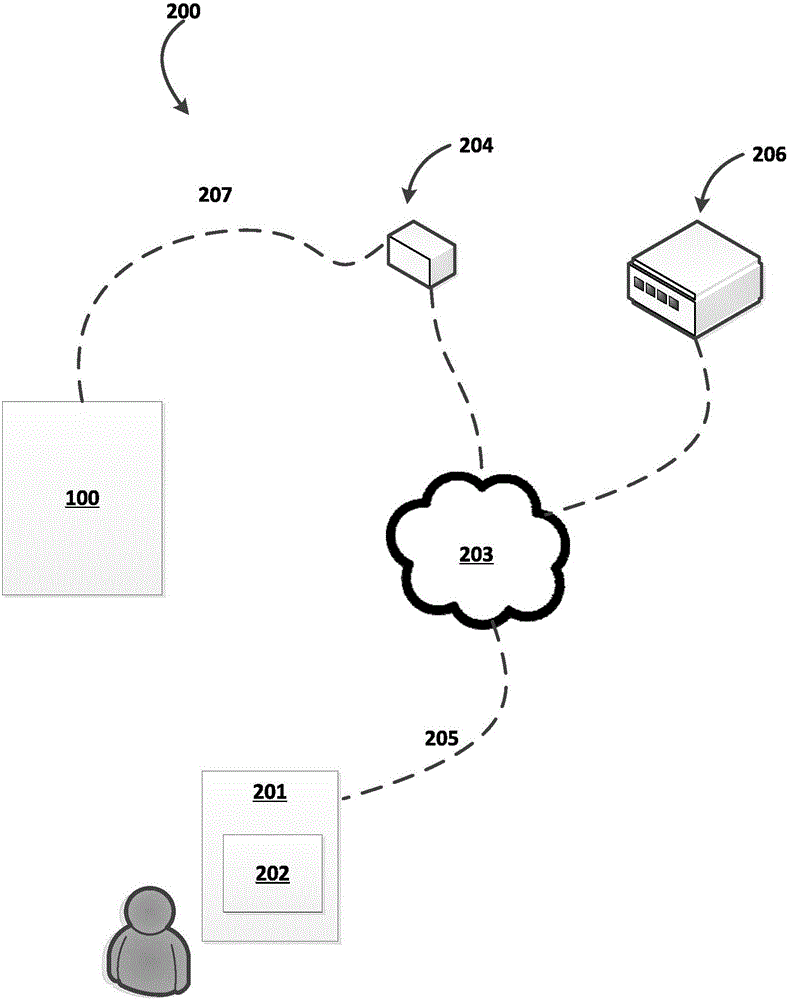

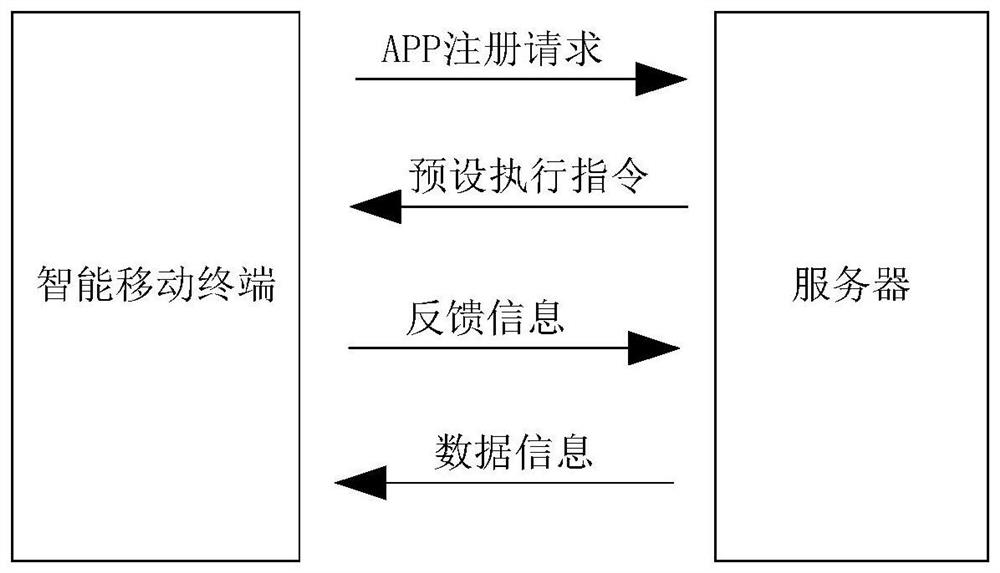

Data acquisition system based on cloud computing

InactiveCN111953688AReduce workloadReduce the possibility of illegal acquisitionSubstation equipmentTransmissionData acquisitionDatabase

The invention relates to a data acquisition system based on cloud computing. The system comprises an intelligent mobile terminal and a server. The intelligent mobile terminal outputs an APP registration request to the server, the server acquires historical registration times of registering other related APPs in a preset time period, and if the historical registration times are greater than or equal to a preset registration time threshold, a first abnormal score is obtained; and the server sends a preset execution instruction to the intelligent mobile terminal, if the intelligent mobile terminal executes the preset execution instruction, a second exception score is obtained, an exception judgment value is obtained according to the two exception scores and the corresponding weights, and if the exception judgment value is smaller than a preset exception threshold value, the server outputs the corresponding data information to the intelligent mobile terminal. According to the data acquisition system, the possibility of illegal registration and illegal data acquisition can be reduced, the occupation amount and the workload of operation resources of the server are reduced, the influenceon the use of other normal members is avoided, and the interest loss degree of an APP operator is reduced.

Owner:西安博康硕达网络科技有限公司

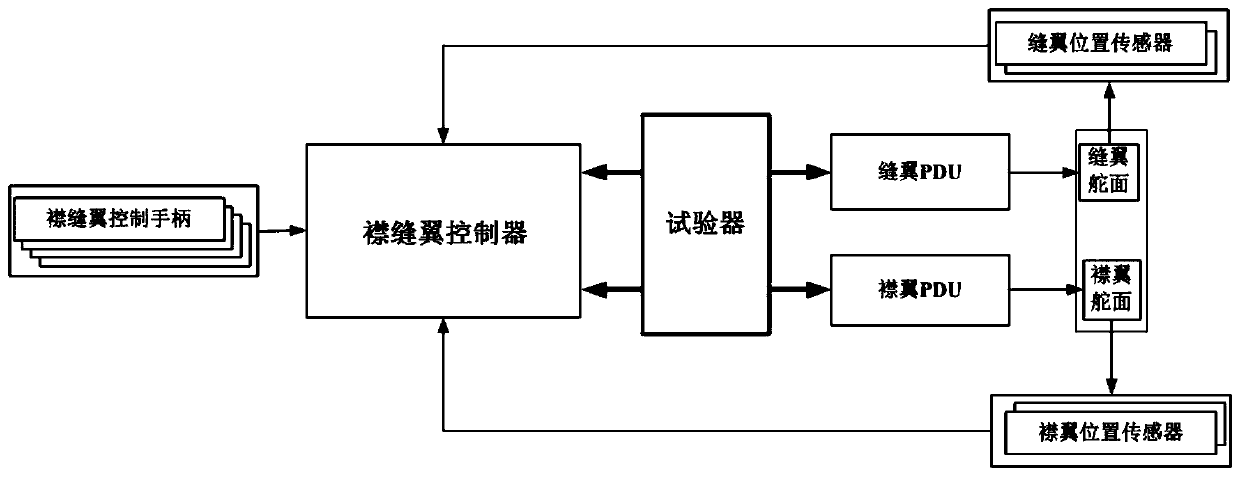

Flap and slat non-instruction motion protection verification system and verification method

ActiveCN111017195AComprehensive and reliable functional performanceVerified and reliableAircraft health monitoring devicesAircraft controlVerification systemPosition sensor

The invention discloses a flap and slat non-instruction motion protection verification system and verification method. The device comprises a flap and slat control handle, a flap and slat controller,a tester, a slat power driving device, a flap power driving device, a slat control surface, a flap control surface, a slat position sensor and a flap position sensor, wherein an instruction output bythe flap and slat controller is adjusted through the tester; and the flap and slat driving device drives the control surface to perform non-instruction motion after receiving the adjusted instruction.The test problem of the flap and slat non-instruction motion protection function of the flap and slat controller is solved, the comprehensive and reliable verification of the functional performance of the flap and slat controller is realized, and the reference of a non-instruction motion detection method is provided for other similar products.

Owner:XIAN AIRCRAFT DESIGN INST OF AVIATION IND OF CHINA

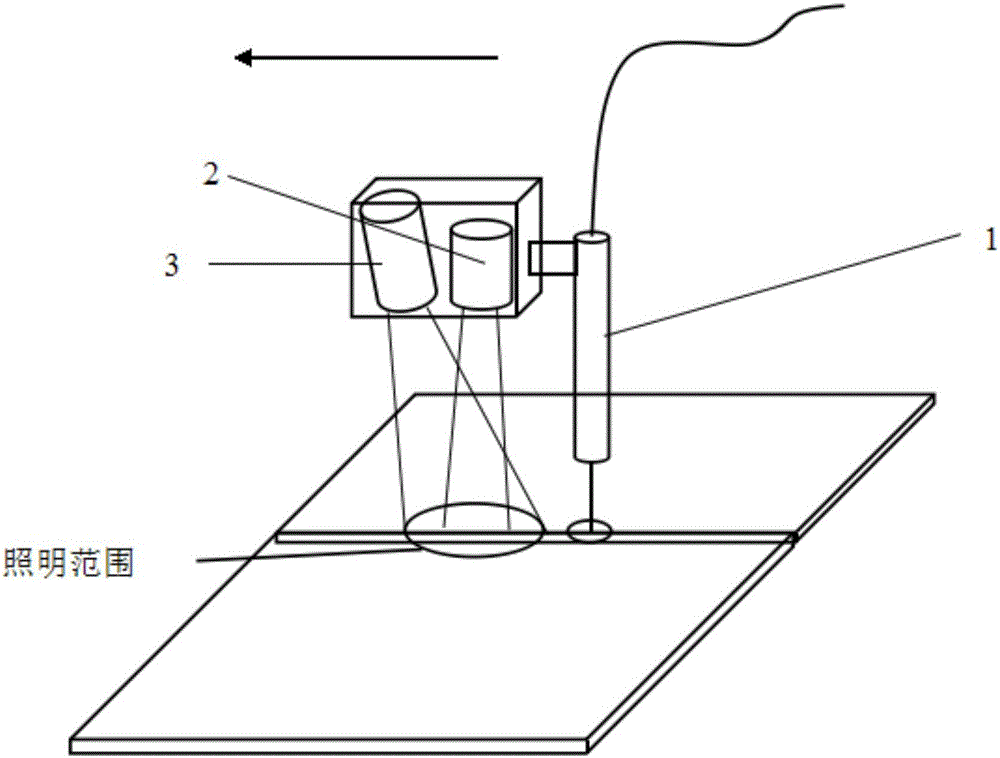

Weld verification method

InactiveCN106514064AVerified and reliableNo authentication failures will occurImage analysisWelding/cutting auxillary devicesArray data structureValidation methods

The invention relates to a verification method for butt weld detection results. The verification method includes the following steps that a weld image and a weld straight line to be verified in the weld image are acquired; q pixel points are selected at the two sides of each row of intersection points with the weld straight line to be verified to form an image subset, the direction of an original image row is generally perpendicular to the weld straight line to be verified, and q is a positive integer which is larger than or equal to 1; all the rows of the image subset are added to obtain an array, the array is subjected to first-order difference, and the positions of the maximum value and the minimum value are found out; and if the maximum value and the minimum value are located at the two sides of the weld straight line to be verified, it is judged that the weld position to be verified is reliable. By the adoption of the method, butt welds (including the welds without gaps and with certain gaps) of sheets under various conditions can be reliably verified, and the phenomenon of recognition failure can be avoided.

Owner:SUZHOU VR ROBOT TECH CO LTD