Two-dimensional layered material-based avalanche field-effect transistor and measurement device

A field-effect transistor, two-dimensional layered technology, applied in the direction of single semiconductor device testing, semiconductor devices, electrical components, etc., can solve the problems of gate voltage losing control of the transistor, unable to completely turn off the transistor, and transistor voltage drop, etc., to achieve small Reset feature, good stability and low energy consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

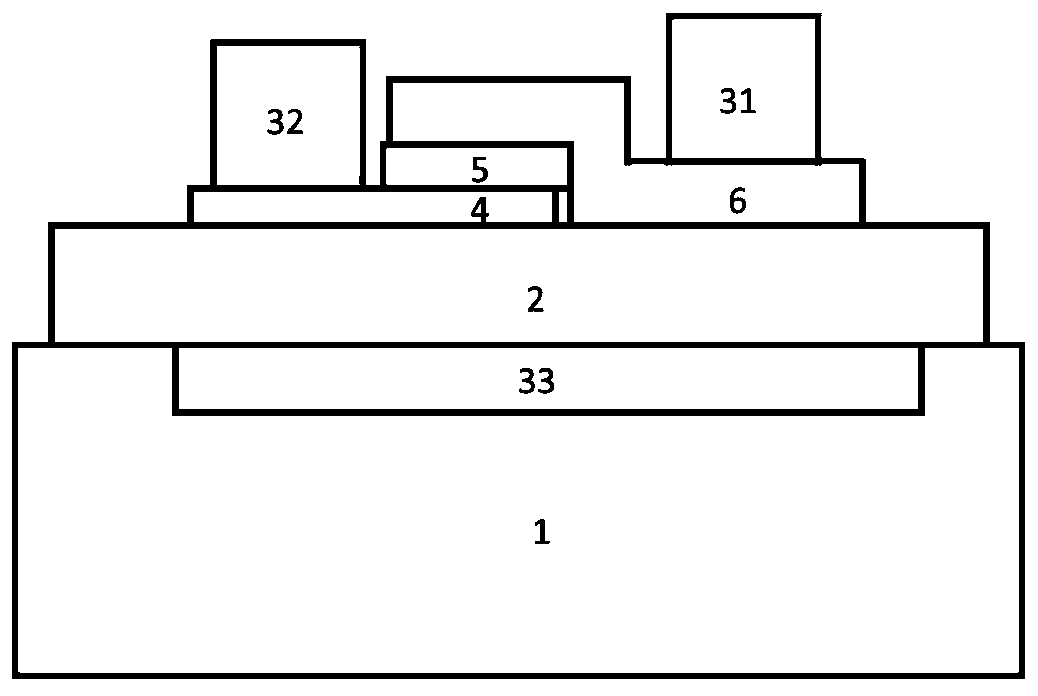

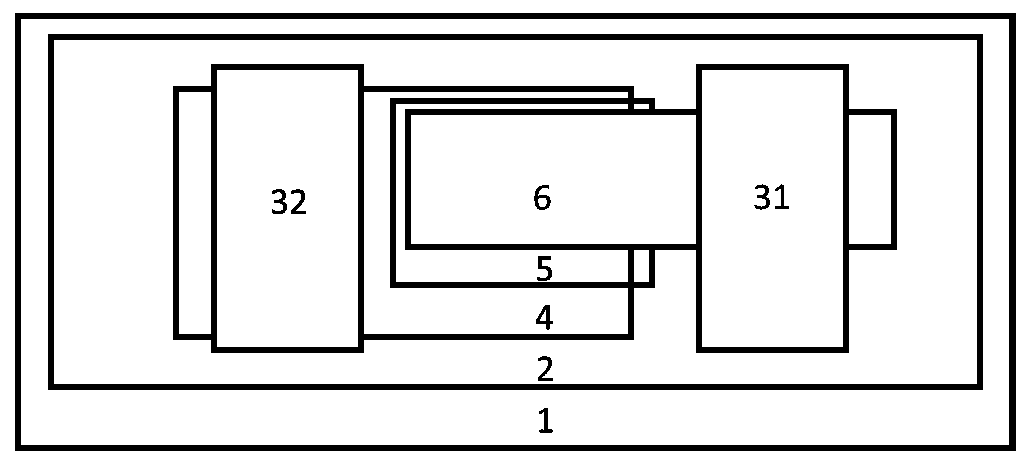

[0025] Such as figure 1 , figure 2 and image 3 As shown, the present embodiment is based on the avalanche field effect transistor of two-dimensional layered materials, including an insulating layer 2, a metal electrode layer, a first two-dimensional material film layer 4, a second two-dimensional material film layer 5 and a third two-dimensional material film layer The thin film layer 6; the metal electrode layer includes a drain electrode layer 31, a source electrode layer 32 and a gate electrode layer 33; the first two-dimensional material thin film layer 4 and the third two-dimensional material thin film layer 6 are laid on the insulating layer 2, the second two The two-dimensional material thin film layer 5 is located between the two stacked parts, the source electrode layer 32 covers the non-stacked part of the first two-dimensional material thin film layer 4, and the drain electrode layer 31 covers the top of the stacked part or the third two-dimensional material thin...

Embodiment 2

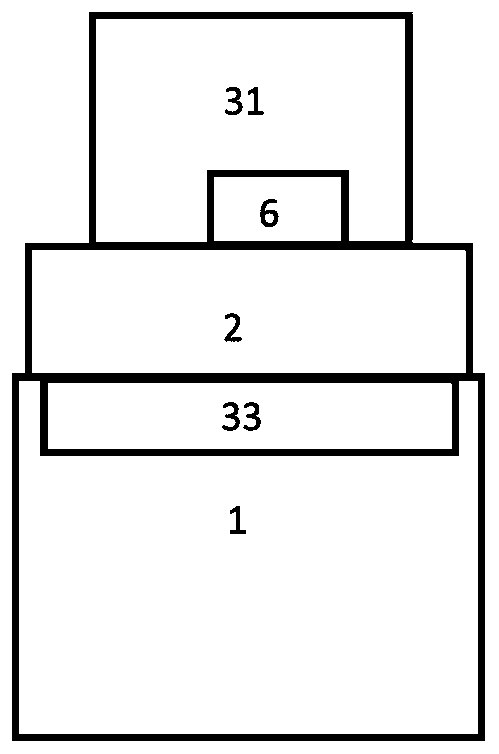

[0049] Such as Figure 6 As shown, the difference between this embodiment and Embodiment 1 is that the gate electrode layer 33 is located above the insulating layer 2, and is connected to the drain electrode layer 31, the source electrode layer 32 and the third two-dimensional material film through another insulating layer 2. Layer 6 connections. The third two-dimensional material thin film layer 5 is an n-type two-dimensional single crystal material, and the second two-dimensional material thin film layer 6 is a p-type two-dimensional single crystal material.

Embodiment 3

[0051] Such as Figure 7 As shown, the difference between this embodiment and Embodiment 1 is that there are two gate electrode layers 33, one is located below the insulating layer 2, and the other is located above the insulating layer 2, and is connected to the drain electrode layer through another insulating layer 2. 31. The source electrode layer 32 is connected to the third two-dimensional material thin film layer 6 .

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More