configurable parallel BCH error correction coding method

An error correction coding and coding technology, applied in the field of data error correction, can solve problems such as low computing efficiency and inability to meet high-speed data processing

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

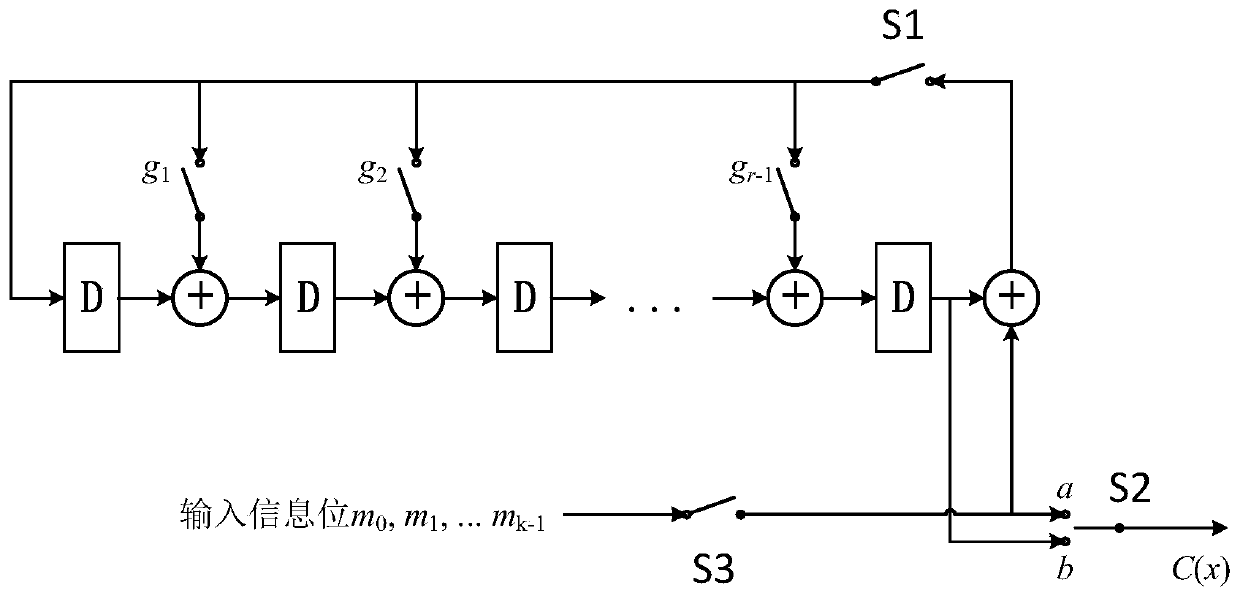

Method used

Image

Examples

Embodiment Construction

[0031] In order to make the purpose, content, and advantages of the present invention clearer, the specific implementation manners of the present invention will be described in further detail below in conjunction with the accompanying drawings and examples.

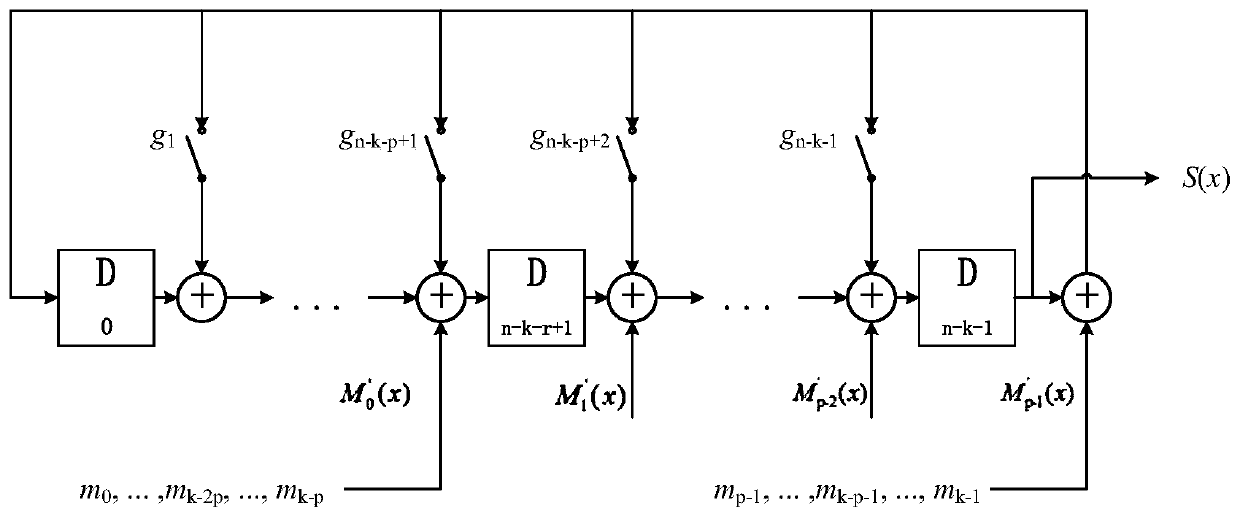

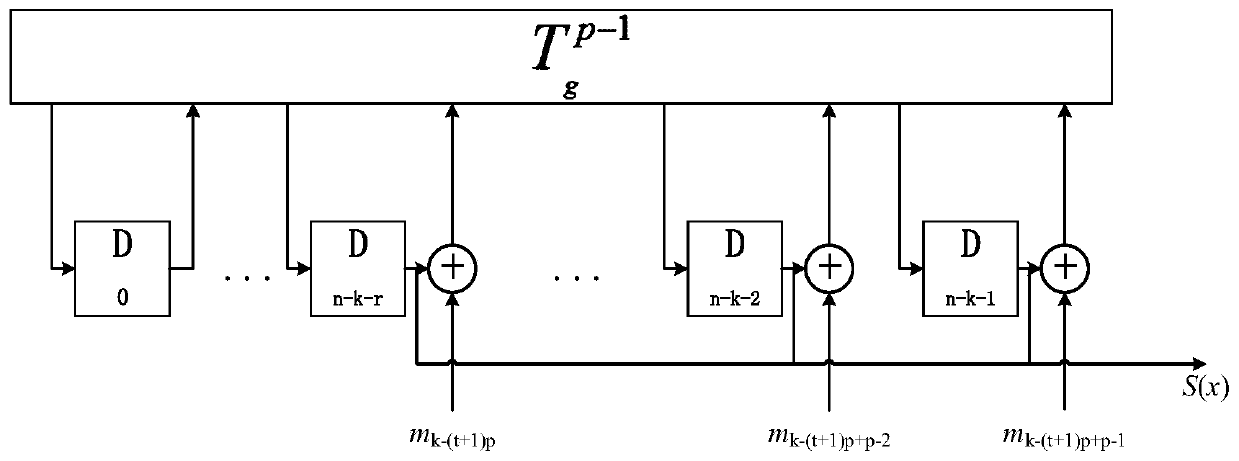

[0032] A configurable parallel BCH error correction coding method of the present invention includes: in order to improve computing efficiency and realize parallel computing, the following algorithm uses p as the data bit width for parallel computing. First, two settings are given: one is that the information bit k can be divisible by p, that is, kmodp=0; the other is that p is smaller than the check bit length r.

[0033] Firstly, the original information polynomial M(x) is divided into p groups in the following way to obtain:

[0034] M(x)=M 0 (x)+M 1 (x)+...+M p-1 (x),

[0035] in

[0036] Further calculations:

[0037]

[0038] in

[0039] Then, the encoding check digit S(x) can be expressed as:

[0040]...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More