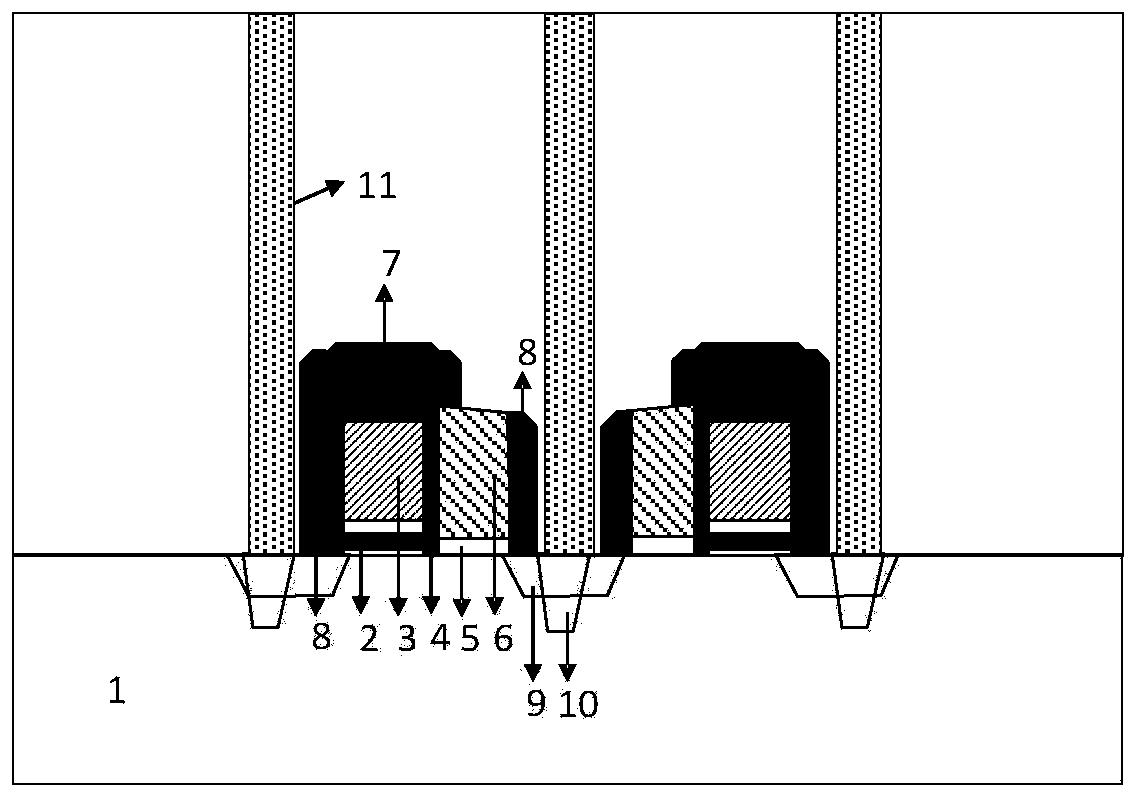

Split-gate SONOS (Semiconductor Oxide Nitride Oxide Semiconductor) memory device

A storage device and split-gate technology, which is applied in the direction of electric solid-state devices, semiconductor devices, electrical components, etc., can solve problems such as affecting, degrading device performance, reducing device channel mobility, etc., to reduce manufacturing costs and improve device performance. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

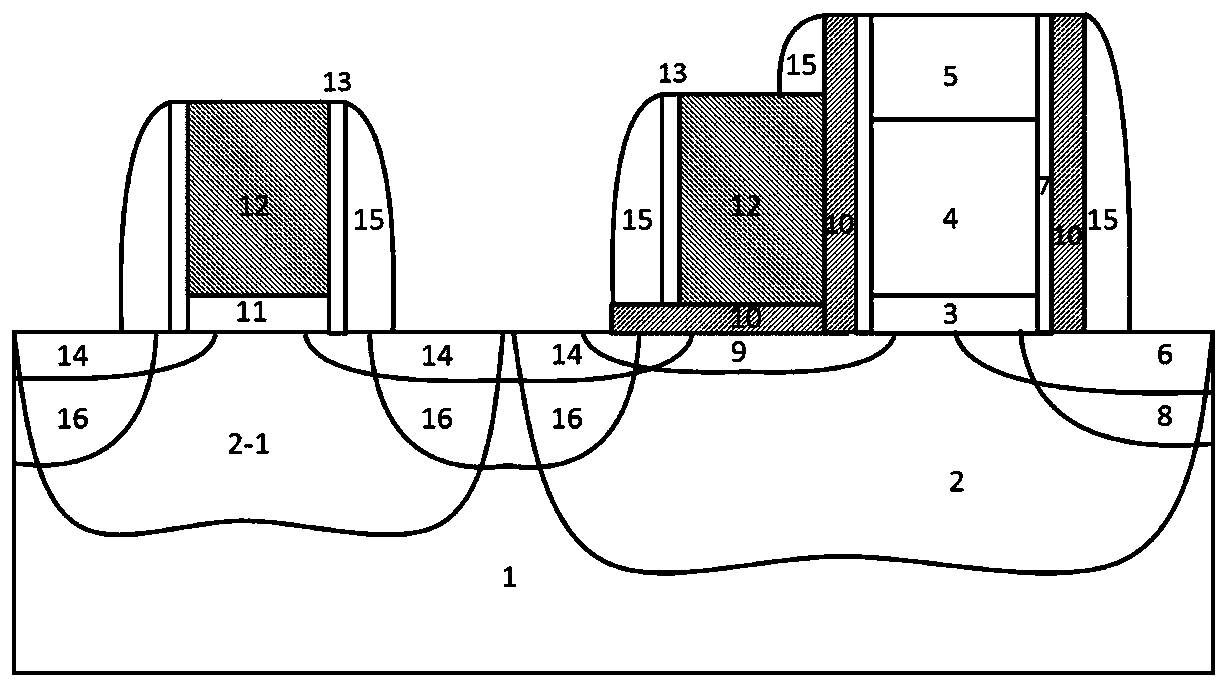

Embodiment 1

[0023] like figure 2 as shown, figure 2 It is a schematic structural diagram of a split-gate SONOS memory device according to the present invention. In this embodiment, the device structure includes: a P-type substrate 1 and a gate oxide layer 3 and an ONO oxynitride layer 10 formed on the P-type substrate 1; the gate oxide layer 3 is used to form the selection The gate oxide layer of the tube; the oxynitride layer 10 is a multi-layer structure of oxide layer-nitride layer-oxide layer, which is used as the ONO layer of the storage tube; the gate oxide layer 3 is sequentially provided with a polysilicon gate 4 and a selection transistor polysilicon gate The top oxide layer 5 on the polysilicon gate 4 of the selection transistor forms a stacked structure; that is, the three-layer structure located on the upper surface of the substrate from bottom to top is: the gate oxide layer 3, the selection transistor Polysilicon gate 4, top oxide layer 5.

[0024] The split-gate SONOS ...

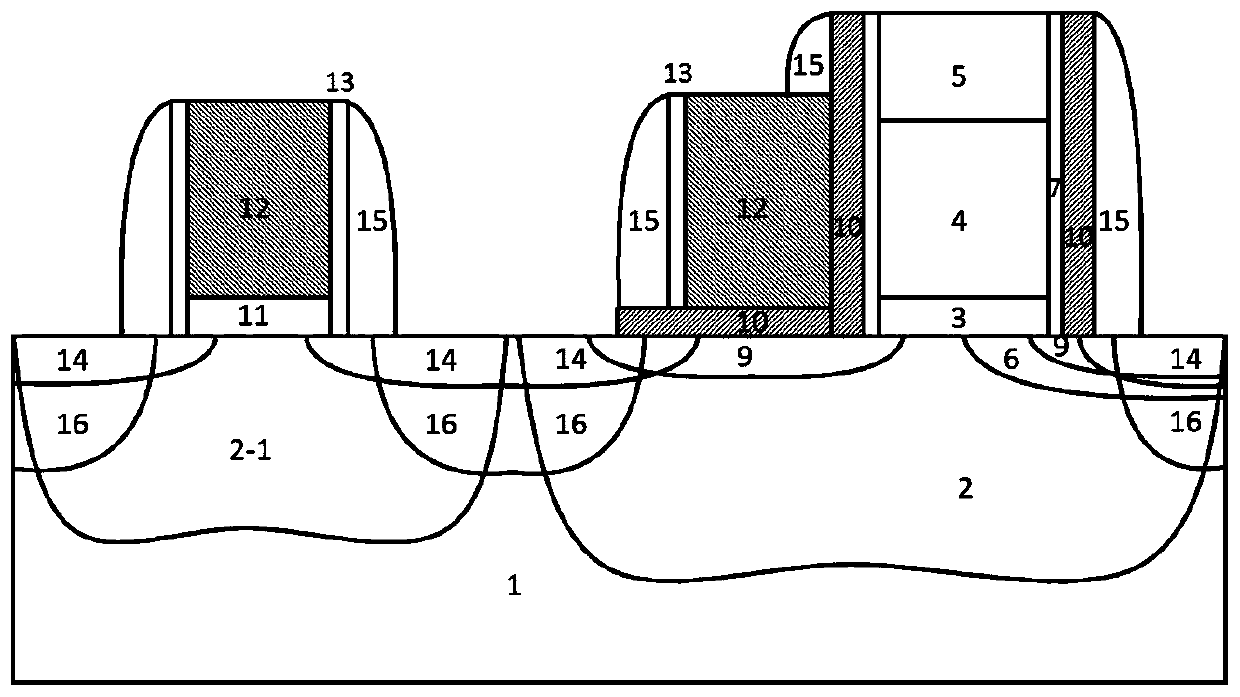

Embodiment 2

[0034] like image 3 as shown, image 3 It is a schematic structural diagram of another split-gate SONOS storage device of the present invention. In this embodiment, the device structure includes: a P-type substrate 1 and a gate oxide layer 3 and an ONO oxynitride layer 10 formed on the P-type substrate 1; the gate oxide layer 3 is used to form the selection The gate oxide layer of the tube; the oxynitride layer 10 is a multi-layer structure of oxide layer-nitride layer-oxide layer, which is used as the ONO layer of the storage tube; the gate oxide layer 3 is sequentially provided with a polysilicon gate 4 and a selection transistor polysilicon gate The top oxide layer 5 on the polysilicon gate 4 of the selection transistor forms a stacked structure; that is, the three-layer structure located on the upper surface of the substrate from bottom to top is: the gate oxide layer 3, the selection transistor Polysilicon gate 4, top oxide layer 5.

[0035] The split-gate SONOS stora...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More