Thin film transistor device manufacturing method

A device manufacturing method and thin-film transistor technology, applied in semiconductor/solid-state device manufacturing, transistors, electrical components, etc., can solve problems such as channel width limitation and critical dimension loss

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

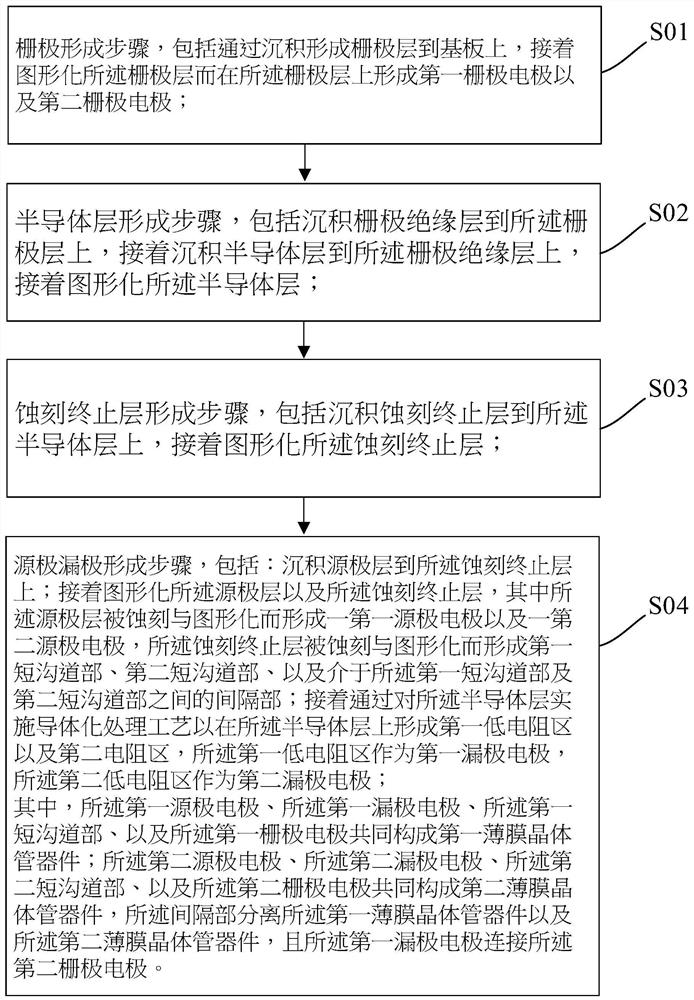

[0030] Please refer to figure 1 , The method for manufacturing a thin film transistor (Thin Film Transistor, TFT) device of the present invention includes: a gate forming step S01, a semiconductor layer forming step S02, an etching stop layer forming step S03, and a source and drain forming step S04.

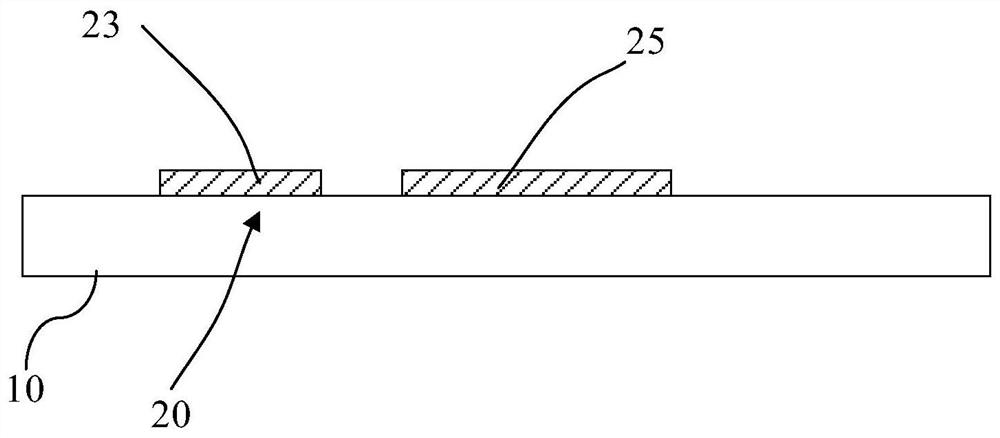

[0031] Please refer to figure 2 , the gate forming step S01 includes depositing and forming a gate (Gate Electrode, GE) layer on the substrate 10 by a physical vapor deposition (Physical Vapor Deposition, PVD) process, and then sequentially applying yellow light to the gate layer 20 process and etching process to pattern the gate layer 20 to form a first gate electrode 23 and a second gate electrode 25 on the gate layer 20 . In a preferred embodiment of the present invention, the gate layer 20 is made of molybdenum (Mo) and / or aluminum (Al). In a preferred embodiment of the present invention, the thickness of the gate layer 20 is 2000-5500 angstroms.

[0032] Please refer to...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More