MOS transistor and method of manufacturing the same

a technology of transistors and transistors, applied in the direction of transistors, semiconductor devices, electrical equipment, etc., can solve the problems of generating floating body effects, affecting the operation so as to improve the operating speed of the device, short channel effect, and reduce the capacitance of the source/drain junction

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] Hereinafter, the preferred embodiments of the invention will be described in detail with reference to the accompanying drawings, where like reference numerals indicate like elements throughout.

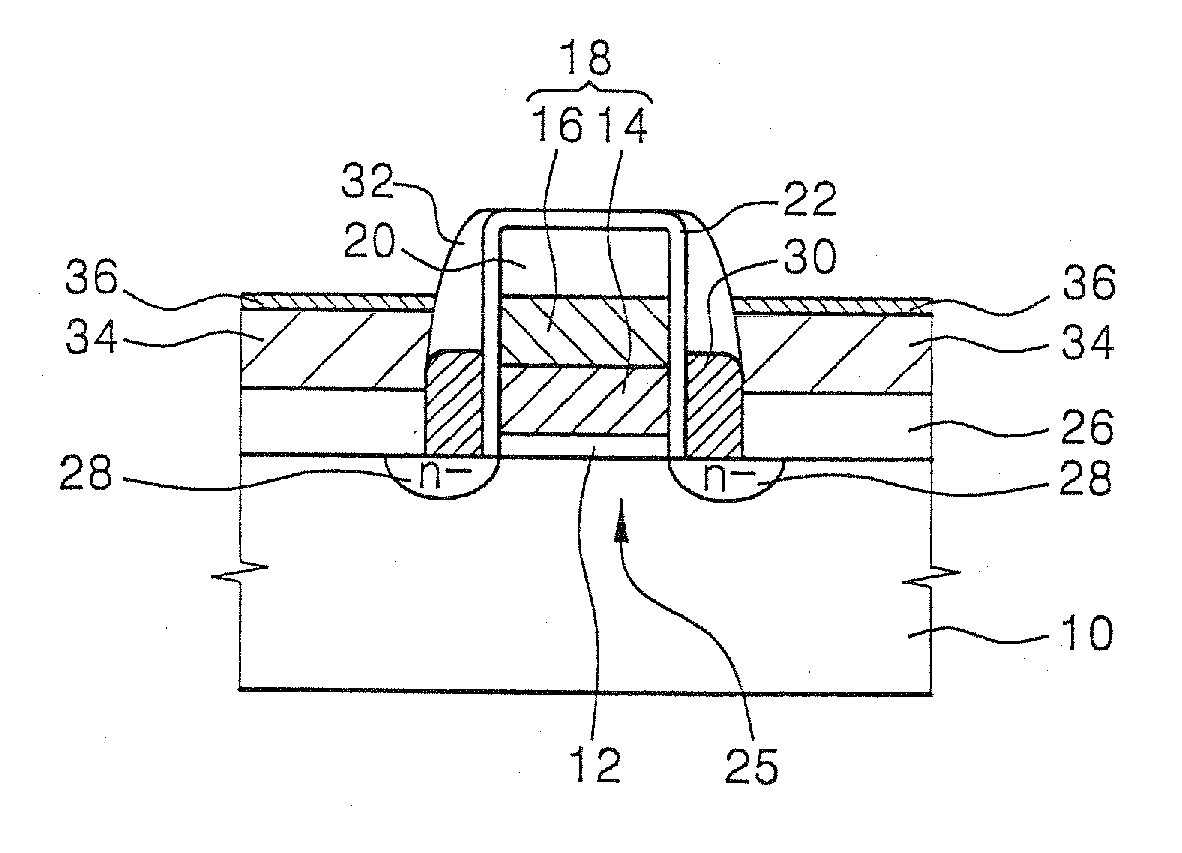

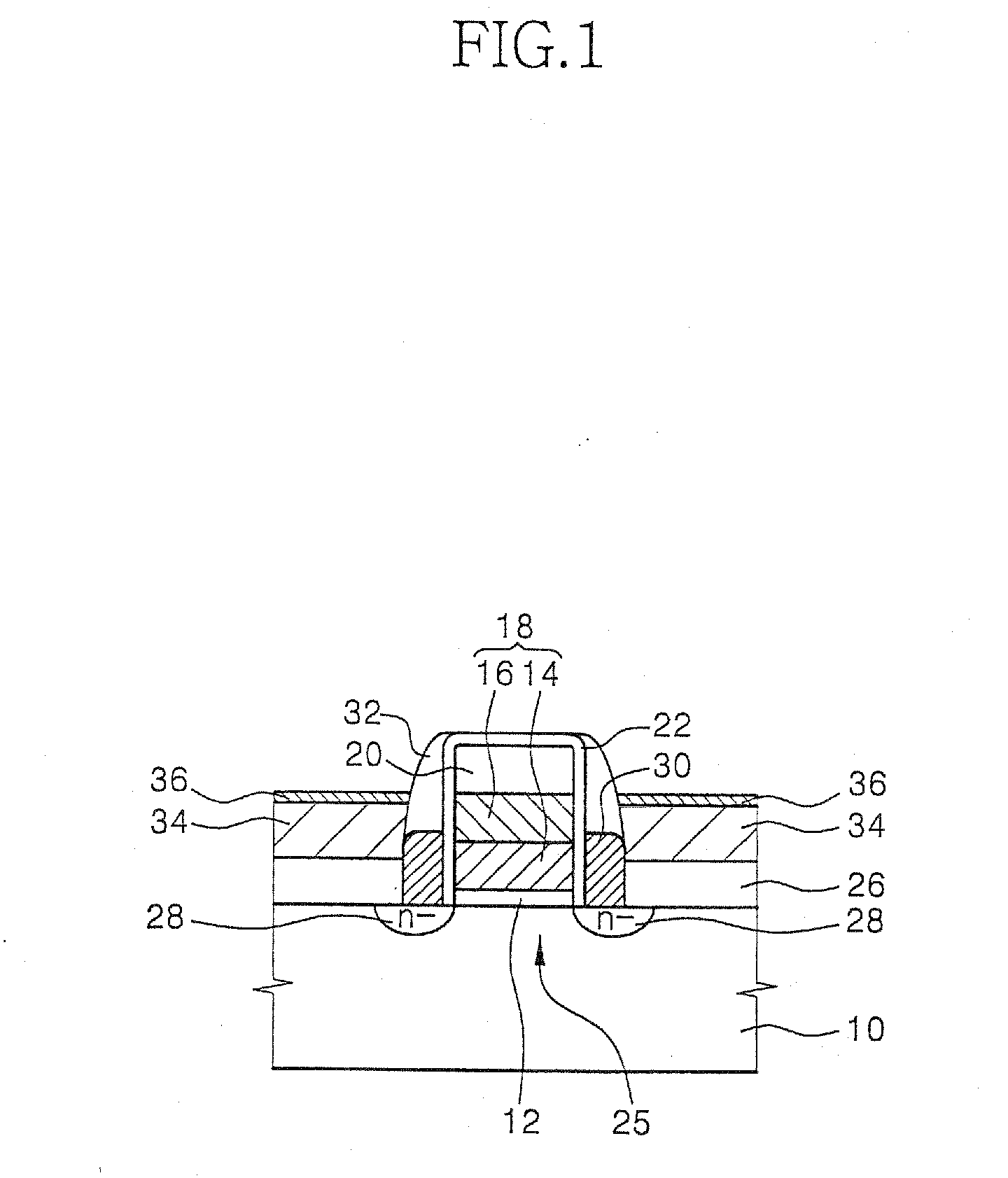

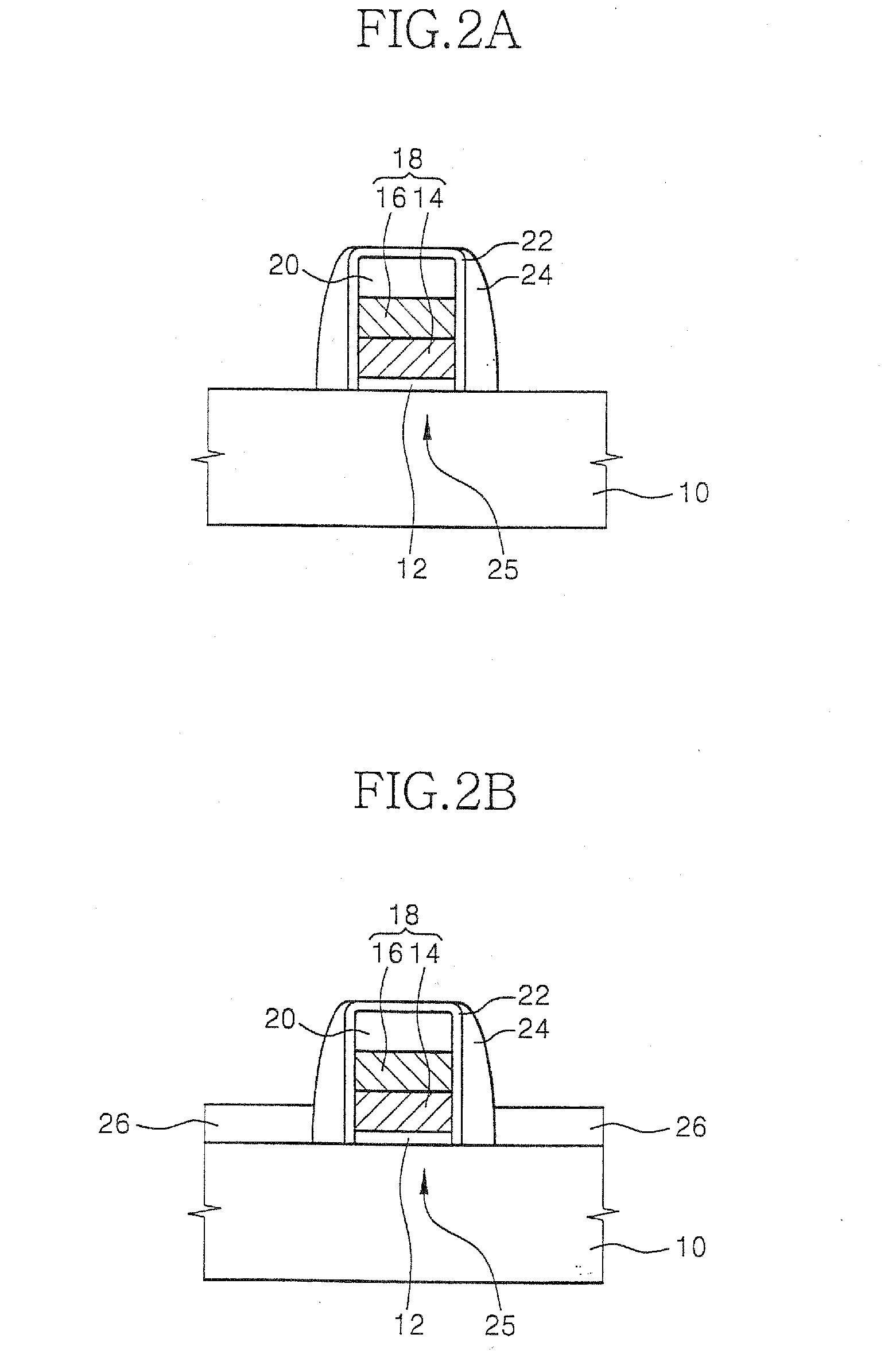

[0027]FIG. 1 is a cross-sectional view of a MOS transistor according to an embodiment of the invention.

[0028] Referring to FIG. 1, a gate structure 25 including a gate insulating layer 12 and a gate electrode 18 is formed on a semiconductor substrate 10. Optionally, the gate structure 25 further includes a gate capping layer 20 formed on the gate electrode 18. The gate capping layer 20 includes an insulating material such as silicon nitride or silicon oxide. In the present embodiment, the gate capping layer 20 is silicon nitride.

[0029] The gate electrode 18 is formed into a polycide structure in which a polysilicon layer 14 and a metal silicide layer 16 are successively stacked.

[0030] A first insulating layer 22 is formed on the top and the sides of the gate structure 25 (that is, t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More