Network-on-chip branch defining task mapping method

A task mapping and branch definition technology, applied in data exchange networks, digital transmission systems, electrical components, etc., can solve problems such as the inability to meet data transmission bandwidth and power consumption requirements, reduce CPU time, improve performance, and balance the system. The effect of network load

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0022] The present invention will be described in further detail below in conjunction with the accompanying drawings and specific embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

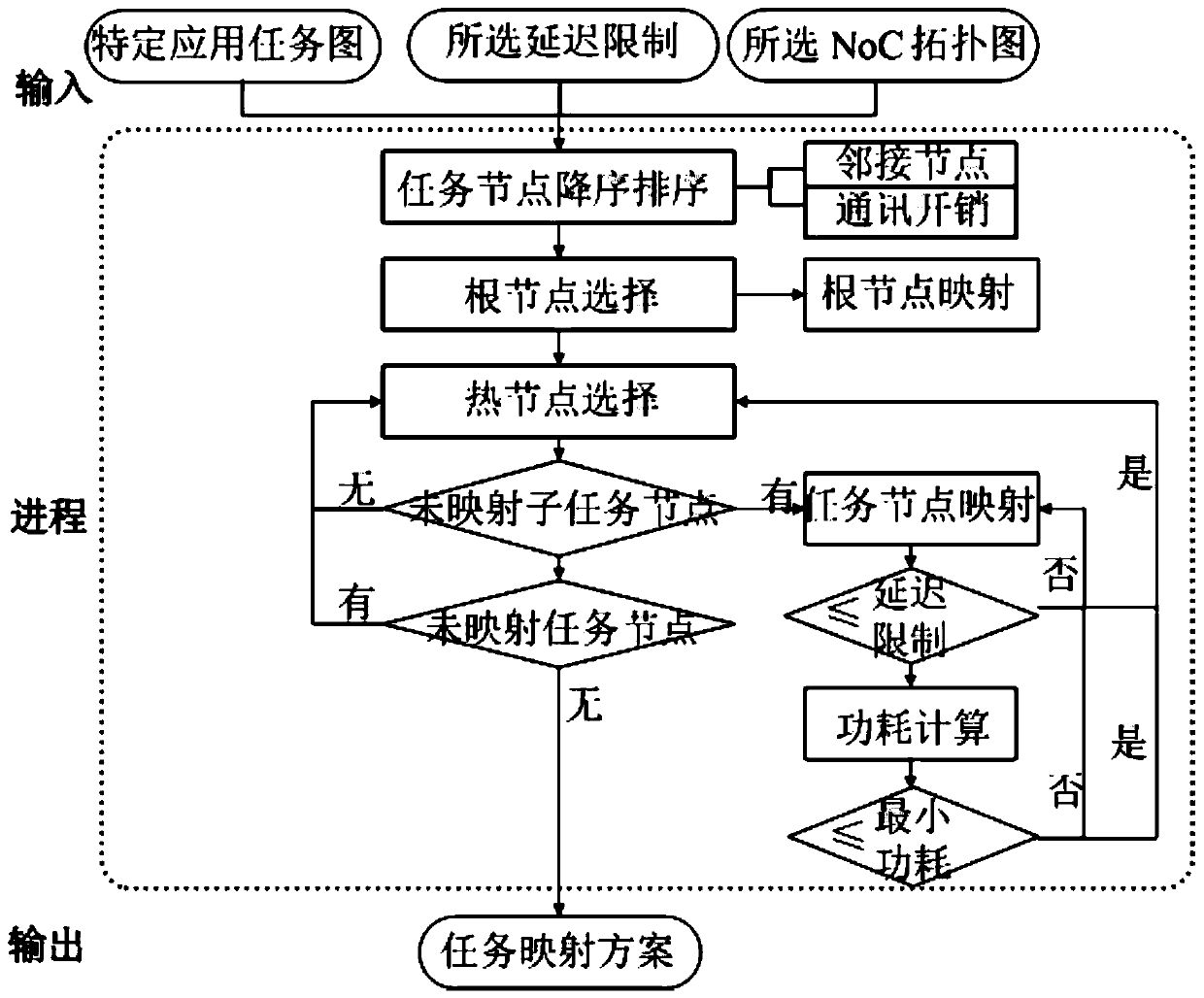

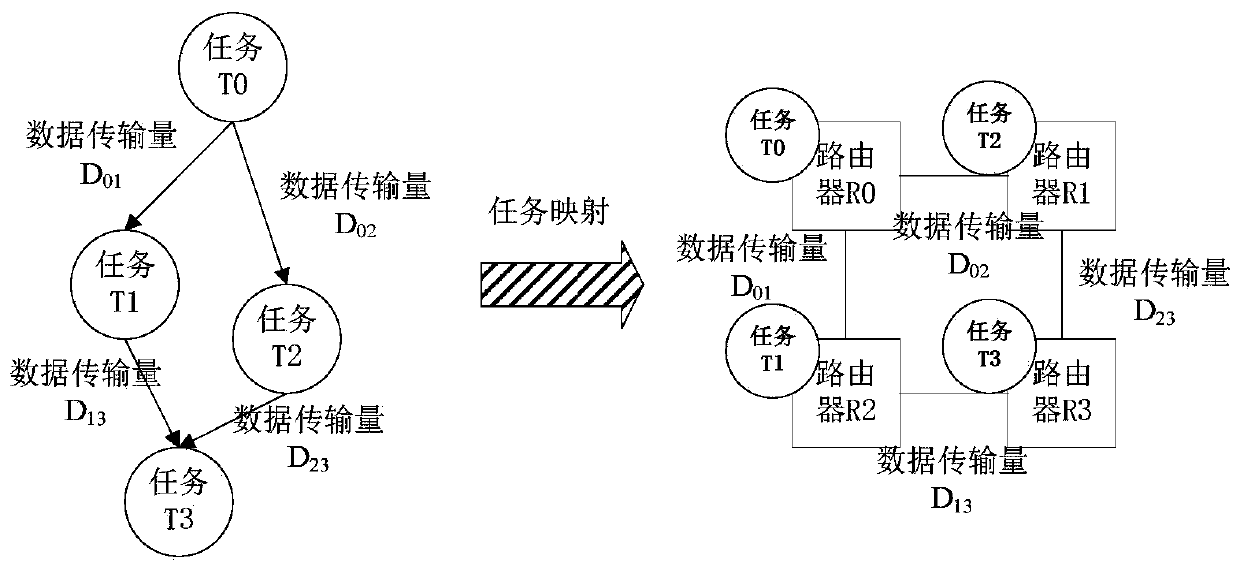

[0023] Referring to 1, an on-chip network branch definition task mapping method includes the following steps:

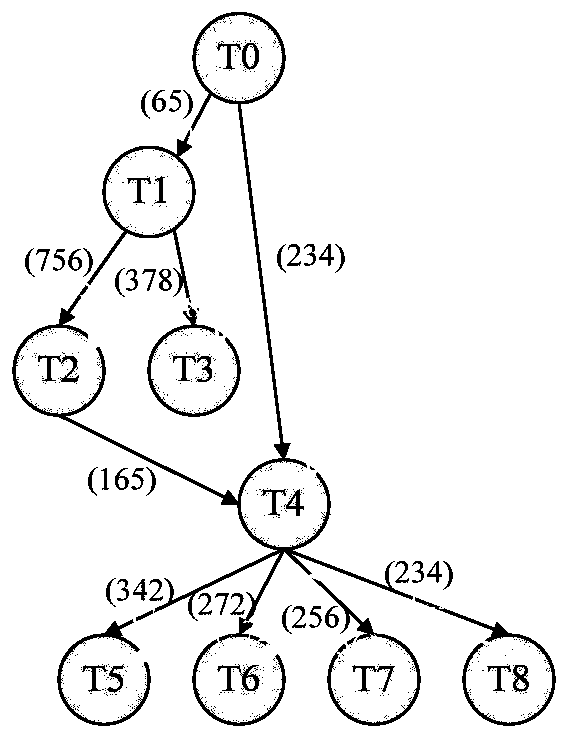

[0024] Determine the task graph of the application to be designed, the delay limit value of the connection edge of the two task nodes defined based on the transmission bandwidth requirements, and the selected NoC topology;

[0025] Sort the task nodes in descending order, select the root node mapping, start from the root node, perform path traversal on each branch of the tree search, select the hot node, and map the task nodes of the unmapped sub-task nodes to the NoC array. On the occupied routing nodes, until the mapping of all hot nodes is completed, all task nodes in th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More