Reading structure of mask memory

A memory and mask technology, applied in the field of readout structure of memory, can solve the problems of not setting control signals, influence of process tolerance, waste of chip area, etc., and achieve the effects of low power consumption, reduced power consumption, and safe reading

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0040] The specific implementation manners of the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. The following examples are used to illustrate the present invention, but are not intended to limit the scope of the present invention.

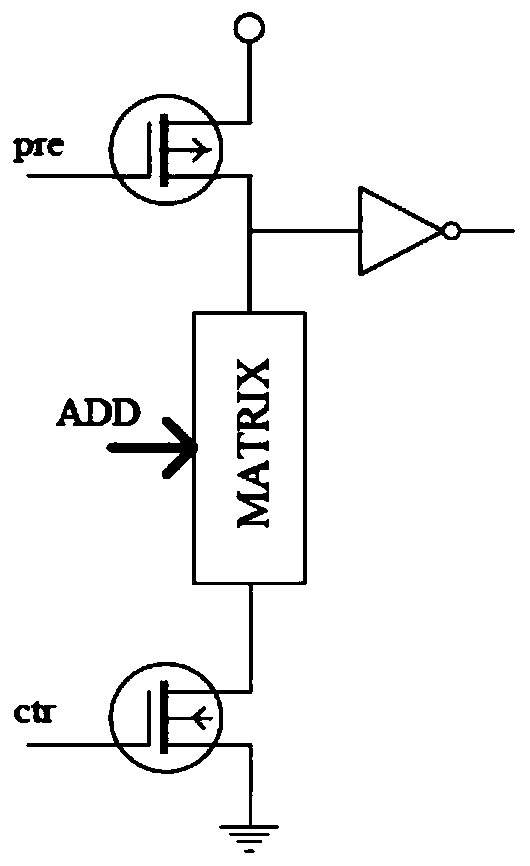

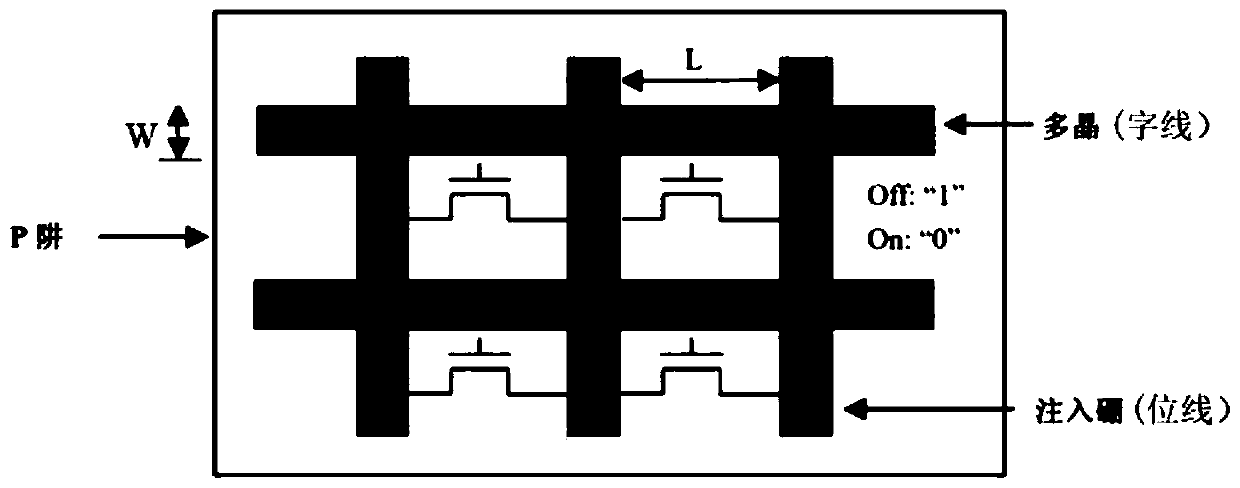

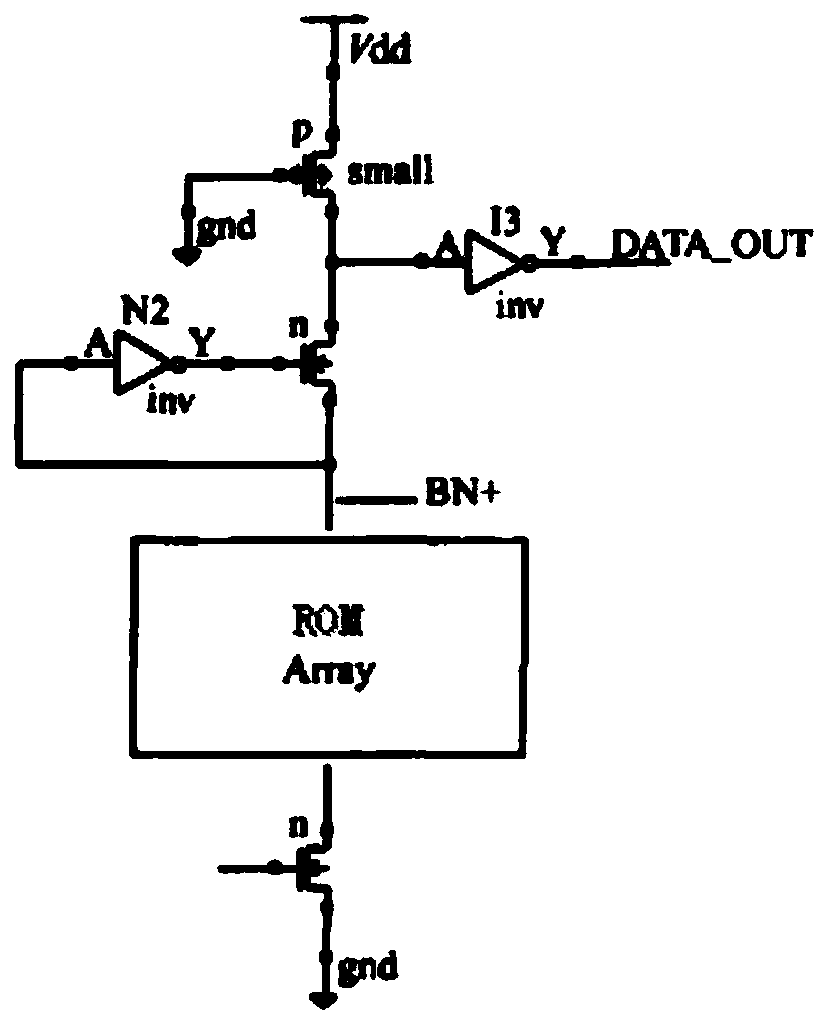

[0041] see Figure 6 to Figure 10 A readout structure of a mask memory according to a preferred embodiment of the present invention includes a MOS transistor P1 whose gate is connected to the PRE signal terminal, a MOS transistor N1 whose gate is connected to Vctrl, and the source of the MOS transistor N1 passes through the node RO Connected with the MaskROM storage array, the drain of MOS transistor N1 is connected to the drain of MOS transistor P1 to form node Net1, the source of MOS transistor P1 is connected to the power supply, and the readout structure of the mask memory also includes MOS transistor P2, MOS transistor P4, MOS transistor N2, MOS transistor N3, invert...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More