Three-dimensional NAND type ferroelectric memory, manufacturing method and operation method

A ferroelectric memory, a three-dimensional technology, applied in the field of memory, can solve the problems of reducing the storage window, limiting the reading speed, and increasing leakage, and achieves the effects of increasing the storage window, improving reliability, and reducing the electric field

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0045] The following will clearly and completely describe the technical solutions in the embodiments of the present invention with reference to the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are only some, not all, embodiments of the present invention. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the protection scope of the present invention.

[0046] In order to make the above objects, features and advantages of the present invention more comprehensible, the present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

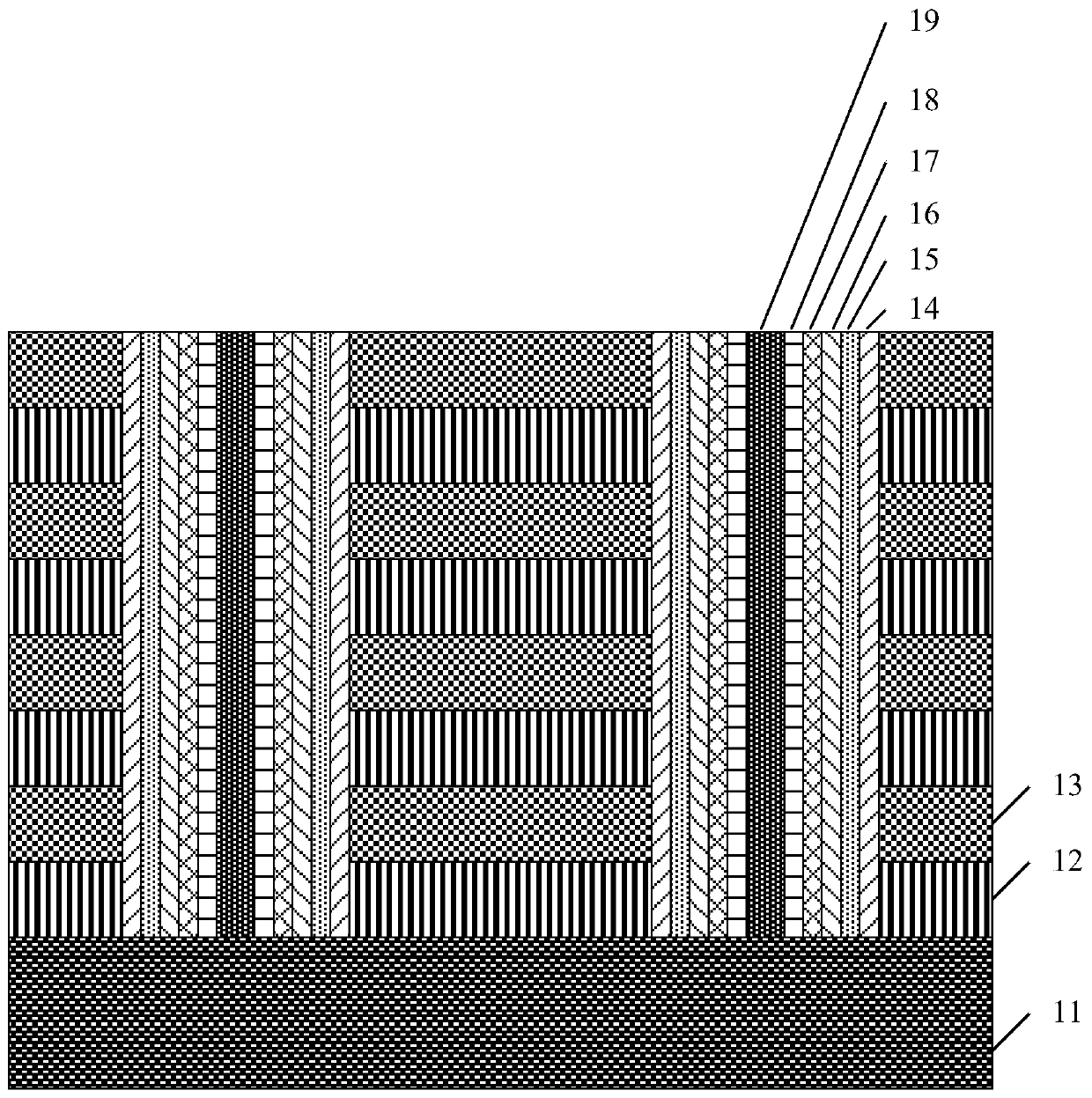

[0047] refer to figure 1 , figure 1 A schematic structural diagram of a three-dimensional NAND ferroelectric memory provided by an embodiment of the present invention, the three-dimensional NAND ferroelectric mem...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More