Multi-chip fan-out packaging structure with cavity and manufacturing method of multi-chip fan-out packaging structure

A packaging structure and multi-chip technology, applied in semiconductor/solid-state device manufacturing, electrical components, electrical solid-state devices, etc., can solve problems such as complex process, technical difficulty, and high cost, and achieve simplified process, reduced cost, and excellent electrical performance Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

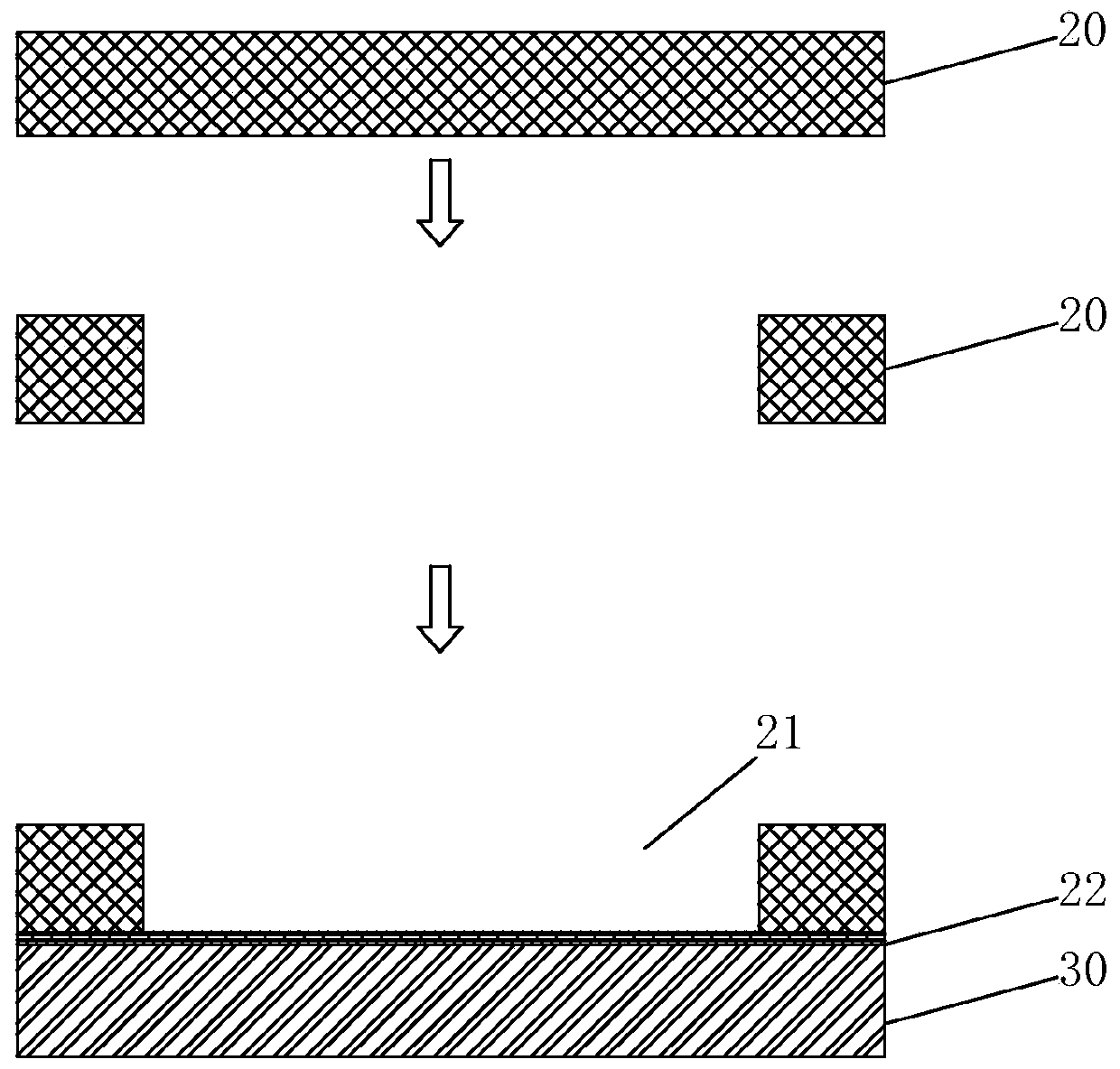

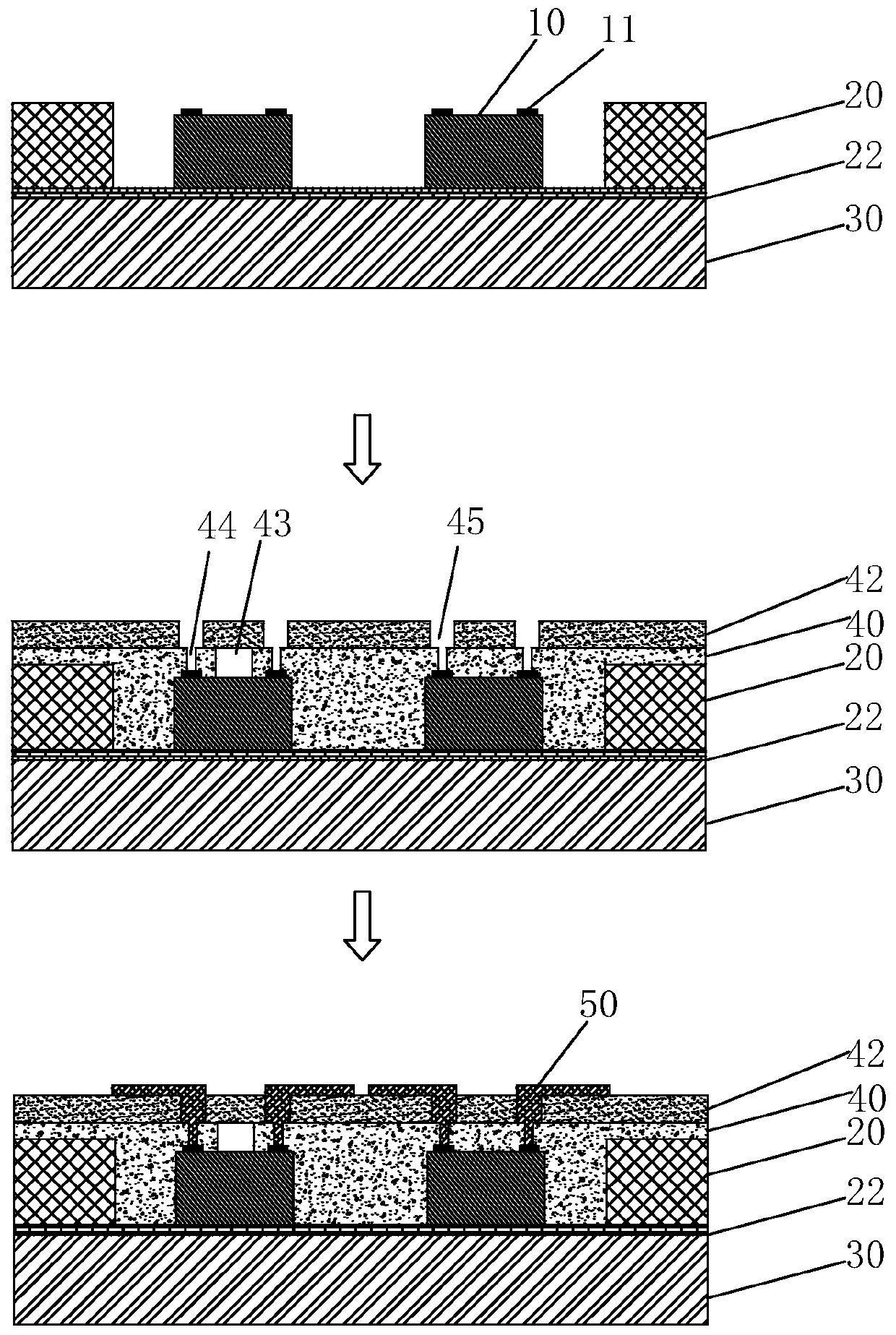

[0032] The present invention will be further described below through specific embodiments. The drawings of the present invention are only schematic diagrams for easier understanding of the present invention, and their specific proportions can be adjusted according to design requirements. The upper and lower relationship of the relative components in the figures described herein should be understood by those skilled in the art to refer to the relative positions of the components. Correspondingly, the upper side of the component is the front and the lower side is the back for easy understanding, so all The same components can be turned over to present, all of which should belong to the scope disclosed in this specification.

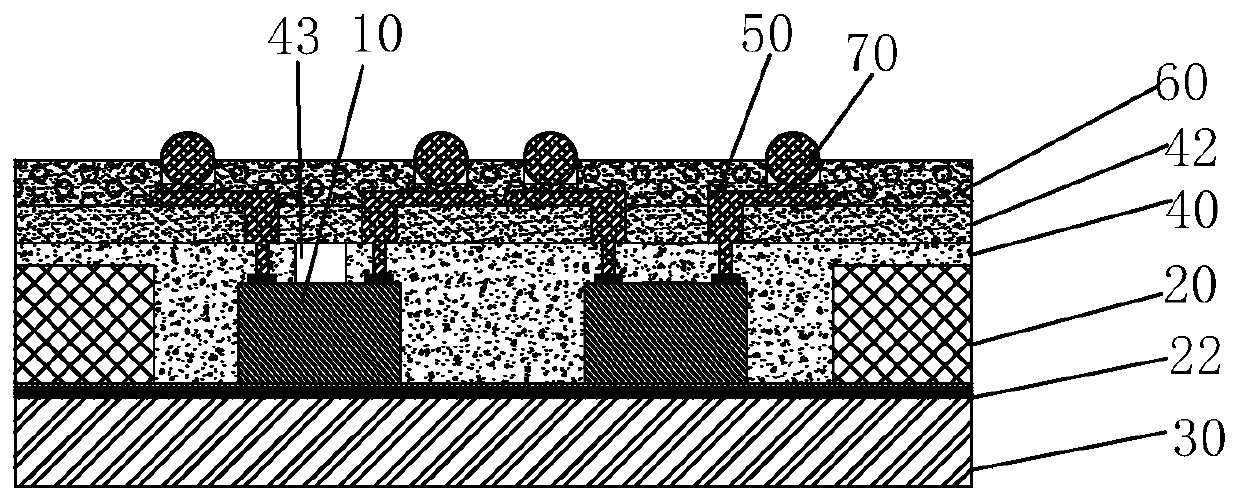

[0033] refer to figure 1 , a cavity-containing multi-chip fan-out packaging structure, including a chip 10, a first carrier 20, a second carrier 30, a filling layer 40, a metal rewiring layer 50, a first insulating layer 42, a second insulating layer 60 an...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More