A kind of vertical stack package chip and preparation method thereof

A vertical, chip-loading technology, applied in semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, semiconductor devices, etc., can solve difficult and complex problems, and achieve the effect of solving the size problem of IC products

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0035] This embodiment provides a multilayer substrate and its preparation method, such as Figure 1-6 shown. The multilayer substrates of this embodiment are connected by connecting pins, and the multilayer substrates are prepared as follows:

[0036] 1. Packaging and interconnection structure design and production:

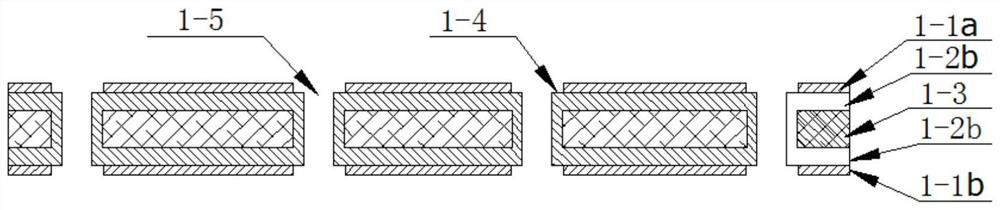

[0037] 1) Substrate manufacturing: figure 1 It is shown as a side view of substrate A, including upper ink layer 1-1a, circuit layer 1-2b, lower ink layer 1-1b, core board layer 1-3; through-hole annular pad 1-4, connection holes for upper and lower circuit layers And interconnect pinholes 1-5, which can be obtained by laser drilling or mechanical drilling.

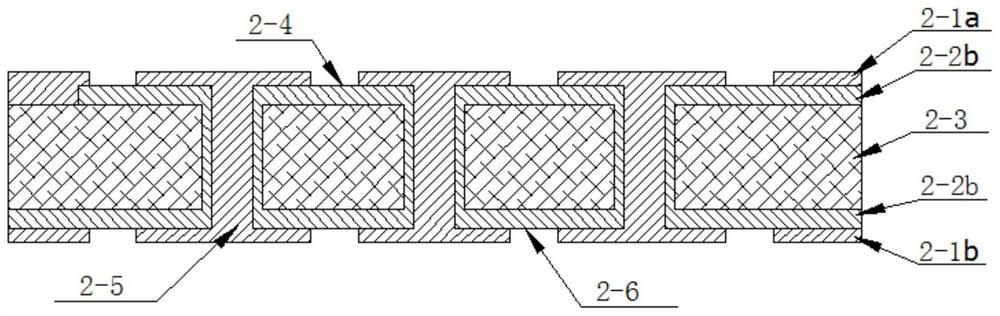

[0038] figure 2 It is shown as a side view of substrate B, including upper ink layer 2-1a, circuit layer 2-2b, lower ink layer 2-1b, core board layer 2-3; circular pad 2-4, connection hole 2 of upper and lower circuit layers -5, round or square pads 2-6, used to connect with other PCB boards.

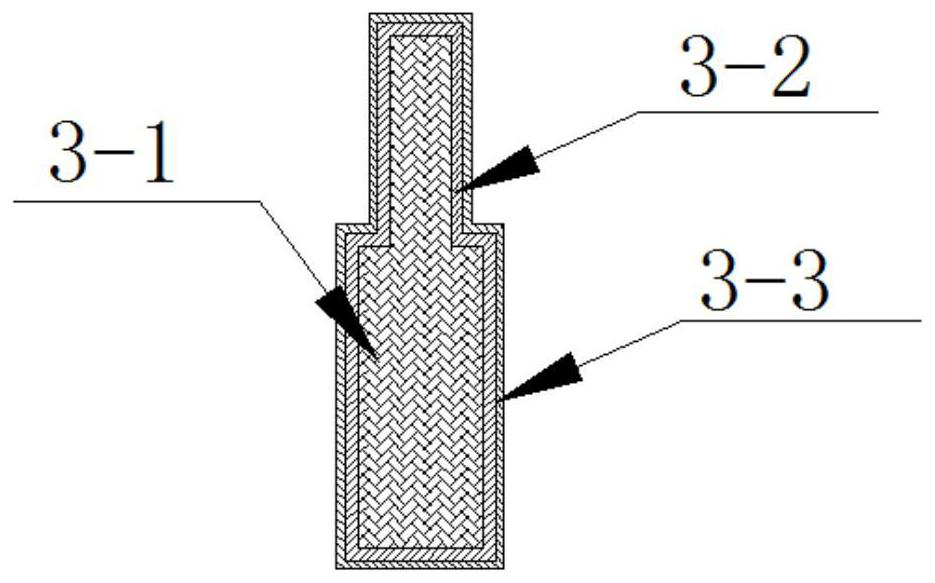

[0039...

Embodiment 2

[0051] This embodiment provides a multilayer substrate and its preparation method, such as Figure 7-10 shown.

[0052] The multi-layer substrate in this embodiment is connected by a flexible board to realize information transmission, and the flexible board includes an ink part and first welding points and second welding points located on both sides of the ink part. The multi-layer substrate includes a substrate A at the bottom, a substrate B at the top, and a plurality of connecting copper columns vertically arranged between the substrate B and the substrate A, and a soft board arranged between the substrate B and the substrate A, so The first welding point of the flexible board is connected to the substrate B, and the second welding point is connected to the substrate A, and the area of the substrate B is different from that of the substrate A. By adjusting the height of the copper pillars, the substrate B and the substrate A can be adjusted.

[0053] The whole process o...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com