PMOS device stress layer structure and formation method thereof

A stress layer and device technology, applied in the fields of semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve problems such as the decline of electrical properties of devices, and achieve the effect of reducing volume difference, improving electrical properties, and accelerating growth rate.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

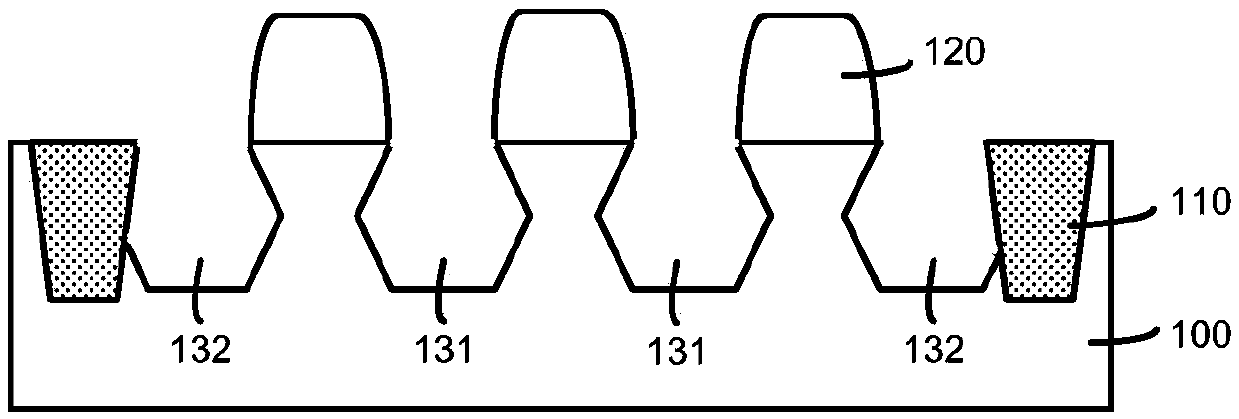

[0027] As mentioned above, in the existing PMOS devices, there is a problem of large volume difference of the stress layer at different positions, which further affects the performance of the semiconductor device.

[0028] After research, it is found that the reason for the above problems is: when forming the stress layer of the PMOS device, the growth rate of SiGe between the gate structure and the shallow trench isolation structure is relatively slow, and the growth is easy to stop at the crystal plane of SiGe. Finally, the volume of the stress layer here is smaller.

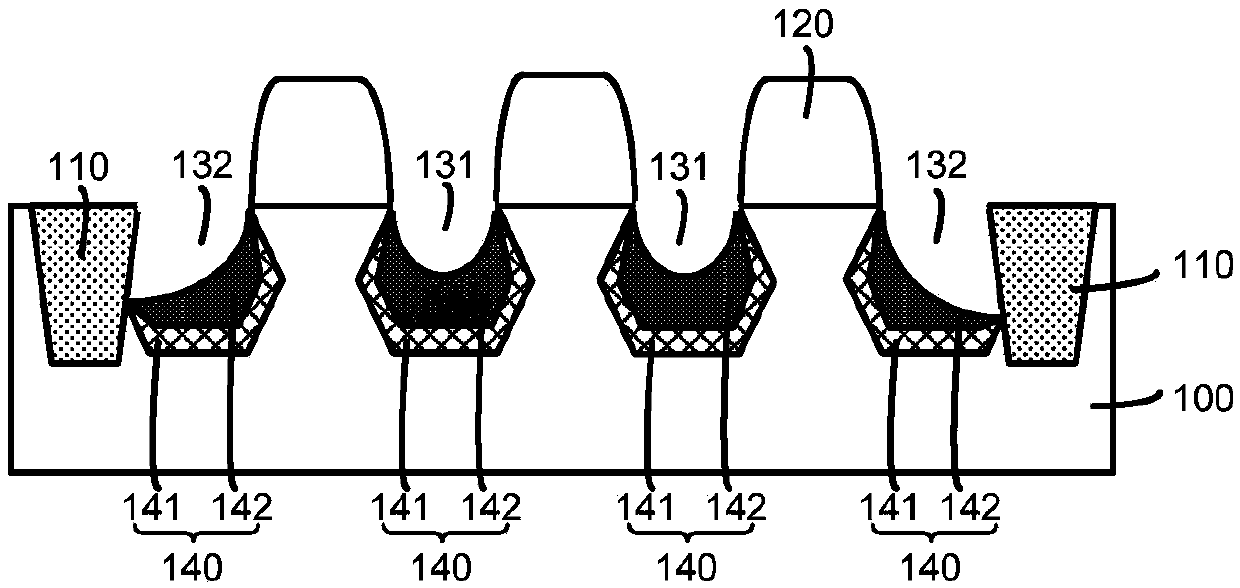

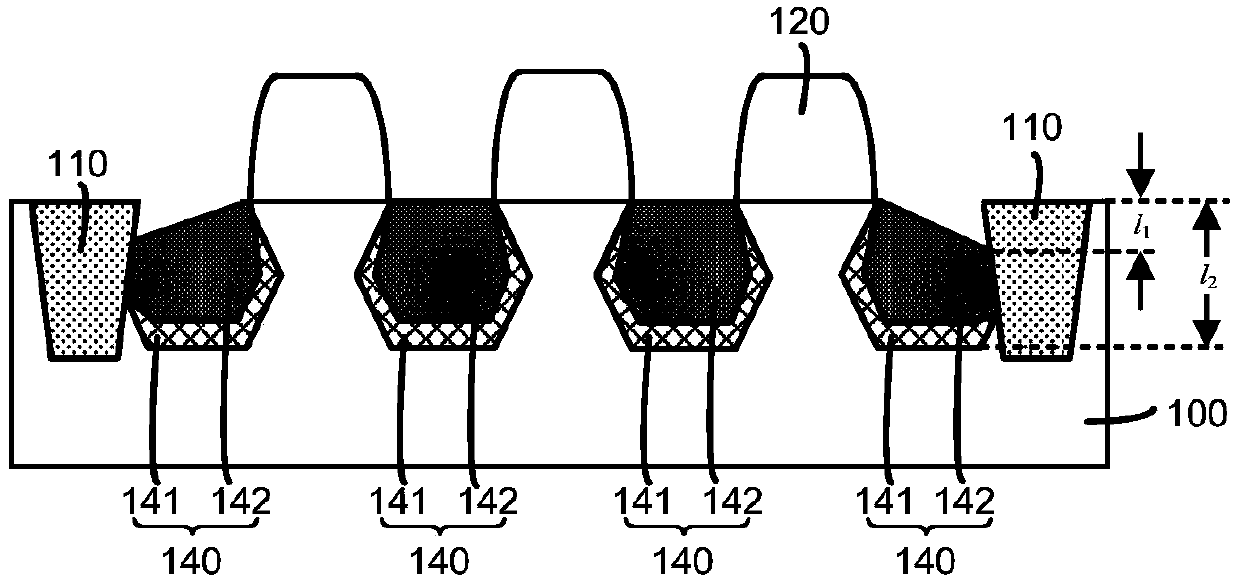

[0029] In order to solve this problem, the present invention provides a method for forming the stress layer structure of a PMOS device. When the SiGe between the gate structure and the shallow trench isolation structure stops growing on the crystal plane of SiGe, heat treatment is performed to destroy The crystal plane of SiGe continues to grow.

[0030] Various exemplary embodiments of the present inventi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More