Process mapping method for FPGA with specific structure

A technology of process mapping and mapping scheme, which is applied in special data processing applications, instruments, calculations, etc., and can solve problems such as unusable and inability to obtain better solutions for mapping objects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0052] It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

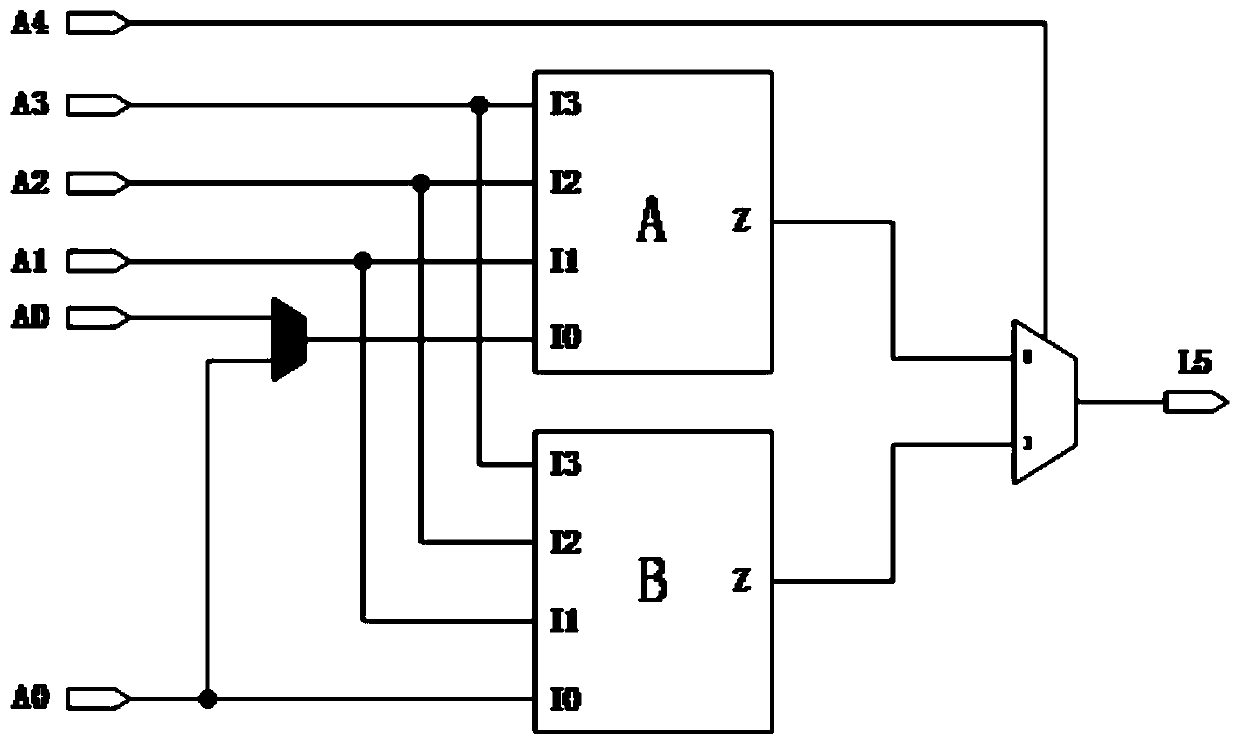

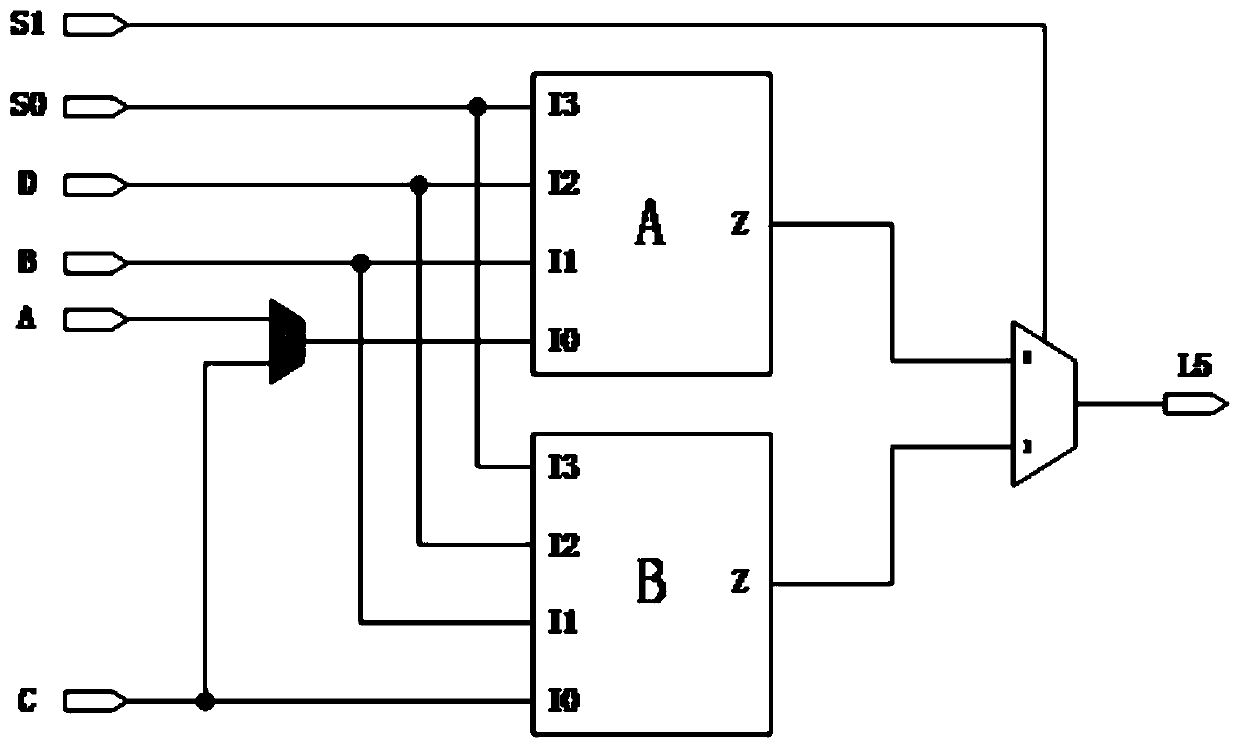

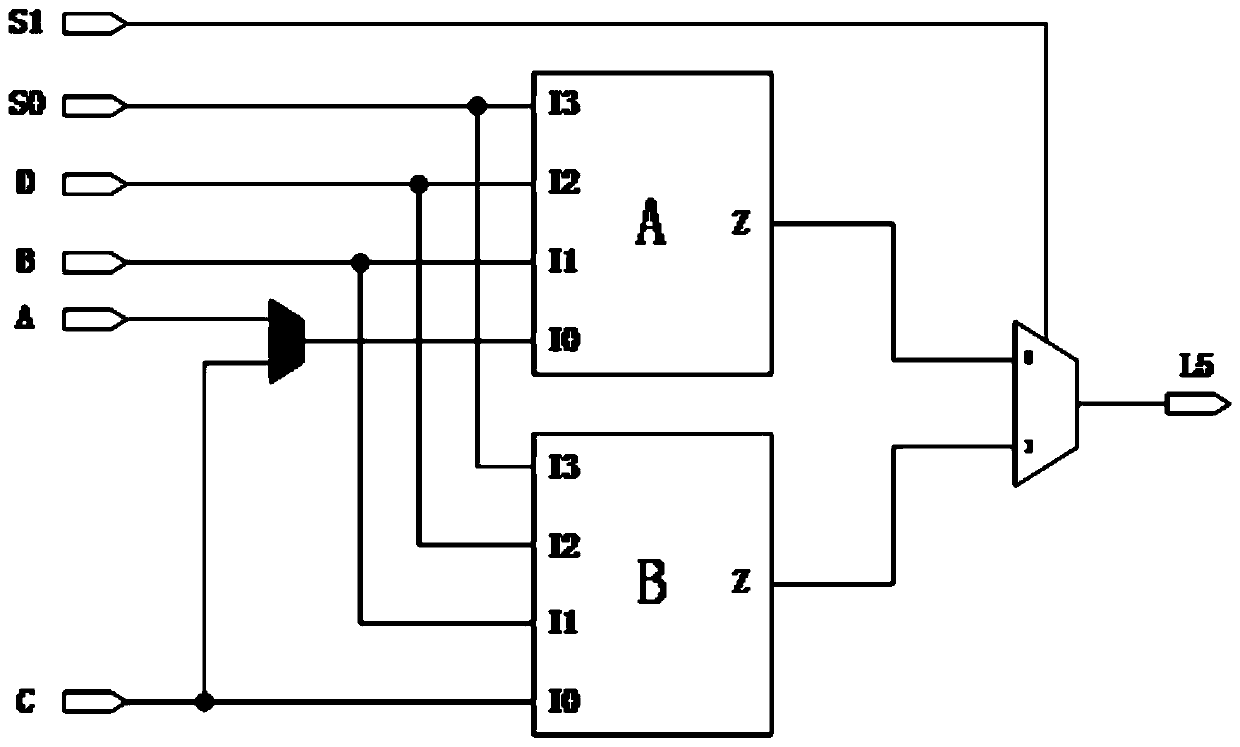

[0053] The FPGA has flexible programmable features, and the programmable features of the combinational logic are mainly realized through a look-up table (LUT, Look Up Table), and the LUT is essentially a RAM (Random Access Memory, random access memory). For example, a LUT with 5 inputs can be regarded as a 32x1 RAM with 5 address lines, which can realize all combinatorial logic within any 5 inputs. Such as Picture 1-1 As shown, the FPGA with a unique structure that the present invention faces has a special LUT structure, and this LUT structure has 6 input terminals, which can realize all combinatorial logics within any 5 inputs, such as Figure 1-2 As shown, the LUT can be configured as a MUX mode—LUT5M to realize the function of MUX4 (4 to 1 multiplexer). Simultaneously the FPGA that the present invention faces al...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More