SRAM circuit yield analysis method based on Bayesian model

A technology of Bayesian model and analysis method, which is applied in the field of SRAM circuit yield analysis based on Bayesian model, and can solve problems such as a large amount of running time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

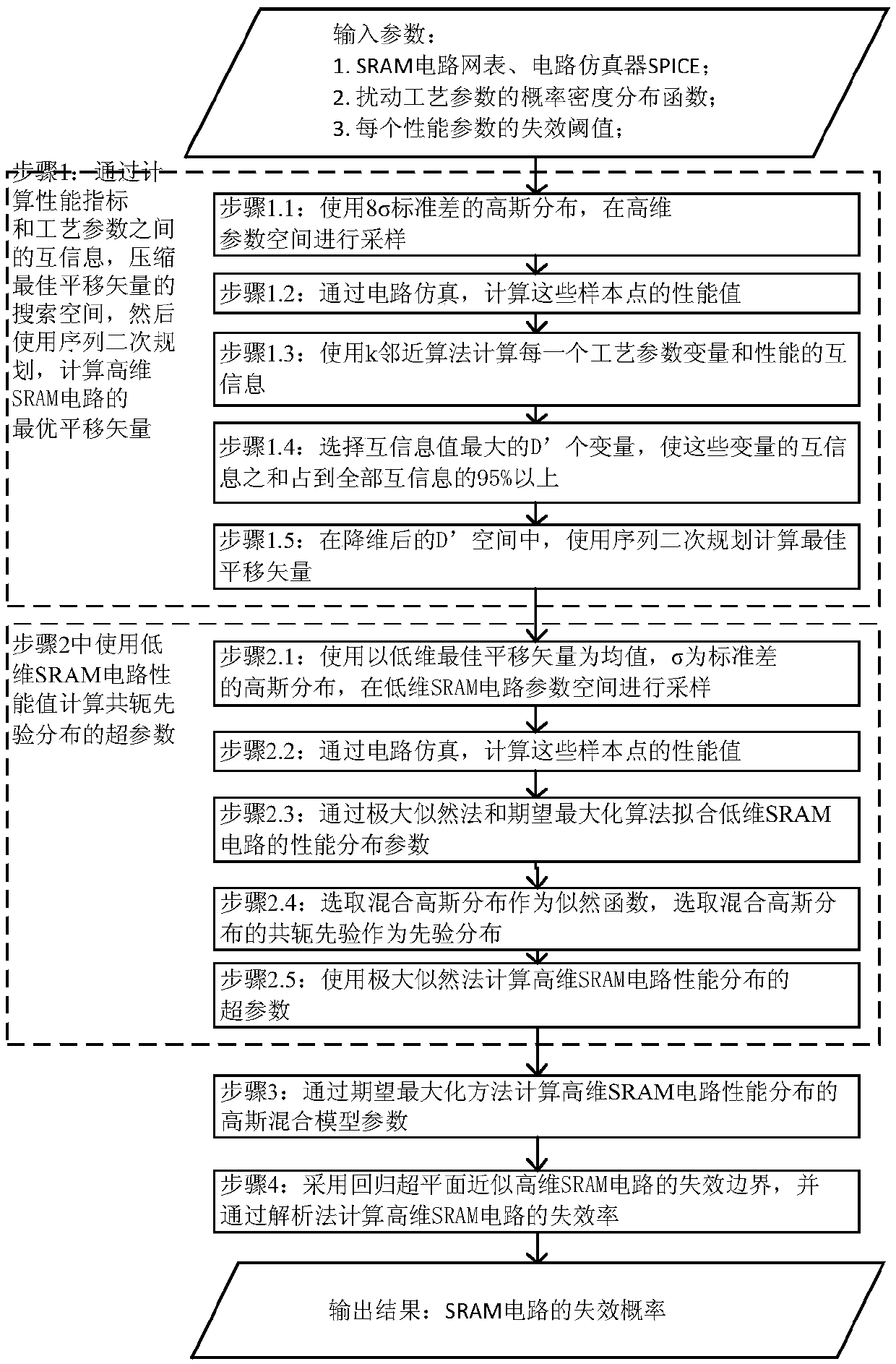

Method used

Image

Examples

Embodiment Construction

[0139] Now, the method of the present invention will be described through the implementation process of specific examples.

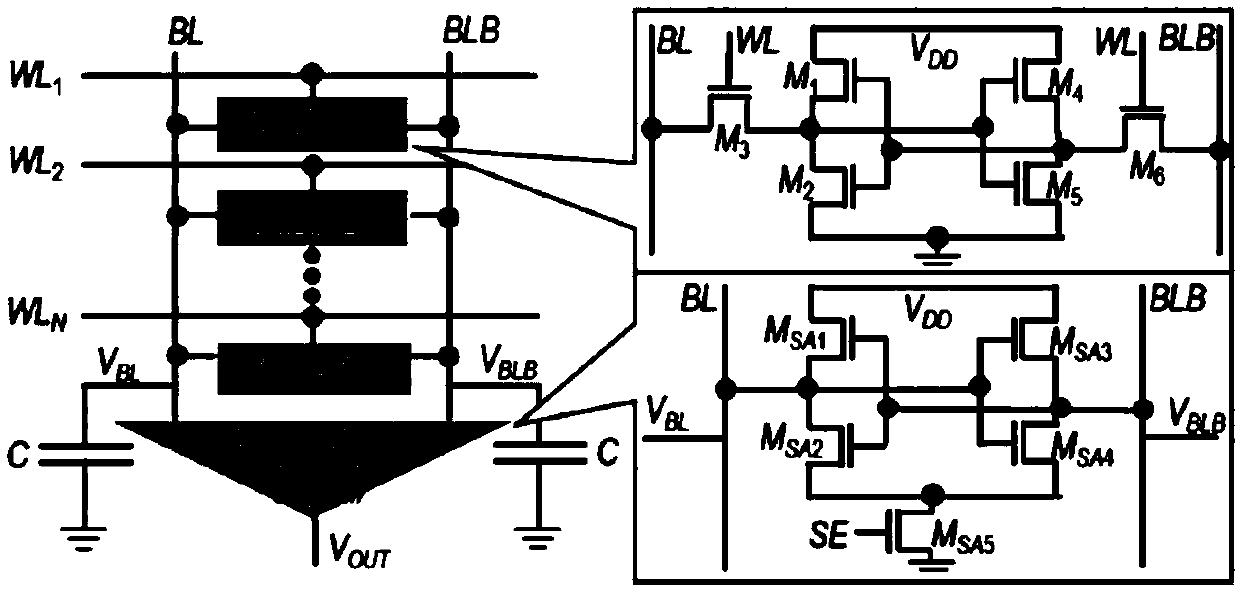

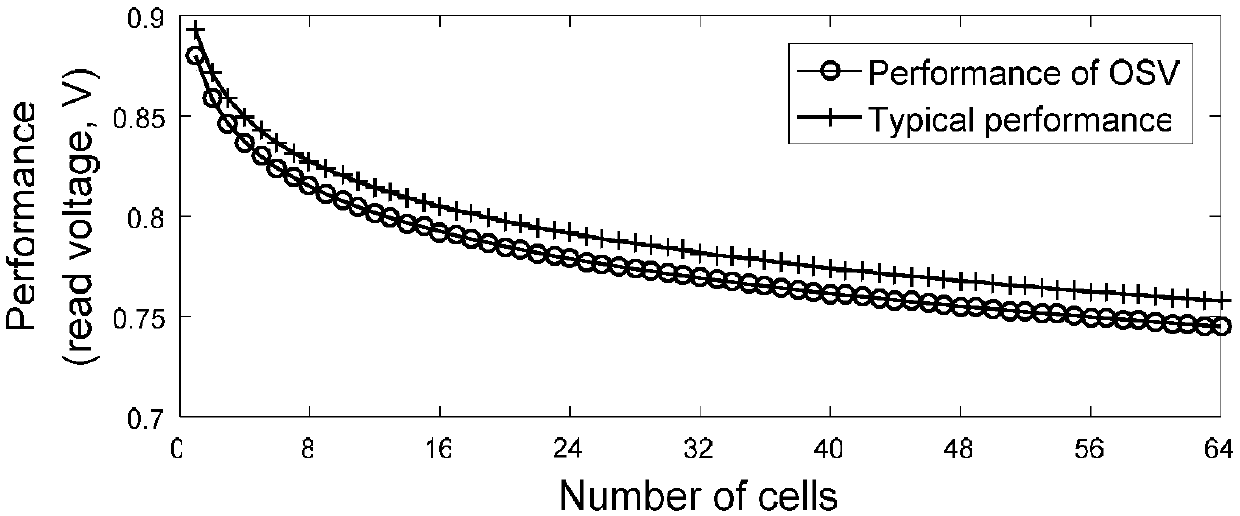

[0140] In order to verify the accuracy and efficiency of the inventive method, the application is verified by two test cases of read operation failure and write operation failure of SRAM array, all test cases use 28nm CMOS process library, adopt HSPICE tool to carry out circuit simulation, although SUS can handle high-dimensional situations, but usually requires more than 106 sample points, which is unbearable for large-scale circuit simulation; the accurate value of the failure rate is obtained on the basis of enough sample points through the most direct MNIS method, Its optimal translation vector is calculated by the MFRIS method. Min-Norm Importance Sampling (MNIS) is an earlier method of importance sampling, which moves the original sampling distribution to the failure point with the smallest two-norm for sampling. Therefore, in the experiment of the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More