Verification platform and verification method for symmetric encryption algorithm based on UVM

A technology of symmetric encryption algorithm and verification platform, which is applied in the direction of faulty hardware testing method, faulty computer hardware detection, calculation, etc., can solve the problems of inability to realize reuse and low efficiency of verifying symmetric encryption algorithm, and achieve good portability and reliability Reusability, clearly structured effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

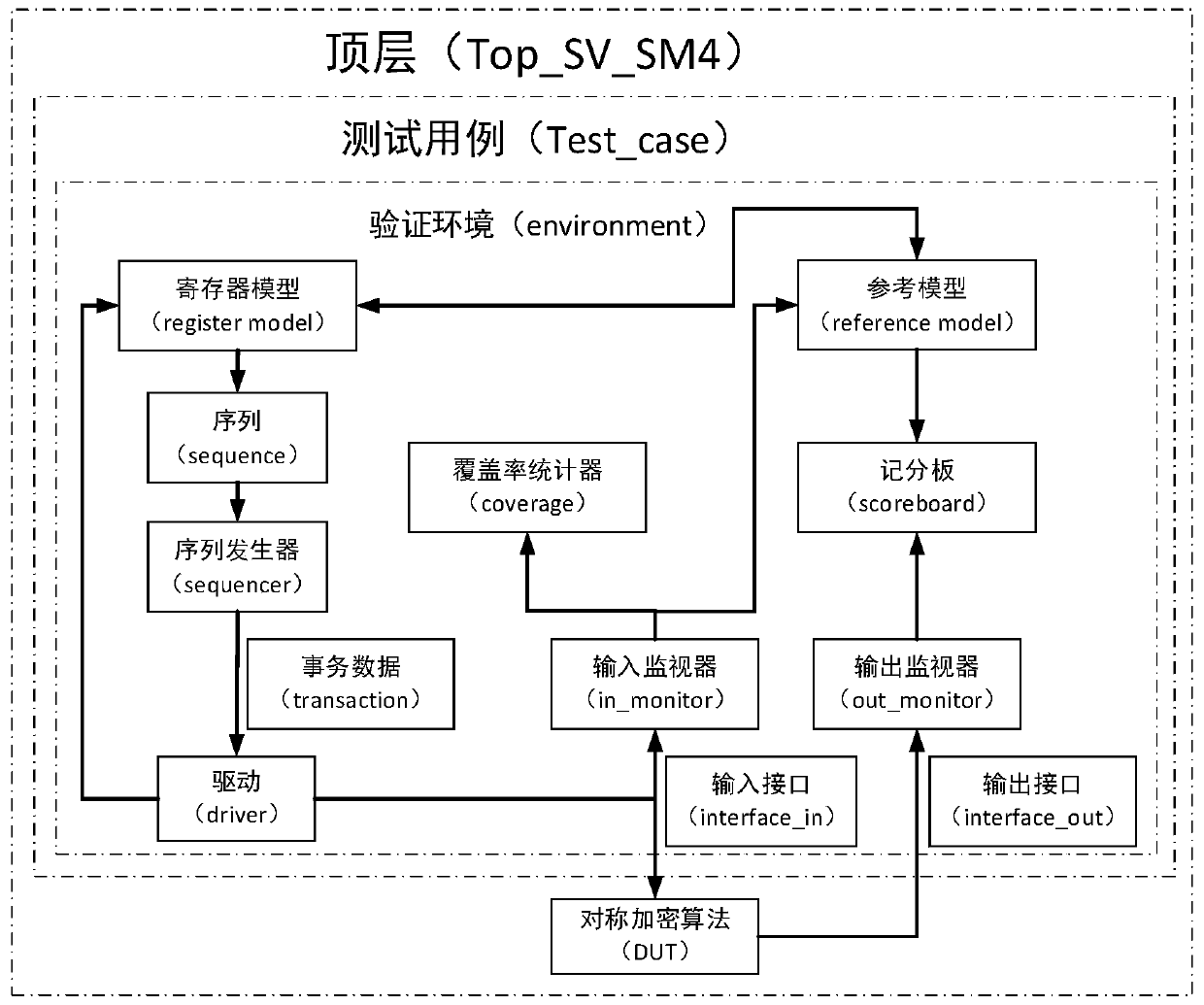

[0047] This embodiment provides a verification platform based on a UVM-based symmetric encryption algorithm, such as figure 1 , including the top layer, test cases and verification environment, the verification environment is derived from uvm_env, and the required components are integrated and connected to work, wherein: the top layer contains the DUT module, and the top layer is connected to the data between the DUT module and the test case At the same time, the DUT module and the verification environment compare the operation results to achieve the purpose of verifying the DUT module; the verification environment can realize the connection and data transmission of each component, and complete the system verification function.

[0048] The components include register models, sequencers, sequences, transaction data, drivers, coverage counters, input monitors, output monitors, scoreboards, reference models, input interfaces, and output interfaces, where:

[0049] The register m...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More