A hardware retransmission circuit and method for aggregated retransmission of data subframes

A data frame and circuit technology, applied in digital transmission systems, electrical components, transmission systems, etc., can solve the problems of throughput impact, increase the load of the main processor, and low efficiency, so as to speed up processing speed, improve transmission throughput, The effect of reducing the load

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

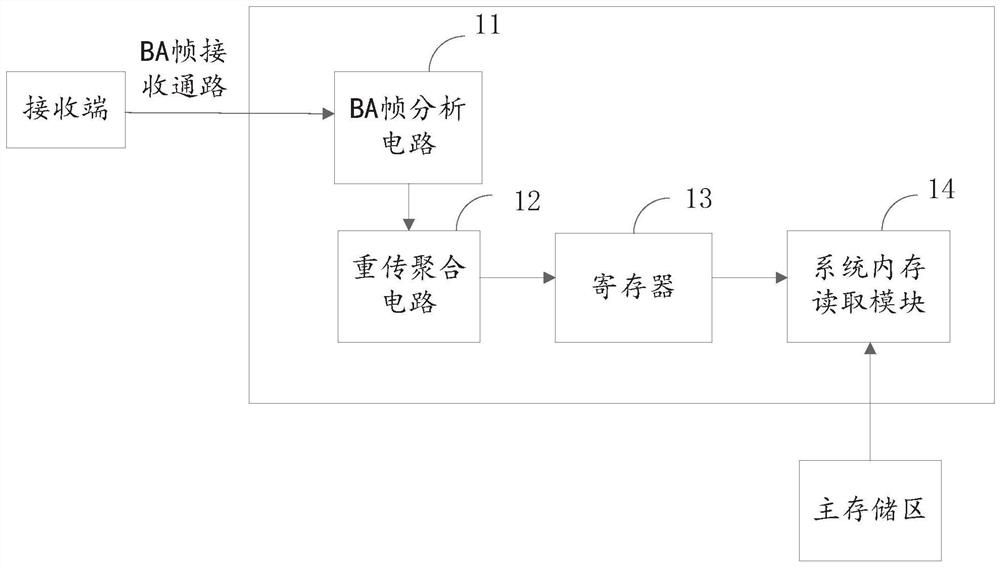

[0027] Such as figure 1 As shown, this embodiment provides a hardware retransmission circuit for aggregated retransmission of data subframes, including:

[0028] A register 13, wherein N descriptors corresponding to N initial transmission subframes are stored in the register 13, where N is a positive integer greater than 1, and the register 13 only stores descriptors, which is more economical than directly storing the initial transmission subframes Register 13 scale. The N descriptors corresponding to the N initial transmission subframes stored in the register 13 may be given by the control layer.

[0029] Single block confirmation BA frame analysis circuit 11, configured to analyze the received current BA frame to obtain the first information associated with the retransmission subframe, the current BA frame is used to represent each subframe in the aggregation frame sent last time The frame transmission situation, the initial transmission subframe includes the retransmissio...

Embodiment 2

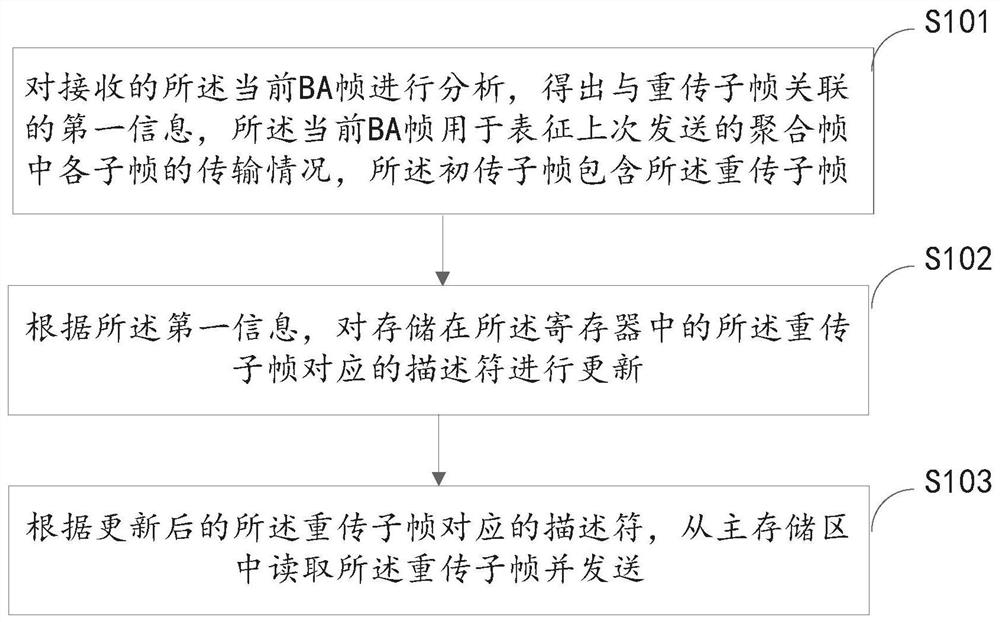

[0078] Based on the same inventive concept, such as figure 2 As shown, this embodiment provides a hardware retransmission method for aggregated retransmission of data subframes, which is applied to any hardware retransmission circuit described in Embodiment 1, including:

[0079] Step S101: Analyze the received BA frame to obtain the first information associated with the retransmission subframe, the current BA frame is used to represent the transmission status of each subframe in the aggregation frame sent last time, the initial transmission The subframe includes the retransmission subframe;

[0080] Step S102: update the descriptor corresponding to the retransmission subframe stored in the register according to the first information;

[0081] Step S103: According to the updated descriptor corresponding to the retransmission subframe, read the retransmission subframe from the main storage area and send it.

[0082] As an optional embodiment, the hardware retransmission meth...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More