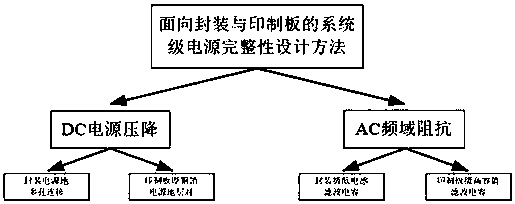

System-level power supply integrity design method for packaging and printed board

A power integrity and design method technology, applied in computer-aided design, calculation, electrical digital data processing, etc., can solve problems such as power distribution network without packaging, save layout and wiring space, improve current-carrying characteristics, and reduce DC The effect of pressure drop

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

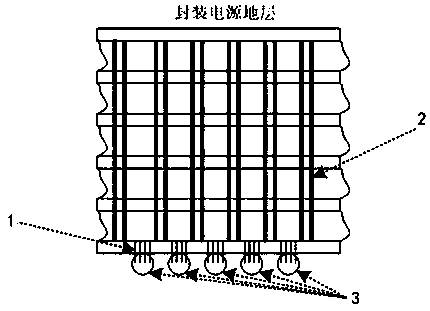

[0022] The specific embodiment of the specific solution of the present invention will be further elaborated in conjunction with the accompanying drawings.

[0023] Those of ordinary skill in the art can understand that all or part of the steps carried by the methods of the above embodiments can be completed by instructing related hardware through a program, and the program can be stored in a computer-readable storage medium. When, one or a combination of the steps of the method embodiment is included. Each functional unit in each embodiment of the present invention may be integrated into one processing module, or each unit may physically exist separately, or two or more units may be integrated into one module. The above-mentioned integrated modules can be implemented in the form of hardware or in the form of software function modules. If the integrated modules are realized in the form of software function modules and sold or used as independent products, they can also be stor...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More