Chip testing device and system

A technology of chip testing and testing equipment, which is applied in the direction of measuring equipment, non-contact testing, single semiconductor device testing, etc., can solve the problems of inability to obtain hotspot positioning points, inability to use laser hotspot mode, etc., to improve the test range and expand the test function, cost reduction effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] Various embodiments of the invention will be described in more detail below with reference to the accompanying drawings. In the various drawings, the same elements are denoted by the same or similar reference numerals. For the sake of clarity, various parts in the drawings have not been drawn to scale.

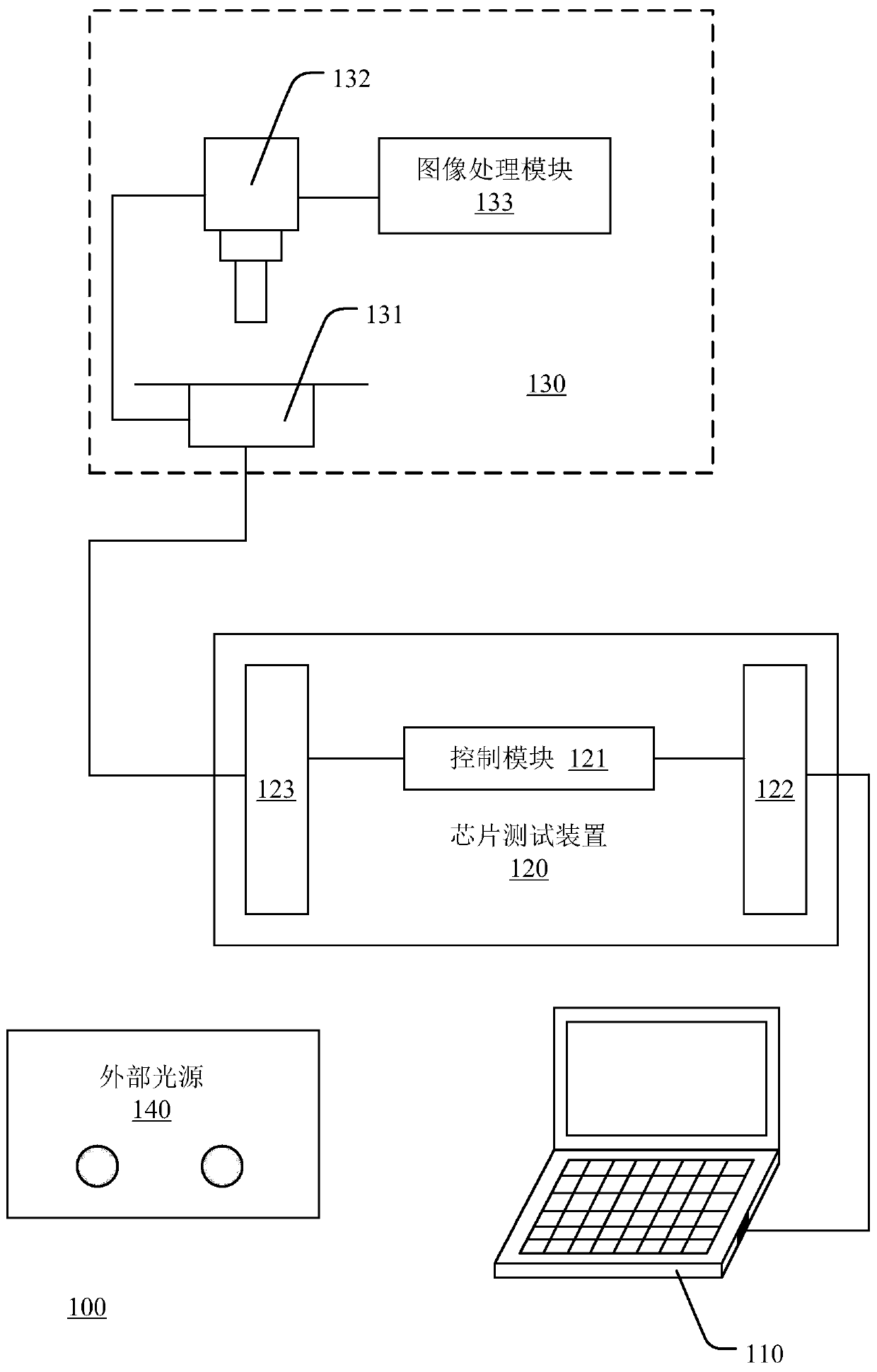

[0029] figure 1 A prior art chip testing system 100 is shown. The chip testing system 100 includes a host computer 110 , a testing device 120 and a positioning device 130 .

[0030] Wherein, the upper computer 110 is, for example, a server that can control all operations in chip testing, and is used to generate control signals, and the control signals are, for example, used to control logic management and processes in the chip testing process. Among them, logic management includes the working state or test mode of the chip during testing. This working state is a certain state, such as Program (writing), Erase (erasing) or Read (reading). In this state, , the chip to...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More