Debugging system for RISC-V processor and debugging signal transmission method

A RISC-V, signal transmission technology, applied in the field of signal transmission, can solve the problems of use and inability, achieve the effect of low design complexity, small number of pins, and meet debugging requirements

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0040] The present invention will be further explained below in conjunction with the drawings and specific embodiments.

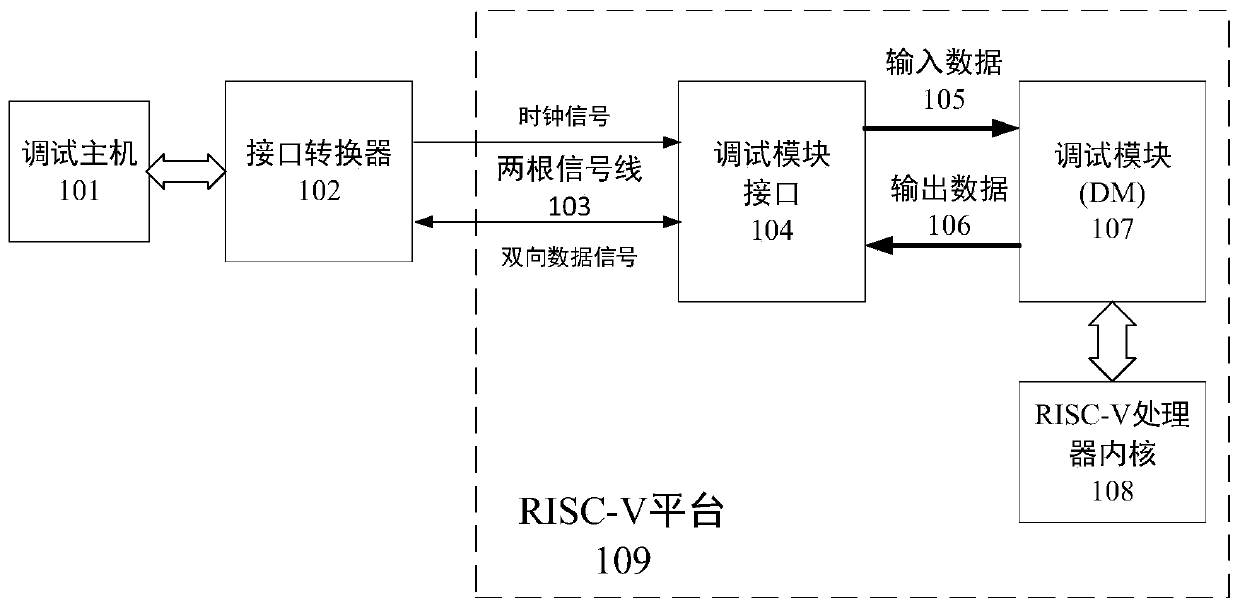

[0041] Such as figure 2 As shown, a debugging system for a RISC-V processor includes a debugging host 101, an interface converter 102, a debugging module interface 104, a debugging module 107, and a RISC-V processor core 108, a debugging module interface 104, and a debugging module 107 And the RISC-V processor core 108 together form the RISC-V platform 109. The debugging host 101 and the interface converter 102 have a two-way communication connection. The interface converter 102 and the debugging module interface 104 are connected by two signal lines 103, a clock signal line and a data signal line. The data signal line is a bidirectional signal line. The debugging module interface 104 has two pins, two Each pin is connected to two signal wires 103, and the debugging module interface 104 can be integrated on the debugging module 107.

[0042] The debugging hos...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com