Power semiconductor module packaging structure

A power semiconductor and module packaging technology, applied in the direction of semiconductor devices, semiconductor/solid-state device components, electric solid-state devices, etc., can solve the power semiconductor module current sharing, heat dissipation, thermal stress, reliability affecting the reliable use of power semiconductor modules, Reducing the reliability of power semiconductor modules, the uniformity of power semiconductor modules, the inability to directly manufacture single-chip chips, etc., to reduce costs, reduce the number of chips, and reduce the number of pins

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] The implementation of the present invention will be described in detail below with reference to the accompanying drawings and embodiments, so as to fully understand how the present invention applies technical means to solve technical problems and achieve the realization process of technical effects and implement them accordingly. It should be noted that, as long as there is no conflict, each embodiment of the present invention and each feature in each embodiment can be combined with each other, and the technical solutions formed are all within the protection scope of the present invention.

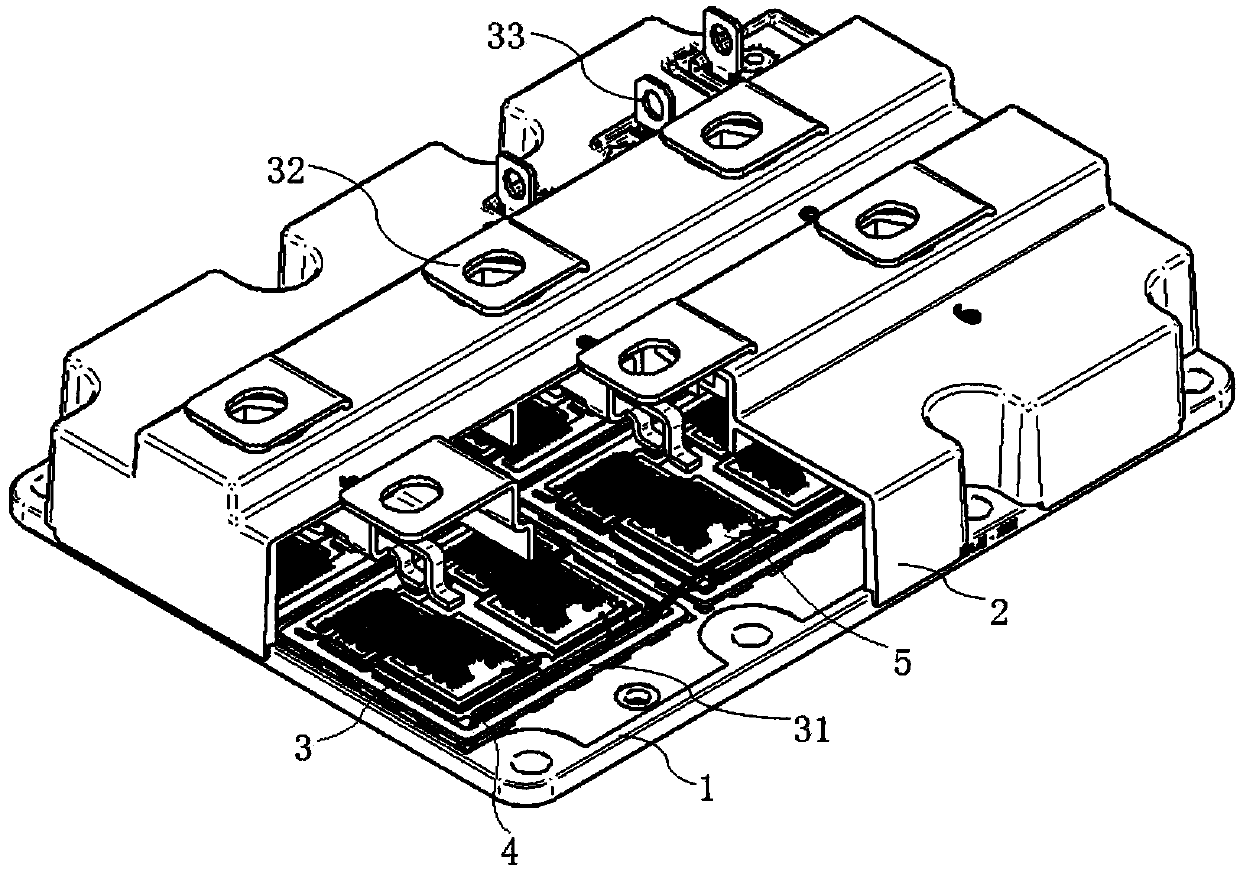

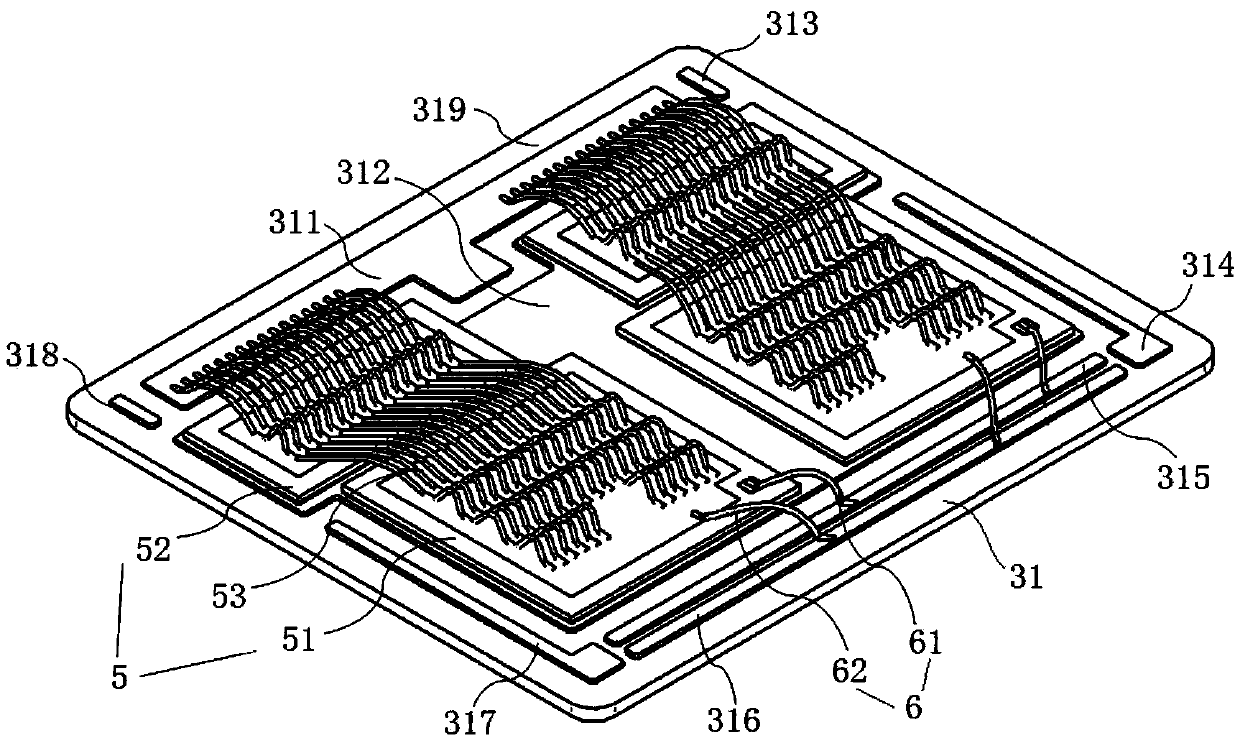

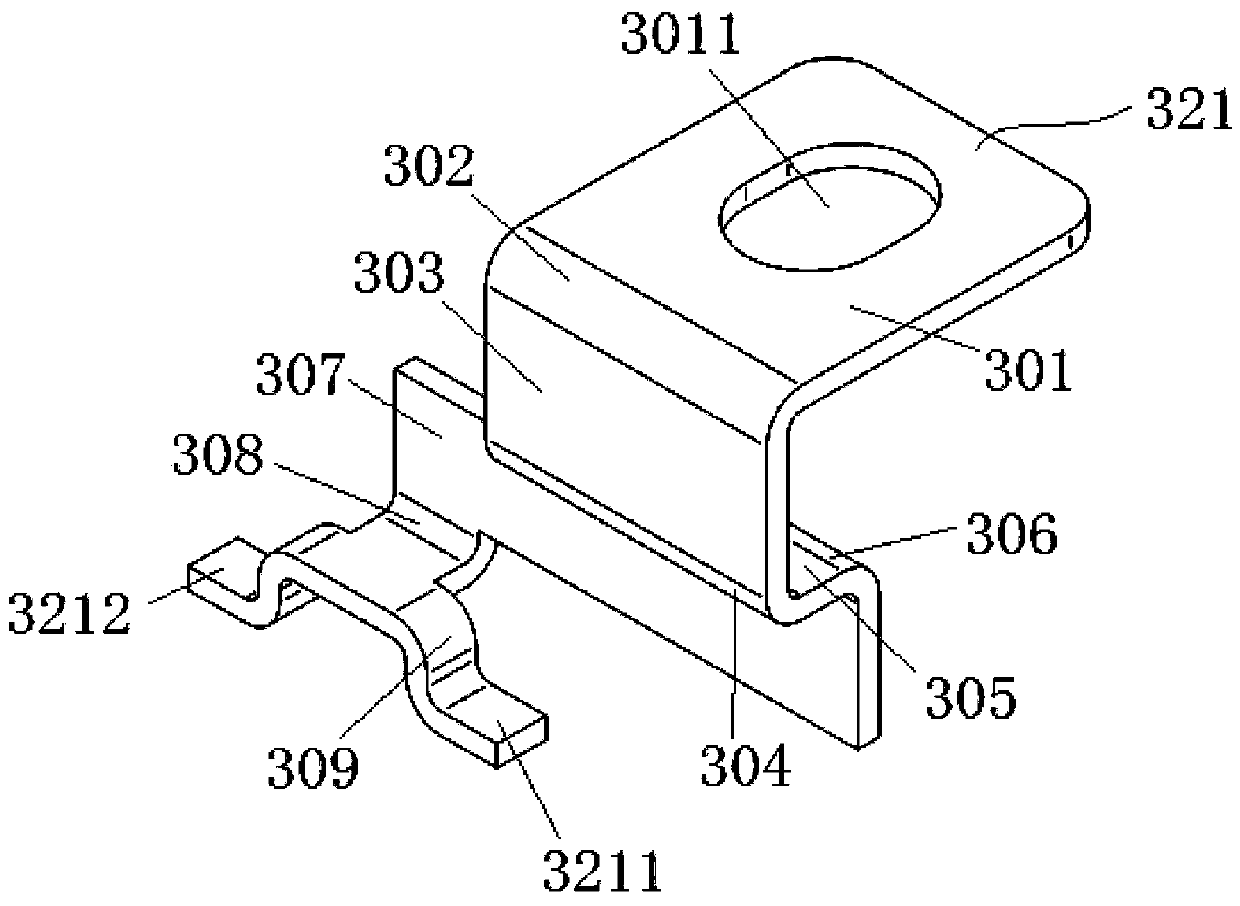

[0031] Such as figure 1 As shown, the power semiconductor module package structure proposed by the present invention includes a substrate 1; a housing 2, the housing 2 and the substrate 1 are sealed and tightly connected; a power semiconductor module subunit 3, which is arranged on the housing 2 and the substrate 1. The containing space is used to form a topology control circuit structu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More