A performance improvement method for stacking dram cache

A caching and performance technology, applied in the performance improvement field of stacked DRAM cache, can solve problems such as high latency, high energy consumption, and cache misses, and achieve the effects of reducing line misses, improving performance, and improving data hit rate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] The present invention will be further described in detail below in conjunction with the accompanying drawings and examples. The following examples are explanations of the present invention and the present invention is not limited to the following examples.

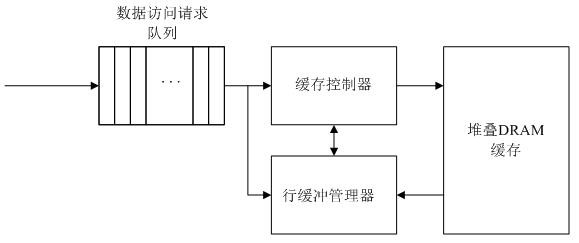

[0031] The method for improving the performance of the stacked DRAM cache in this embodiment includes the following steps:

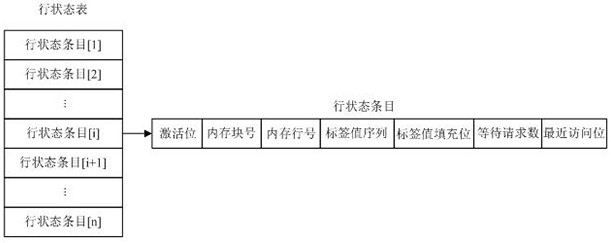

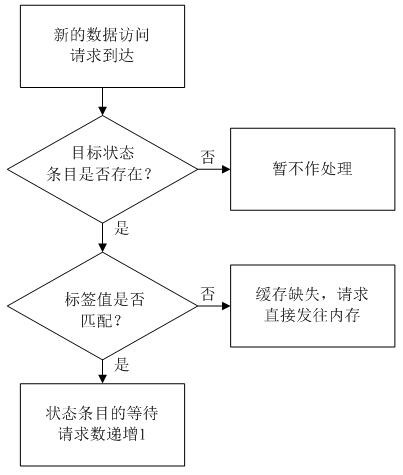

[0032] S1. Propose a row buffer manager, which includes a row status table, and the row status table includes a plurality of row status entries, and each row status entry includes an activation bit, a memory block number, a memory row number, a tag value sequence, a tag value filling bit, The number of waiting requests and the last access bit are used to describe the state of a memory row data.

[0033] The active bit identifies whether the memory line is loaded into the line buffer: if the active bit value is 1, it means that the memory line is currently loaded into the line buffer; if the ac...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More