Random multiphase clock generation circuit

A technology for generating circuits and multi-phase clocks, which is applied in the direction of applying random technology conversion, electrical components, physical parameter compensation/prevention, etc. It can solve the problems of sampling time mismatch, dynamic performance degradation of analog-to-digital converters, etc., and improve dynamic performance Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0022] Below in conjunction with accompanying drawing, further illustrate the present invention through embodiment.

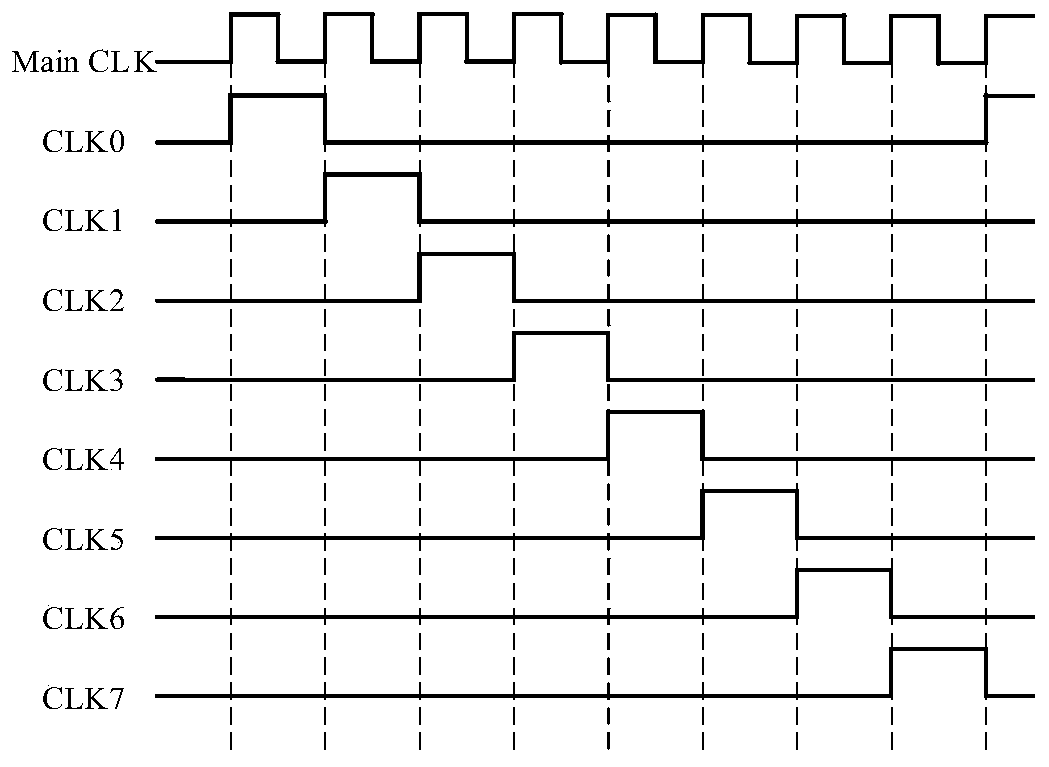

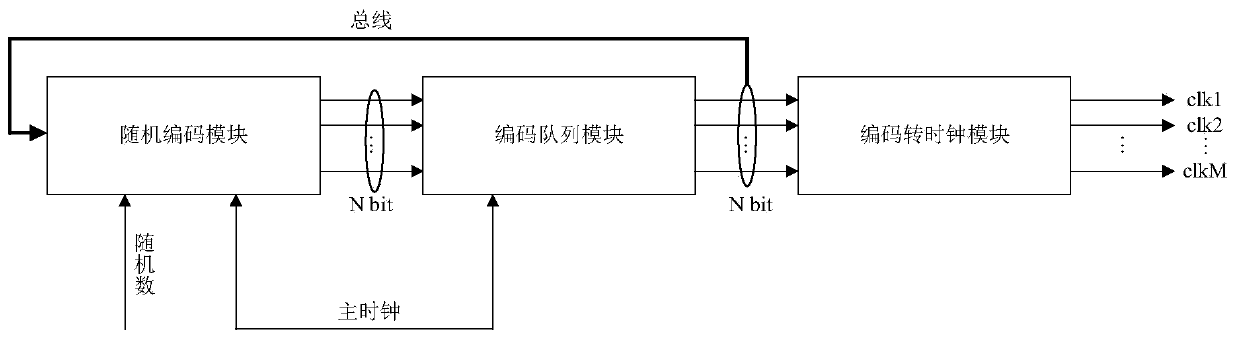

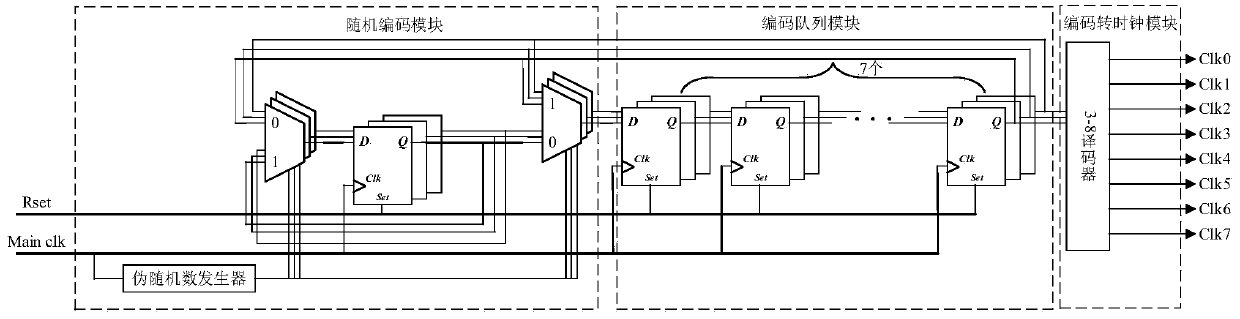

[0023] The present invention proposes a random multi-phase clock generation circuit, which can randomly output M sub-clock signals, and M is a positive integer greater than 1; therefore, the present invention can be applied to TI-ADC and used to control M channels of TI-ADC respectively However, it is obvious that the present invention can be applied not only to TI-ADC, but also to other systems that require random multi-phase clocks. In the following, the application of the present invention to control the random working sequence of M channels in TI-ADC will be described as an example.

[0024] The total number of registers in the random encoding module and the encoding queue module is equal to the number of sub-ADCs in the TI-ADC (ie, the number of channels of the TI-ADC), so the random encoding module includes a first register, and the encoding queue module ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More