Pipelined analog-to-digital converter (ADC) capable of carrying out background digital calibration

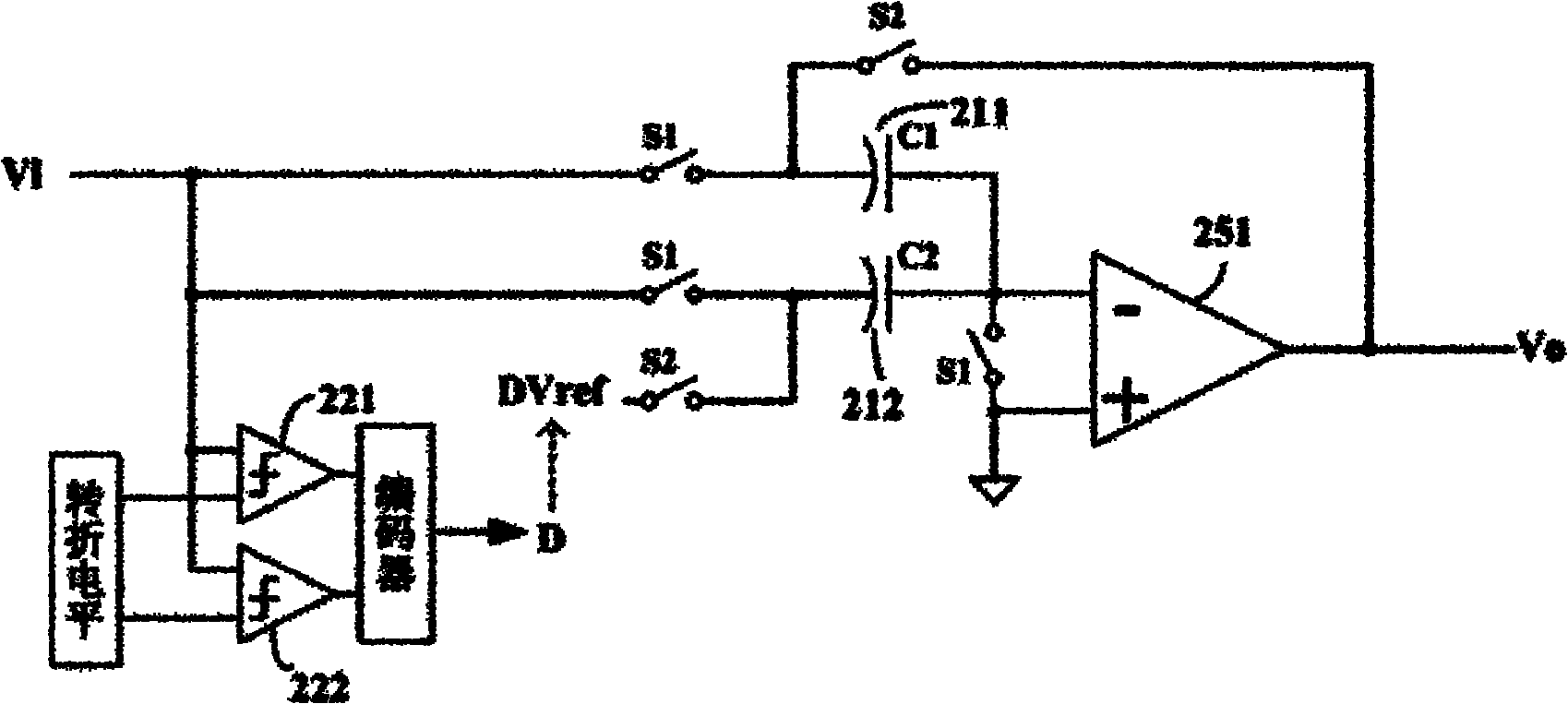

An analog-to-digital converter, pipelined technology, applied in the direction of analog/digital conversion calibration/testing, etc., can solve problems such as the operational amplifier 251 is not ideal, the performance of the analog-to-digital converter is deteriorated, and the gain error of the operational amplifier is easy to achieve , improve linearity, and improve the effect of dynamic performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0038] The present invention will be further described below in conjunction with the accompanying drawings.

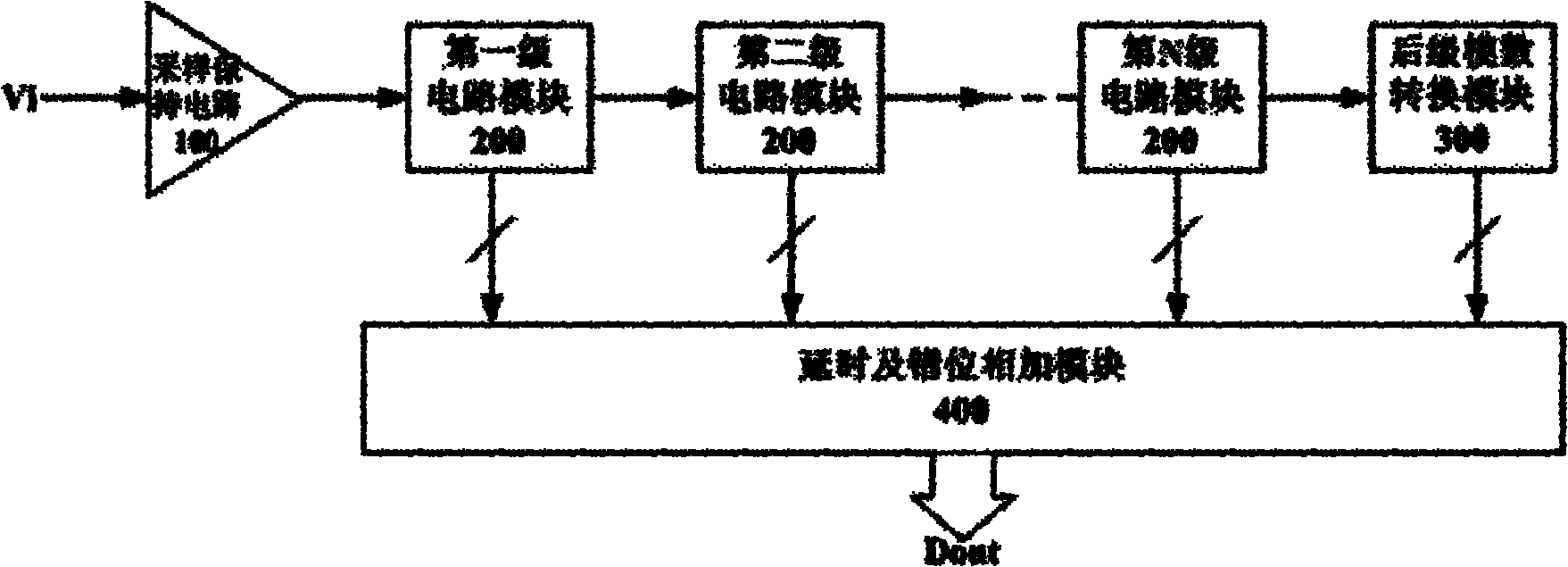

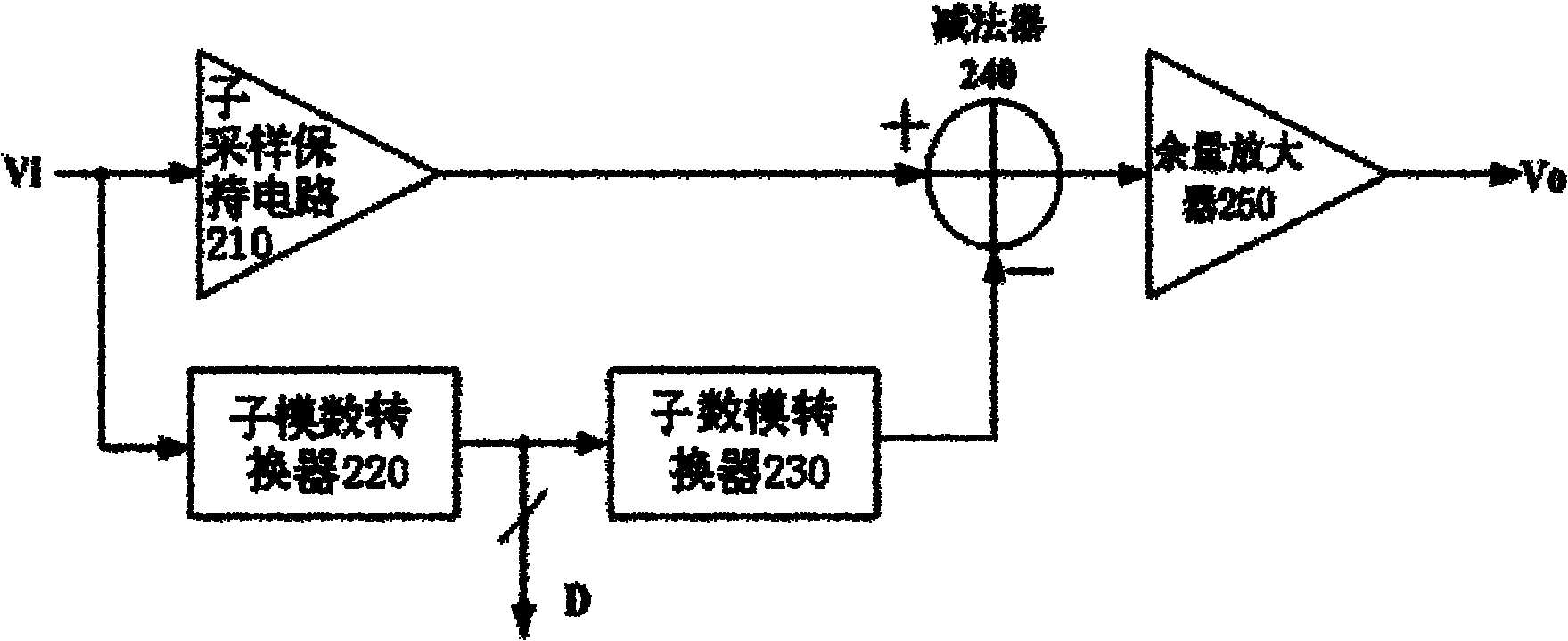

[0039] Such as Figure 5 Shown is a schematic structural diagram of a pipelined ADC that can perform background digital calibration, including a sample-and-hold circuit 100 connected in series, M calibratable stage circuit modules 500, N stage circuit modules 200, and a subsequent analog-to-digital conversion module 300 , where each calibratable level circuit module 500 is connected to a corresponding digital calibration level circuit 600, the quantized value output ports of the level circuit module 200 and the subsequent analog-to-digital conversion module 300 are in phase with the delay and offset addition module 400 Connection, the output end of the delay and offset addition module 400 is reversely connected in series with the digital calibration level circuit 600, and M and N are natural numbers.

[0040] The input analog signal is sampled by the sample-and-hold c...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More