High-low temperature incubator for batch test of semiconductor chips

A batch testing, semiconductor technology, applied in electronic circuit testing, auxiliary non-electrical temperature control, measurement of electricity and other directions, can solve the problems of different air temperature, parallel, can not meet the cooling requirements of semiconductor chips, etc., to ensure temperature uniformity, The effect of stabilizing the ambient temperature

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

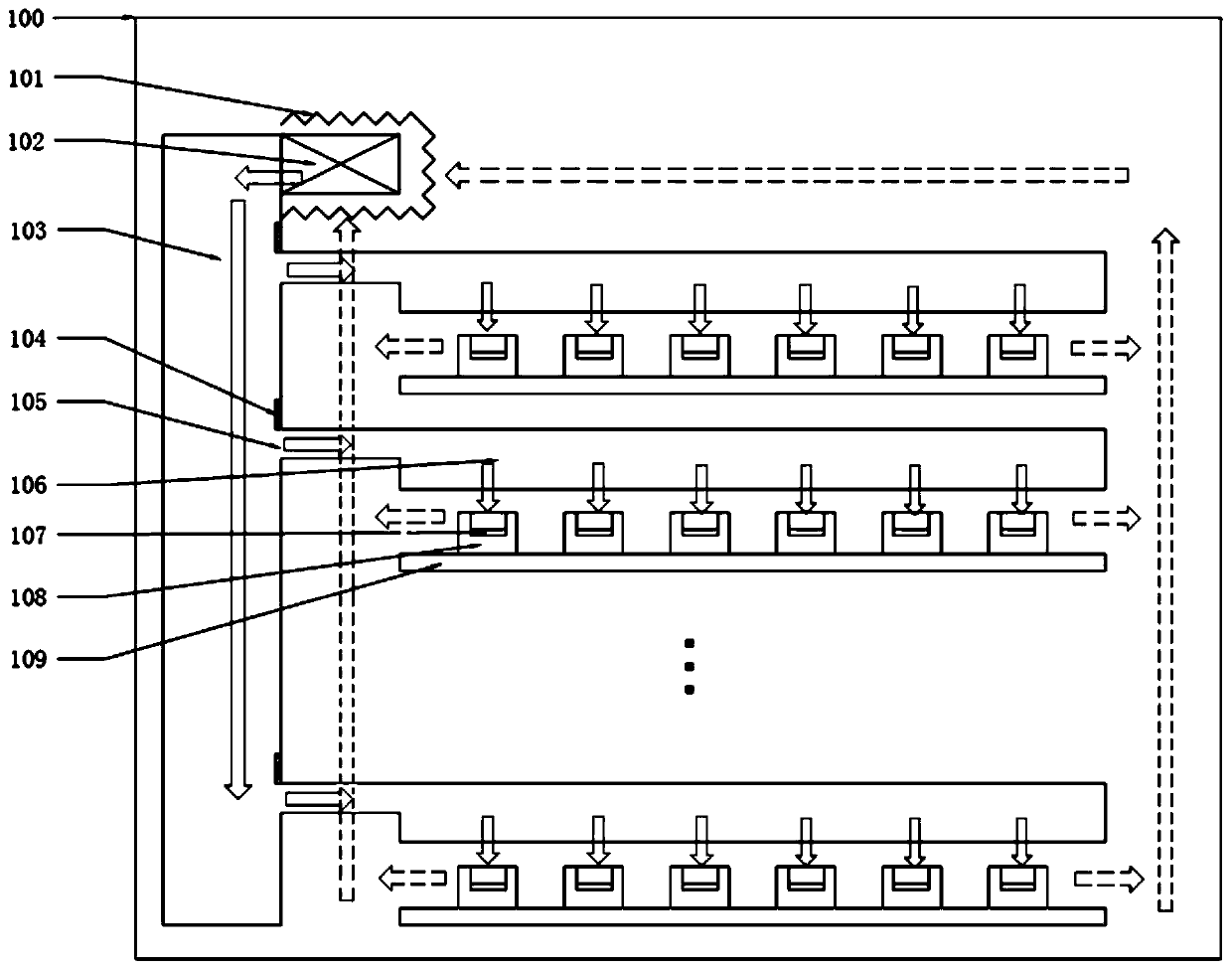

[0025] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments.

[0026] The invention provides a high and low temperature incubator, which provides stable temperature and good heat dissipation conditions for each semiconductor chip when the multi-slot semiconductor chip test board is tested at the same time, through reasonable air duct design and air temperature / pressure monitoring sensors To realize the stability and control of the ambient temperature of all the semiconductor chips to be tested in the high and low temperature incubator within a certain range.

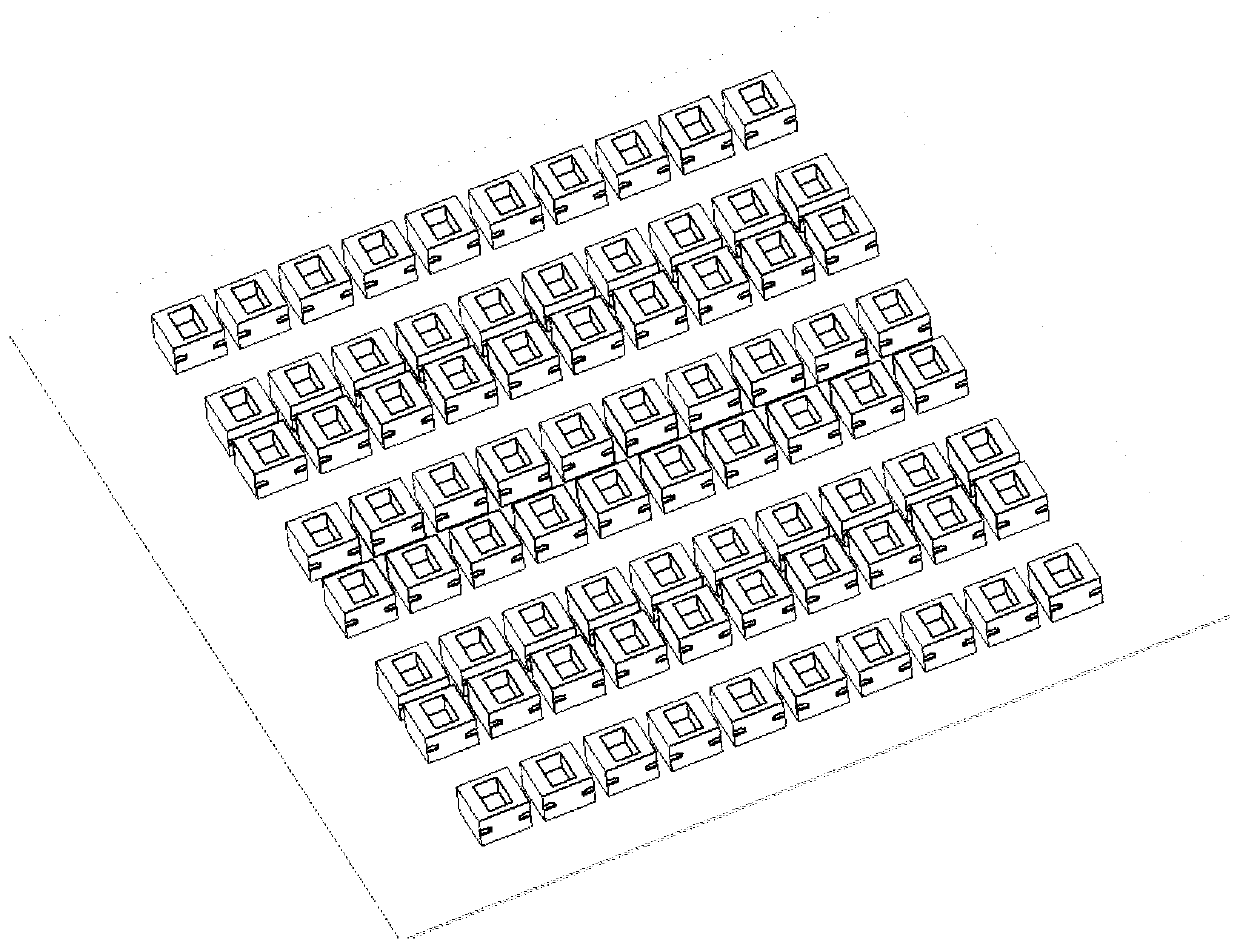

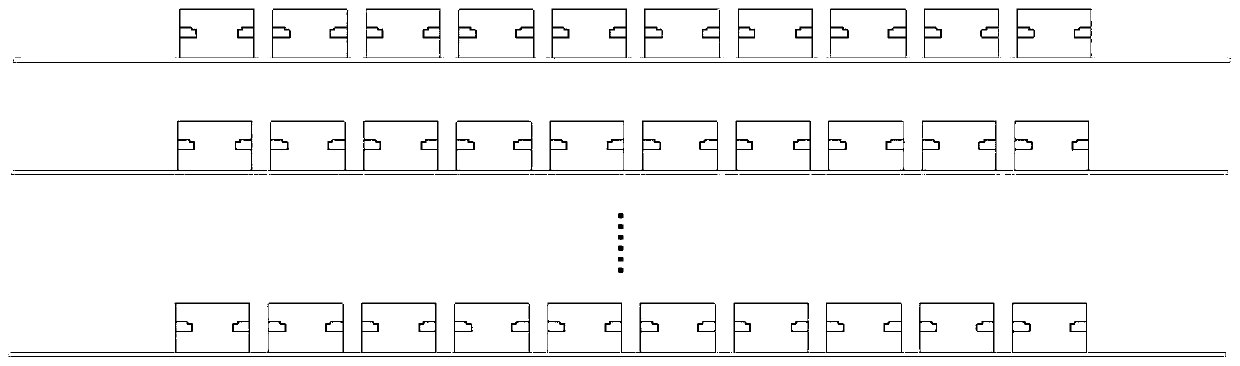

[0027] see image 3 , which is a high and low temperature incubator for batch testing of semiconductor chips in a preferred embodiment of the present invention. In the incubator wall 100, a gas power device (centrifugal fan) 102 is provided with a heat e...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More