A kind of preparation method of high-performance memristor

A memristor and high-performance technology, which is applied in the field of non-volatile memory storage devices, can solve the constraints of memristor storage capacity, low resistance, high resistance state contrast memristor response speed, large surface roughness of three-dimensional images, Problems such as poor pattern uniformity, achieve the effects of obvious and controlled on and off states, good pattern uniformity, and low cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

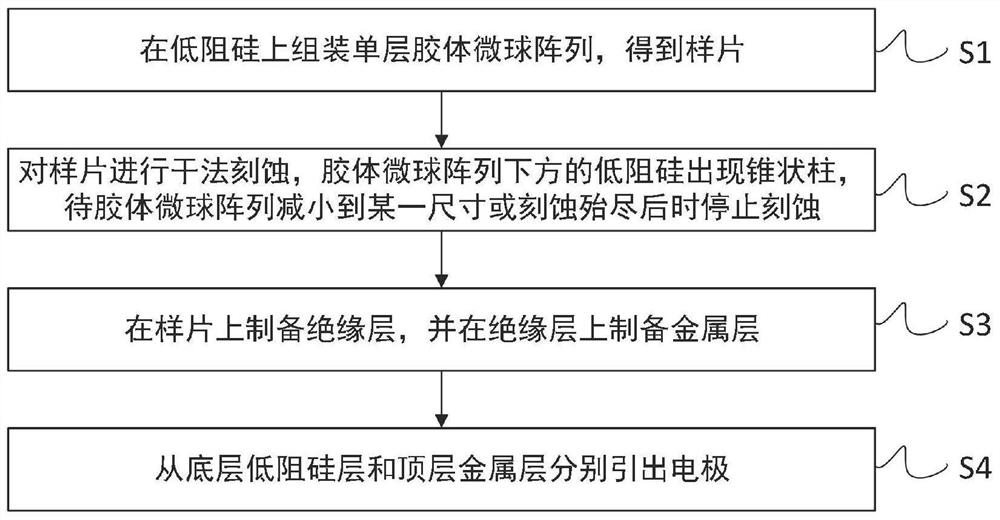

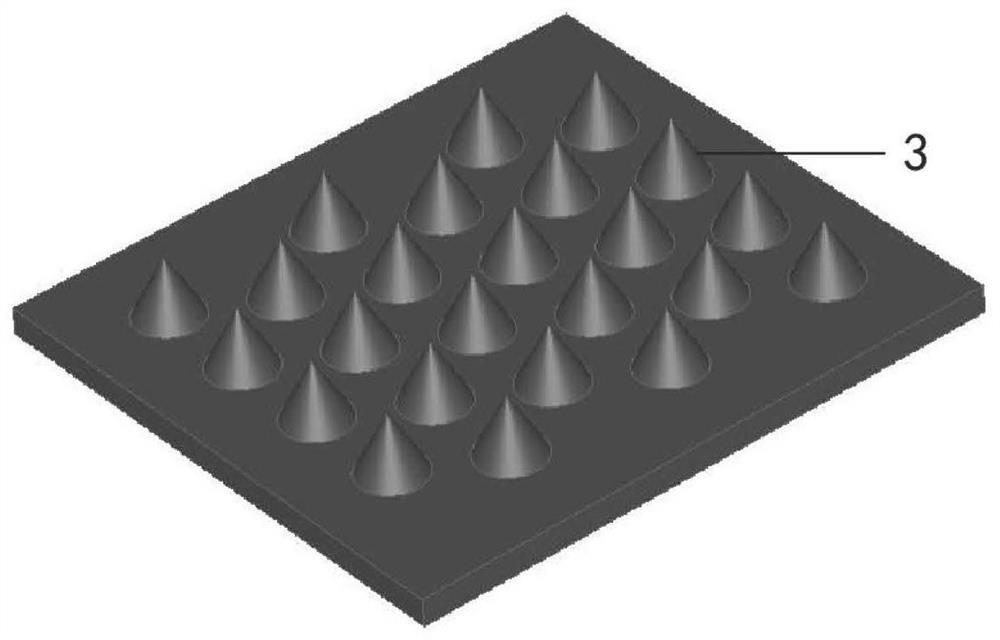

[0042] See figure 1 , figure 1 A method of preparing a high performance memristor disclosed in the present application, including the following steps:

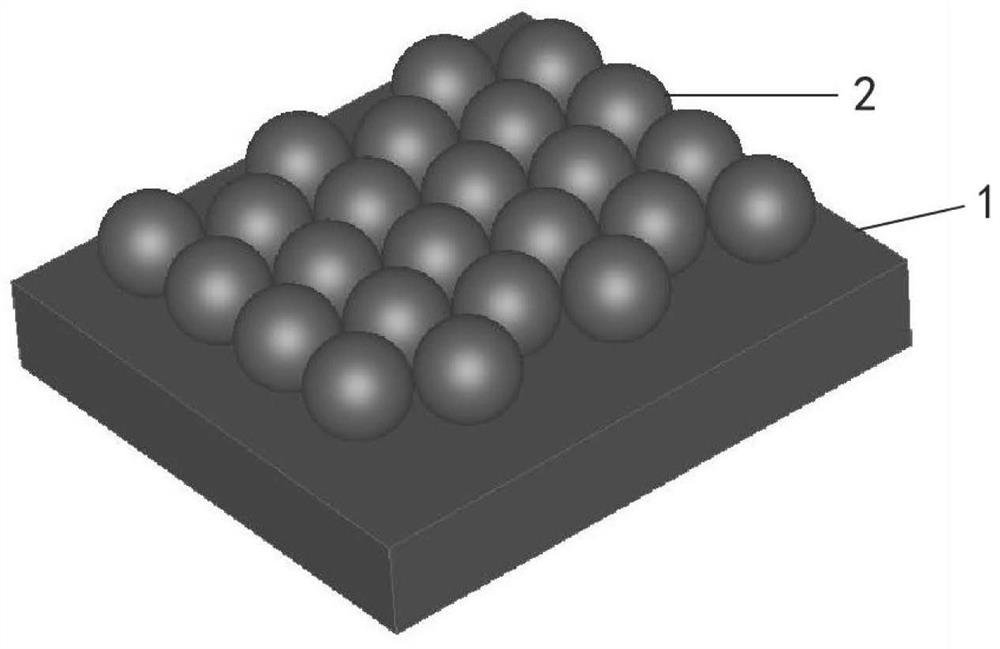

[0043] S1: figure 2 As shown, a single layer colloidal microsphere array 2 is assembled on the low resistant silicon 1 to obtain a sample.

[0044] Among them, the low-resistant silicon is clean, dried, and polished low-resistant silicon.

[0045]More preferably, in an exemplary embodiment, a low-resistant silicon crystal is 100, 110 or 111, a conductivity approaches or less than 0.01 Ω · cm.

[0046] In yet another exemplary embodiment, the components of the colloidal microsphere include a polymer, a dielectric, a semiconductor, a metal, a colloidal microsphere size of 30 nm to 100 μm.

[0047] In yet another exemplary embodiment, the monolayer colloidal microsphere array in low-resistant silicon is used in low-resistant silicon, which includes spin coating, gas-liquid interface self-assembly, dropping-self-assembly, vertical Li ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| size | aaaaa | aaaaa |

| size | aaaaa | aaaaa |

| size | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More