Double-base-island heat dissipation chip packaging process

A technology of chip packaging and process, which is applied in the field of double-base island heat dissipation chip packaging process, can solve the problems of stamping deformation of lead frame blank, package deformation of lead frame blank, heat deformation of lead frame blank, etc., and achieve the effect of avoiding stamping deformation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] The present invention will be further described below in conjunction with the accompanying drawings.

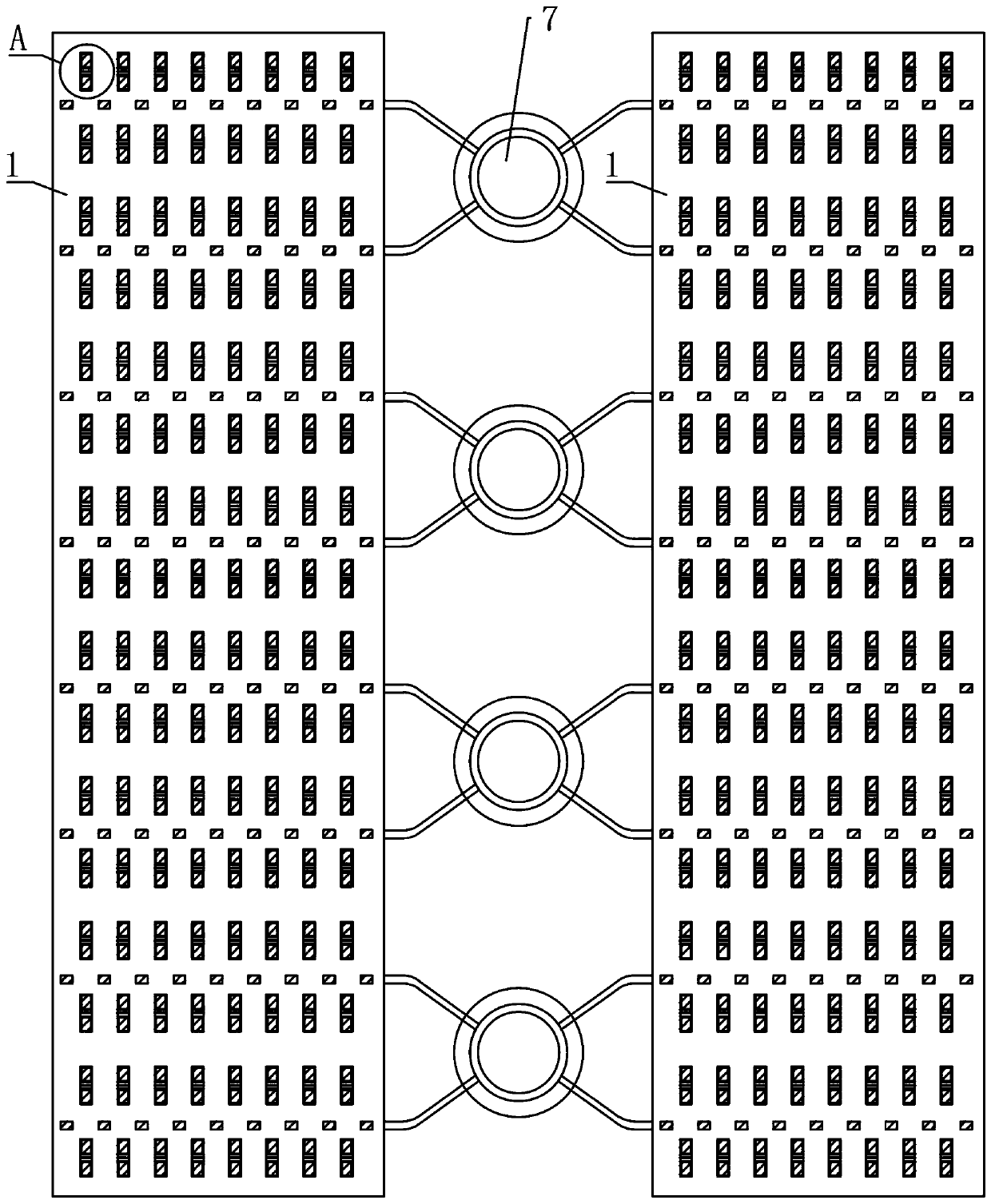

[0025] Such as Figure 1-7 As shown, a double base island cooling chip packaging process,

[0026] Step 1. Forming several base islands on the lead frame blank 1,

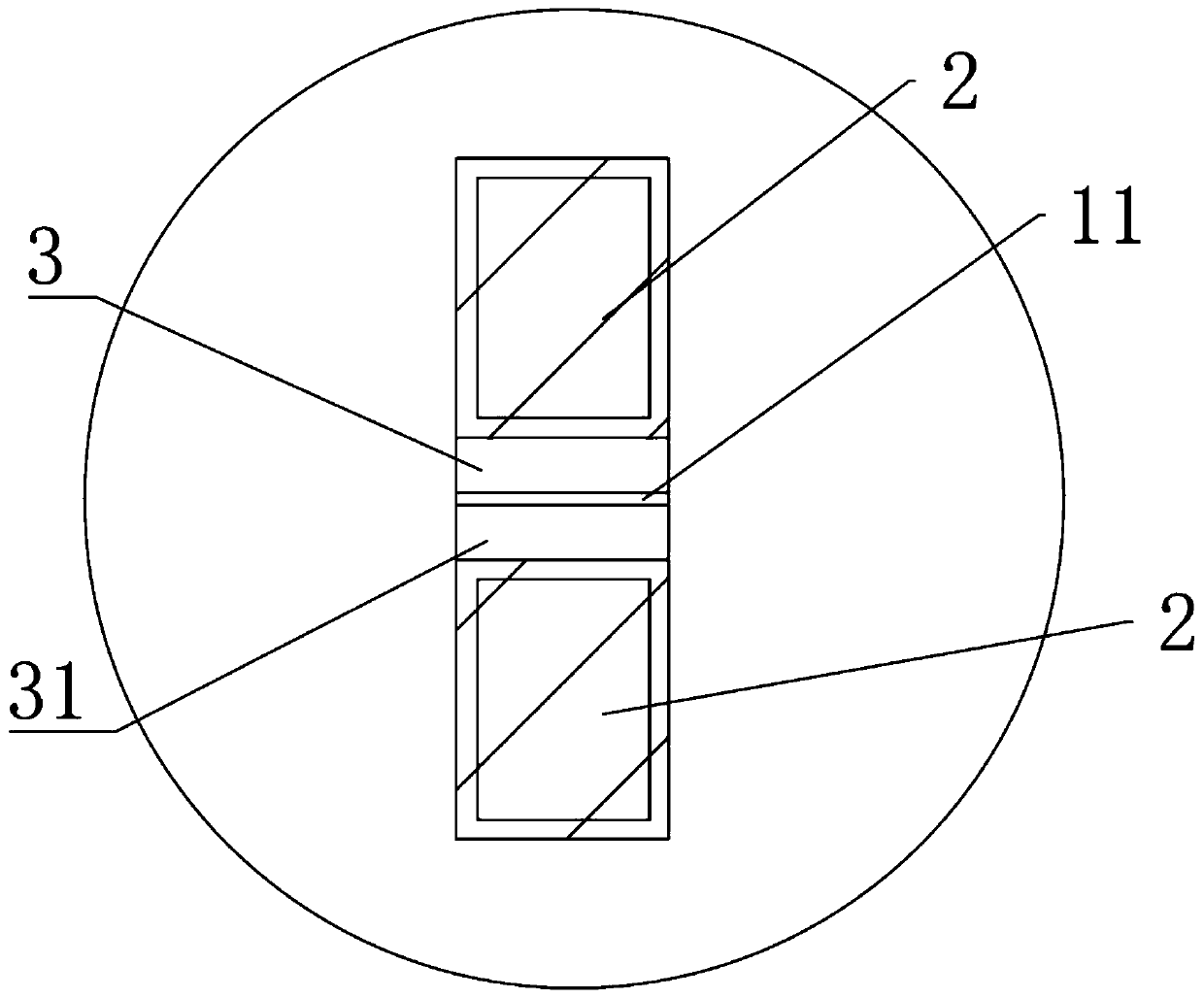

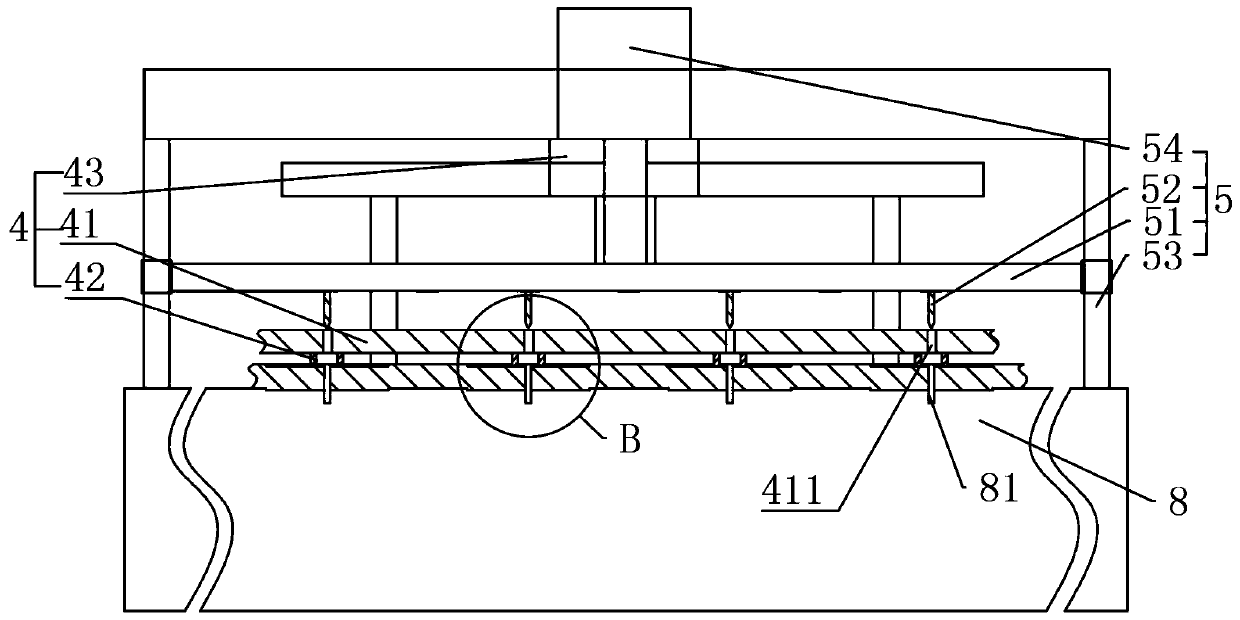

[0027] Step 2. Place the lead frame blank 1 on the stamping die base 8 of the stamping device, first press the lead frame blank 1 through the first pressing assembly 4, and the lead frame blank 1 is formed by stamping the middle part of the base island through the stamping assembly 5 The heat dissipation groove 11, the heat dissipation groove 11 runs through the upper and lower end surfaces of the lead frame blank 1, and separates the base island into a first base island 3 and a second base island 31;

[0028] Step 3. Correspondingly installing the chip 2 in the first base island 3 and the second base island 31;

[0029] Step 4. Compress the surroundings of the heat sink 11 through the second pressing co...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More