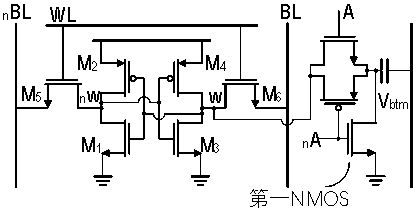

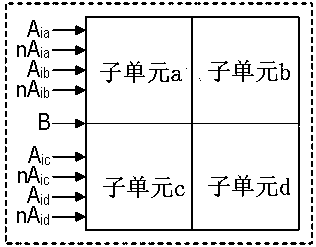

Subunit, MAC array and bit width reconfigurable analog-digital hybrid in-memory calculation module

A hybrid computing and sub-unit technology, applied in the direction of analog/digital conversion, digital memory information, electrical components, etc., can solve the problems of the MAC array occupying a large area, limited application scenarios, reducing the analog-to-digital conversion speed, etc., to solve the input imbalance. Effect of Voltage Offset

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0051] In order to make the object, principle, technical solution and advantages of the invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that, as described in the summary of the present invention, the specific embodiments described here are used to explain the present invention, not to limit the present invention.

[0052] It should be noted that the connection or positional relationship that can be determined according to the text or technical content of the manual is partially omitted or not all position change diagrams are drawn for the sake of simplicity of the drawing. It cannot be considered that there is no explanation for the position change diagram shown in the figure. For the sake of brevity, it will not be explained one by one in the specific explanation, and it will be explained in a unified manner here.

[0053] As a common application scenario,...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com