Extensible multi-port DDR3 controller based on FPGA

A controller and multi-port technology, which is applied in the field of communication, can solve problems such as the inability to meet the multi-port application requirements of simultaneously processing multiple high-speed complex data stream buffers, and achieve high use efficiency, memory space saving, and convenient read and write operations Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

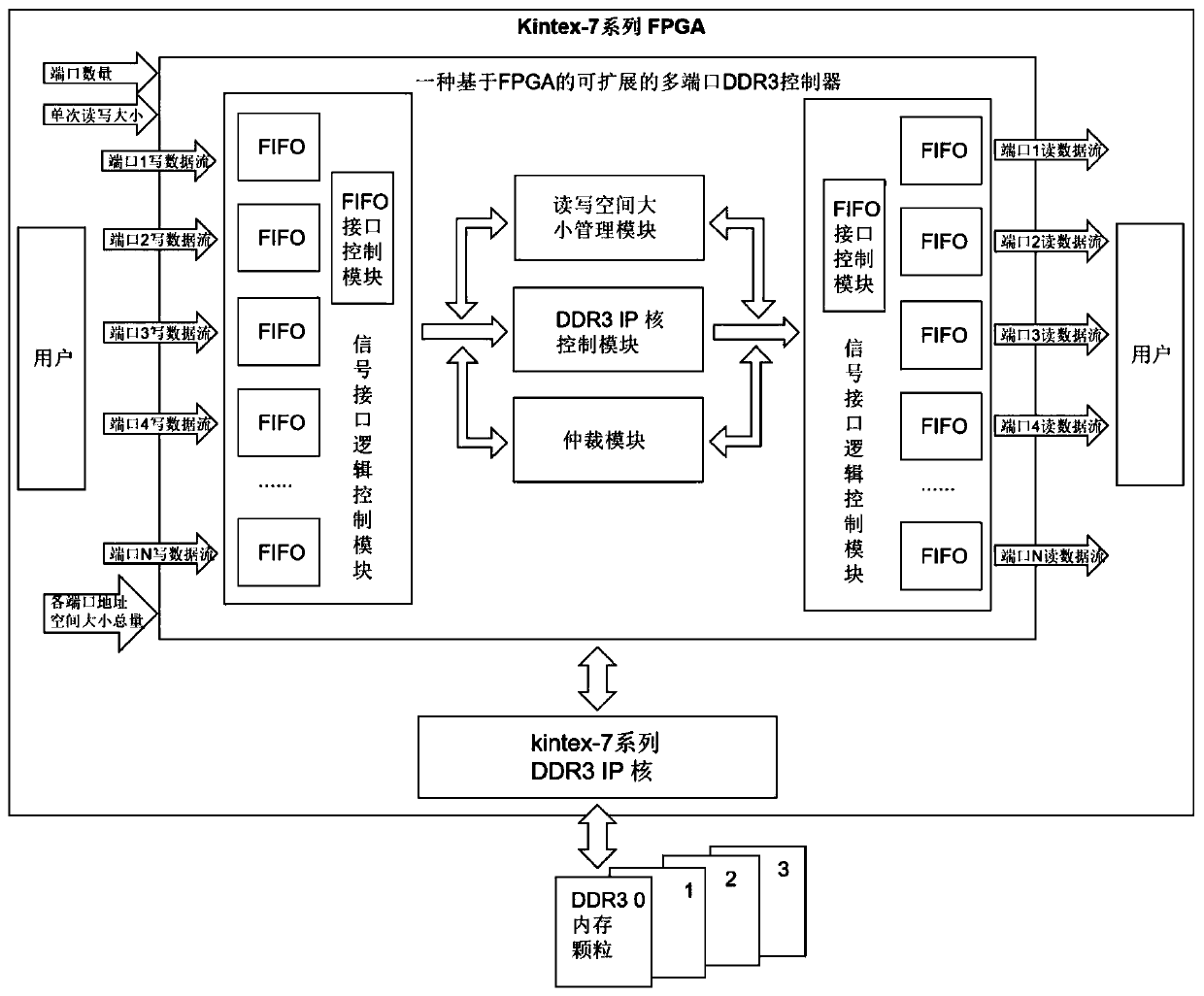

[0036] A scalable multi-port DDR3 controller based on FPGA, including an arbitration module, a read-write space size management module, a DDR3 IP core control module and a FIFO interface control module, an arbitration module, a read-write space size management module, and a DDR3IP core control module and the FIFO interface control module are electrically connected in sequence;

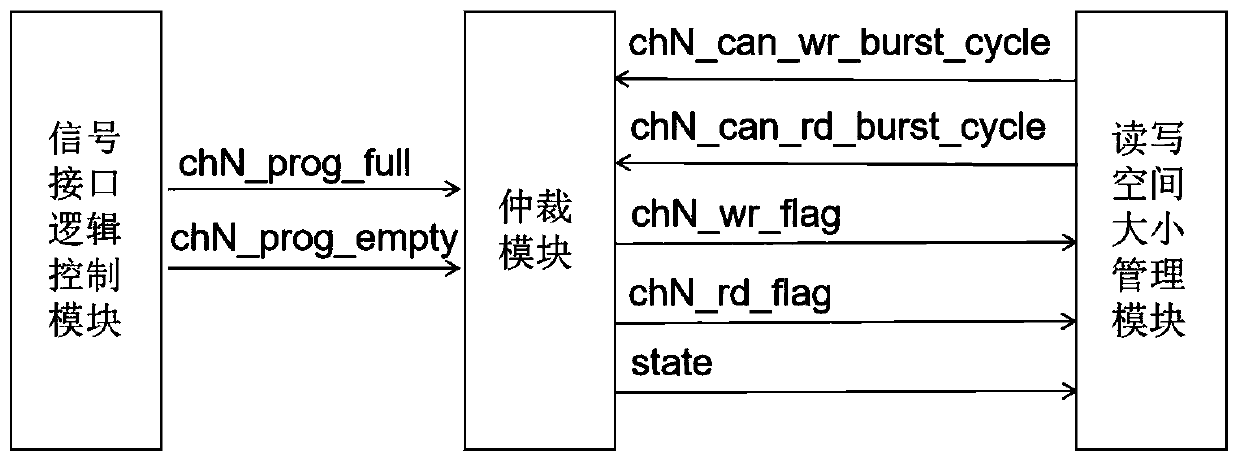

[0037] The arbitration module is used to comprehensively arbitrate and manage the read and write requests of each port according to the remaining available address space for reading and writing provided by the read and write space size management module, the FIFO capacity threshold corresponding to each port, and the priority information of each port according to actual needs ;

[0038] The read and write space size management module is used to manage the read and write process of each port. According to the single read and write size configured globally and the total address space size of each port, t...

Embodiment 2

[0082] The difference technology compared with embodiment one is as follows:

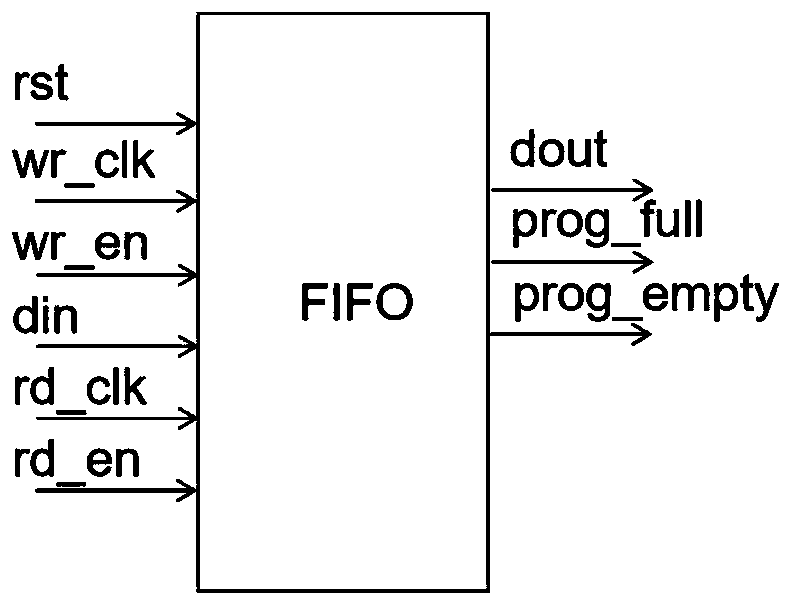

[0083] Replace the read-write space size management module with the signal interface logic control module, which is used to configure the number of ports according to the port expansion requirements, and the DDR3 IP core control module and FIFO interface control module are also used to send and receive signal interface logic control module data. Configure the number of ports and the size of a single read and write. The number of ports determines the number of instantiated read and write FIFOs in the signal interface logic control module. FIFOs solve the problems of data caching and data transmission across clock domains.

[0084] The number of ports in this technical solution is configurable: the user can configure the number of data flow channels according to actual usage requirements, and the read-write interface adopts the standard FIFO interface form, which makes the read-write operation more co...

Embodiment 3

[0086] The difference technology compared with embodiment one is as follows:

[0087]On the basis of Embodiment 1, a signal interface logic control module is added, the signal interface logic control module is used to configure the number of ports according to the port expansion requirements, and the DDR3 IP core control module and FIFO interface control module are also used for sending and receiving signal interface logic control module data. Configure the number of ports and the size of a single read and write. The number of ports determines the number of instantiated read and write FIFOs in the signal interface logic control module. FIFOs solve the problems of data caching and data transmission across clock domains.

[0088] This technical solution provides a DDR3 controller interface whose number of ports can be arbitrarily expanded according to requirements, with standard FIFO read-write interface form, configurable port number, configurable single read-write size, and co...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More