Hardware architecture for accelerating Deep Q-Network algorithm and design space exploration method of hardware architecture

A hardware architecture and algorithm technology, applied in the field of artificial intelligence, can solve problems such as optimization of FPGA hardware computing architecture, high computational complexity, and large consumption of storage resources.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

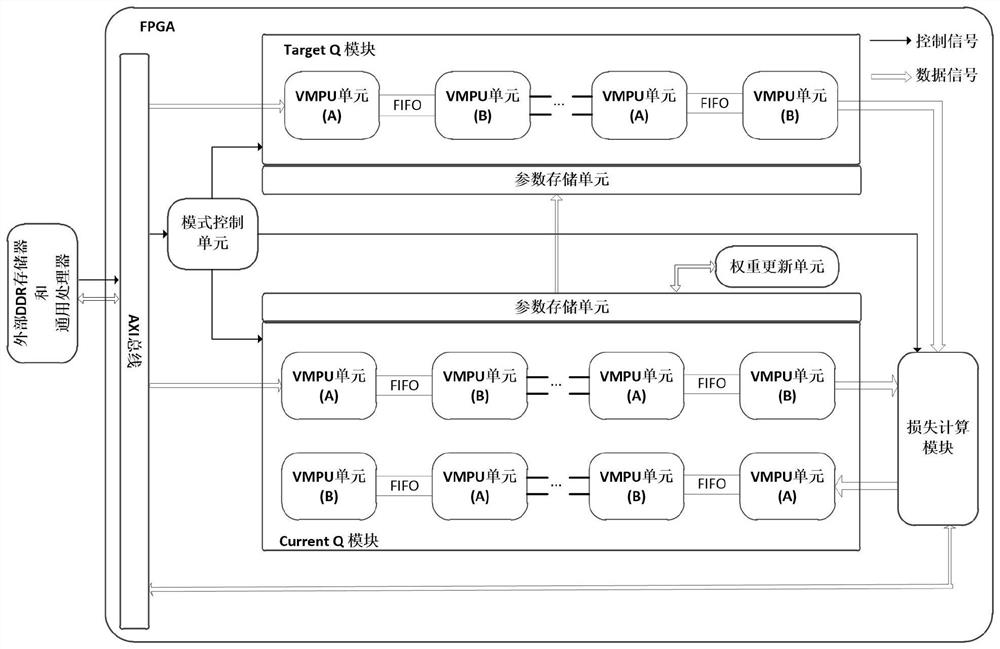

[0036] A kind of hardware framework for accelerating Deep Q-Network algorithm, described hardware framework comprises general processor module and FPGA programmable logic module and external DDR memory, and described FPGA programmable logic module comprises AXI bus interface, Target Q module, Current Q module, Loss calculation module, mode control module, parameter storage unit and weight update unit;

[0037] The general processor module is responsible for interacting with the external environment and realizing the calculation of the reward function, and is also responsible for the maintenance of the DeepQ-Network algorithm experience pool;

[0038] The external DDR memory is mainly responsible for the storage of the Deep Q-Network algorithm experience pool.

[0039] The AXI bus interface is a general AXI bus interface structure, which is responsible for realizing the transmission and feedback of control signals and data signals between the general processor and the FPGA prog...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com