Bare chip KGD screening method based on adapter substrate

A screening method and bare chip technology, applied in the direction of electrical components, circuits, semiconductor/solid-state device testing/measurement, etc., can solve the unsuitable bare chip size, different PAD coordinates, small batch testing requirements, expensive fixtures, etc. problem, to achieve the effect of reducing test cost, reducing test cost, and reducing processing cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] The present invention will be further described in detail below in conjunction with specific embodiments, which are explanations of the present invention rather than limitations.

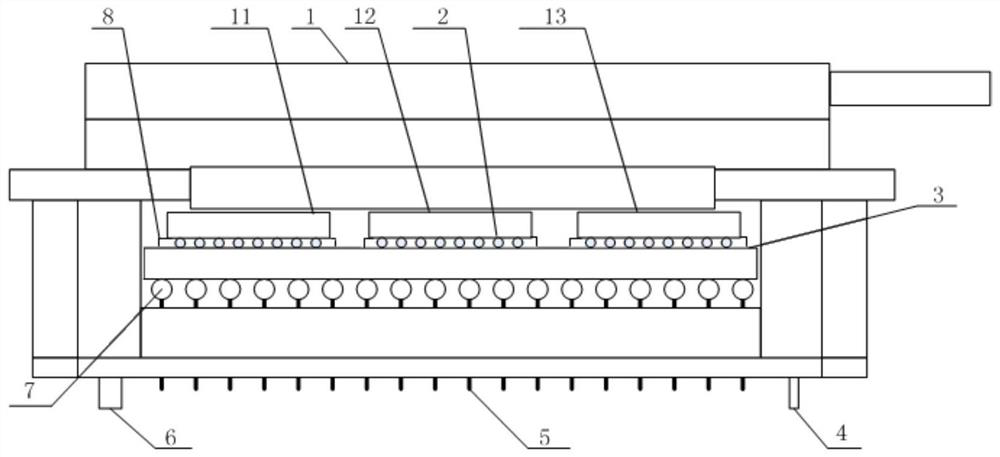

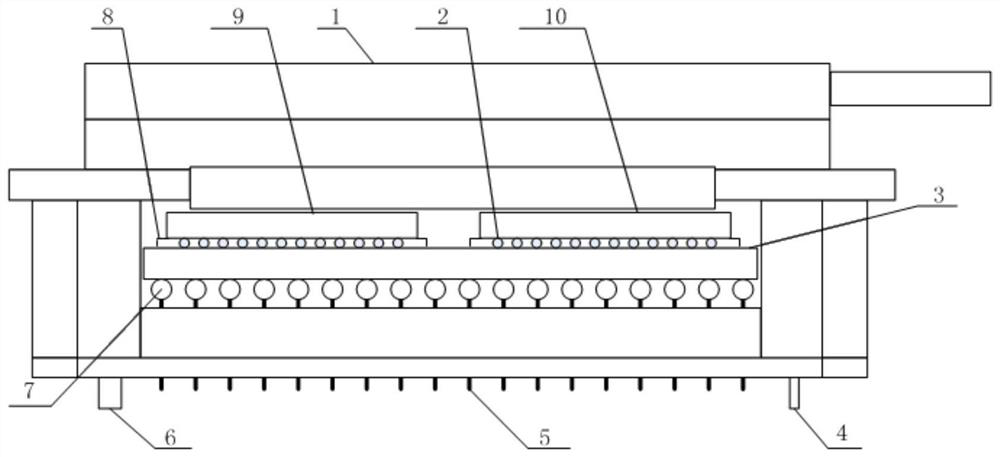

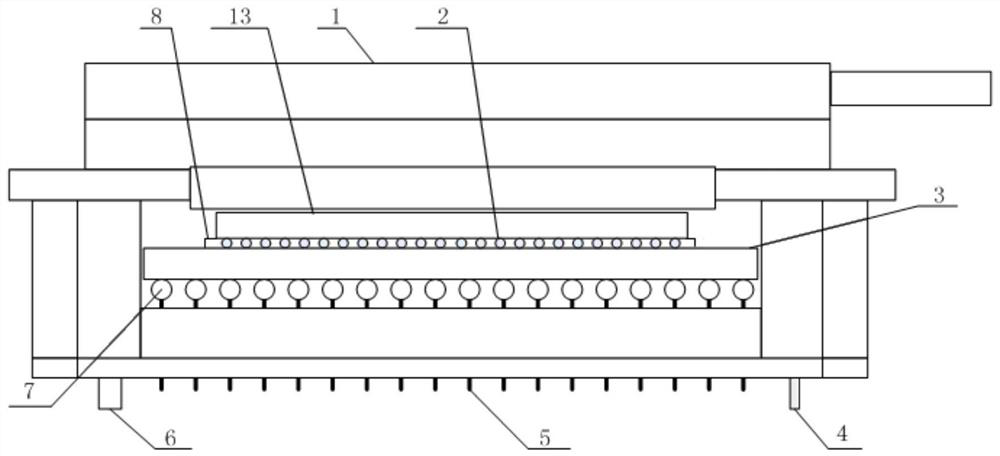

[0029] A kind of bare chip KGD screening method based on the transfer substrate of the present invention, such as Figure 4 and Figure 5 As shown, the specific steps are as follows:

[0030] Step 1, determine the bare chip standard component size,

[0031] Bare chip standard components can also be called silicon components, including silicon transfer substrates and bare chips. According to the size of silicon transfer standard substrates and bare chips, the number of bare chips of this size placed on silicon transfer substrates is determined to form each standard Bare chip components;

[0032] An example is as follows,

[0033] The area of the silicon transfer substrate is 30mm×30mm, the diameter of the PAD at the bottom of the silicon transfer substrate is 200μm, and the spacing betwe...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com