Semiconductor structure and forming method thereof

A technology of semiconductor and stacked structure, which is applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, electric solid-state devices, etc. It can solve the problems that the performance of 3D packaging structure needs to be improved, and achieve the effect of improving cutting accuracy and preventing damage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0017] It can be seen from the background art that the performance of the existing 3D packaging structure needs to be improved.

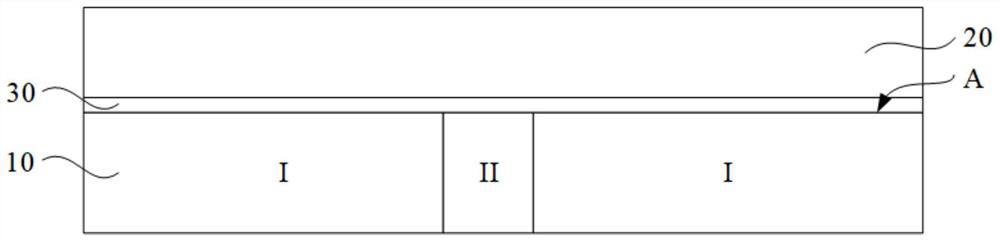

[0018] The analysis found that with the increase in the number of stacked wafers in the 3D packaging structure, the thickness of the wafer stack structure is getting thicker and thicker. It is difficult to effectively cut the wafer stack structure with a single cutting process, and it is easy to cause mis-cutting of the chip.

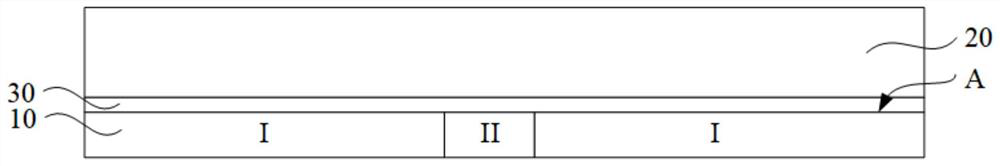

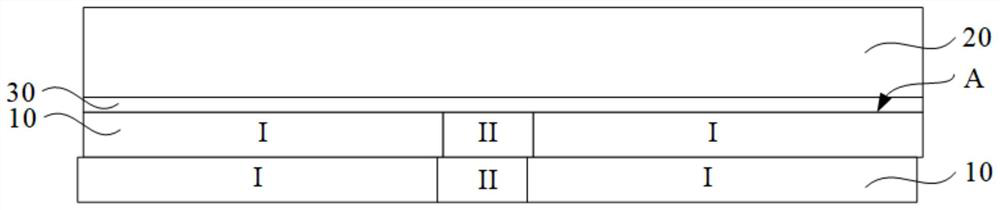

[0019] In order to solve the above problems, an embodiment of the present invention provides a method for forming a semiconductor structure. The wafer stack structure is cut twice to complete the cutting of the wafer stack structure. Different, so as to avoid cutting to the chip by mistake during the cutting process, and prevent the chip from being damaged.

[0020] In order to make the purpose, technical solutions and advantages of the embodiments of the present invention clearer, the embodiments of the present invention wil...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Width | aaaaa | aaaaa |

| Width | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More