Power management integrated circuits and semiconductor memory modules including power management integrated circuits

A power management, integrated circuit technology, applied in static memory, read-only memory, digital memory information, etc., can solve problems such as large burdens

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0022] Hereinafter, embodiments of the inventive concept may be described in detail and clearly to the extent that those of ordinary skill in the art can realize the inventive concept. The same reference numerals denote the same elements throughout.

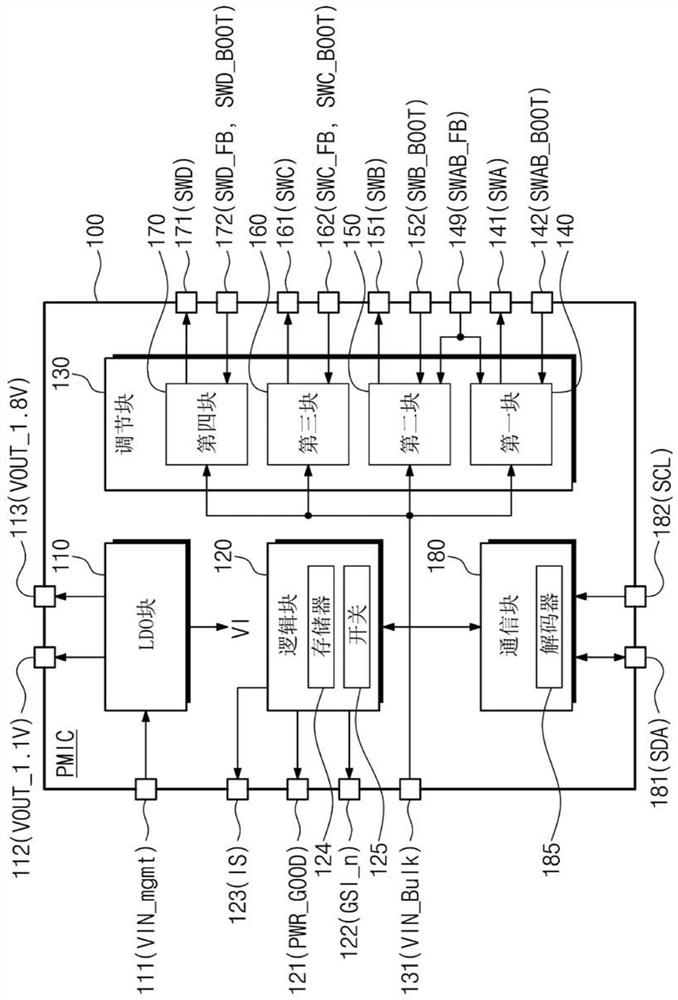

[0023] figure 1 is a block diagram illustrating a power management integrated circuit (PMIC) 100 according to an embodiment of the inventive concept. refer to figure 1 , the power management integrated circuit 100 may include a low drop out (LDO) block 110 , a logic block 120 , a regulation block 130 and a communication block 180 .

[0024] The LDO block 110 may be connected with a first LDO pad (pad, or pad) 111 , a second LDO pad 112 and a third LDO pad 113 which may be attached to an external device. The LDO block 110 may receive a first input voltage VIN_mgmt through a first LDO pad 111 . For example, the target level of the first input voltage VIN_mgmt may be 3.3V and may have an allowable range of 3.0V to 3.6V.

[0025...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap