Processing method for back-to-back design of PCB

A technology of PCB board and processing method, applied in the processing field of PCB board back-to-back design, can solve the problems of inability to guarantee quality, long processing cycle, low production efficiency, etc. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

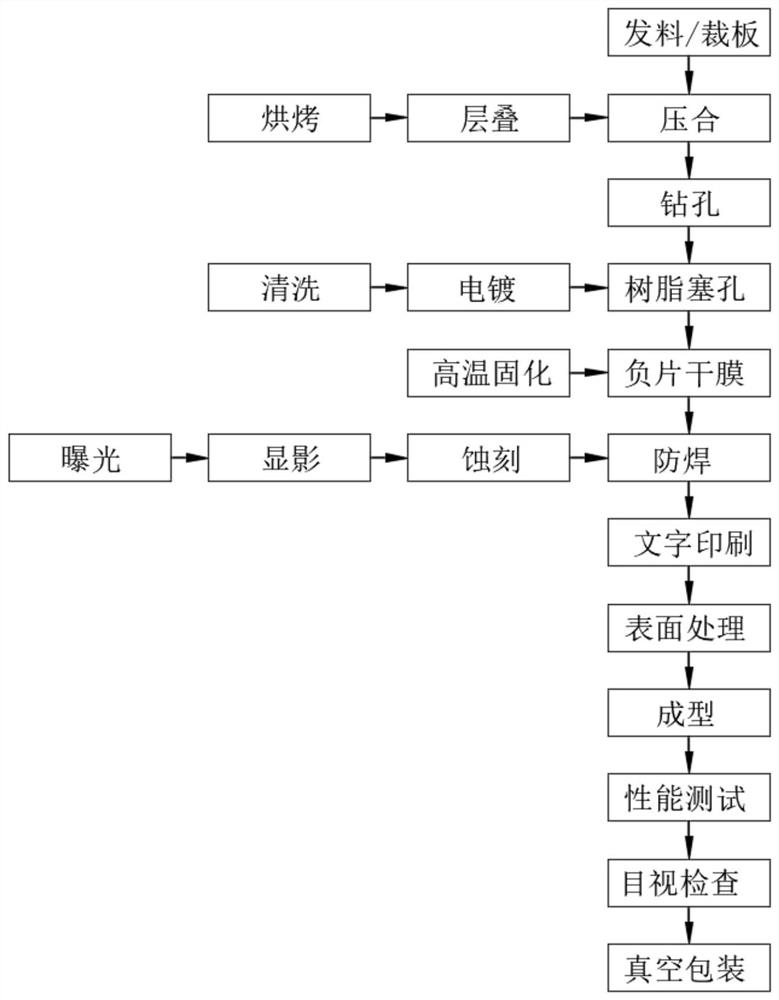

[0025] see figure 1 , in an embodiment of the present invention, a back-to-back design processing method for a PCB includes an upper core board and several layers of middle core boards located at the bottom of the upper core board, the bottom of the middle core board is provided with a lower core board, the The size of the upper core board, the middle core board and the lower core board are all the same.

[0026] In this embodiment, preferably, copper layers are electroplated on the front and back sides of the upper core board, the middle core board and the lower core board.

[0027] In this embodiment, preferably, a semi-cured prepreg material is provided between the upper core board and the middle core board, between each middle core board, and between the middle core board and the lower core board.

[0028] In this embodiment, preferably, its implementation method includes the following steps:

[0029] S1: Select the appropriate material according to the needs, and cut an...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More