Semiconductor structure and forming method thereof

A technology of semiconductor and gate structure, applied in the field of semiconductor structure and its formation, can solve the problem that the surface of the wafer cannot provide enough area for interconnection lines, etc., so as to reduce the probability of bridging and optimize the electrical performance.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0013] It can be seen from the background art that the devices formed so far still have the problem of poor performance. The reasons for the poor performance of the device are analyzed in conjunction with a method of forming a semiconductor structure.

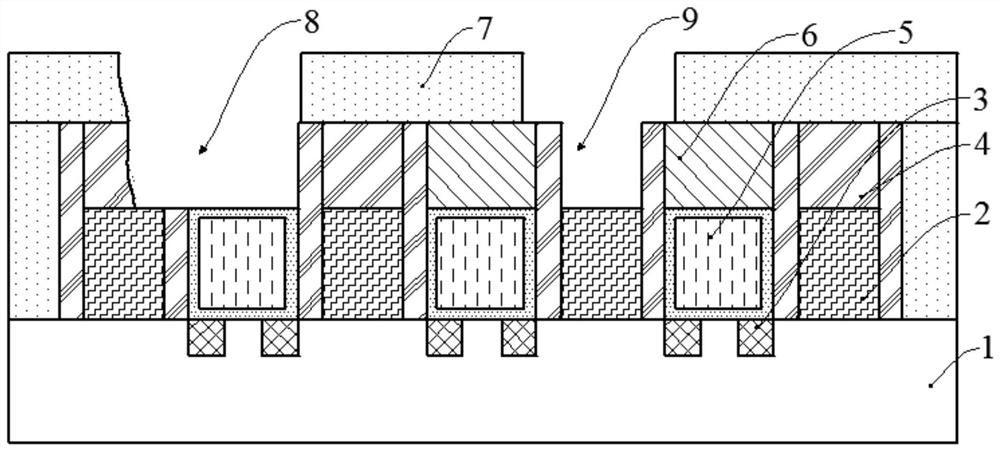

[0014] refer to Figure 1 to Figure 4 A structural schematic diagram corresponding to each step in a method for forming a semiconductor structure is shown.

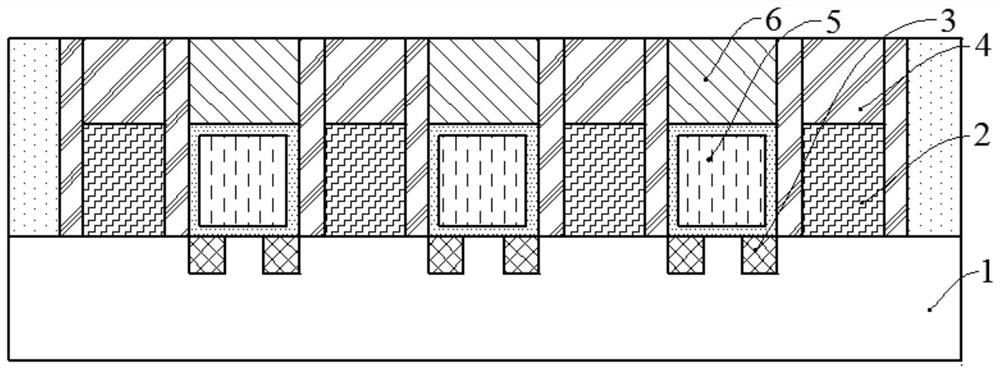

[0015] Such as figure 1 As shown, a substrate is provided, and the substrate includes a substrate 1, a gate structure 2 located on the substrate 1, source and drain doped regions 3 located in the substrate 1 on both sides of the gate structure 2, An insulating cap layer 4 on the gate structure 2, a source-drain connection layer 5 on the substrate 1 between the insulating cap layers 4, and a source-drain dielectric layer on the source-drain connection layer 5 Layer 6.

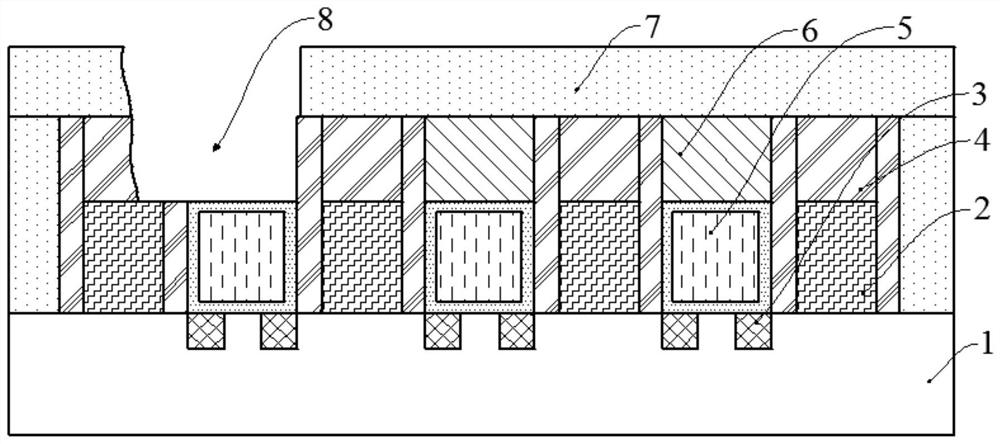

[0016] Such as figure 2 As shown, an interlayer dielectric layer 7 is formed on the insulating capp...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More