An instruction scheduling system and method for a reconfigurable array processor

An array processor and instruction scheduling technology, applied in instruction analysis, concurrent instruction execution, electrical digital data processing, etc., to achieve the effects of improving use efficiency, enhancing versatility, and improving compatibility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0044] In order to make the purpose, technical solutions and advantages of the embodiments of the present invention clearer, the technical solutions in the embodiments of the present invention will be clearly and completely described below in conjunction with the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments It is some embodiments of the present invention, but not all of them. Based on the implementation manners in the present invention, all other implementation manners obtained by persons of ordinary skill in the art without creative efforts fall within the protection scope of the present invention.

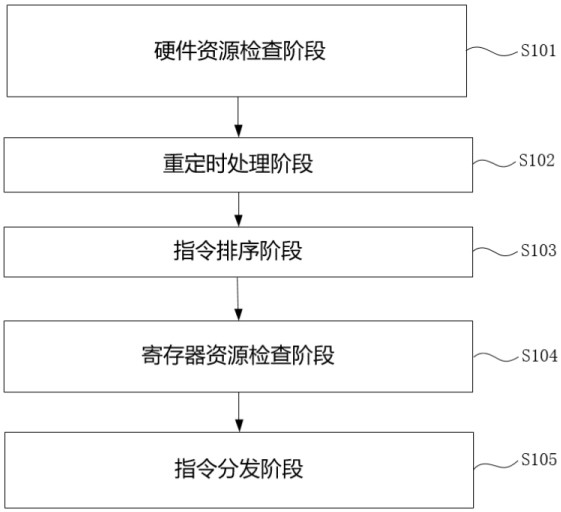

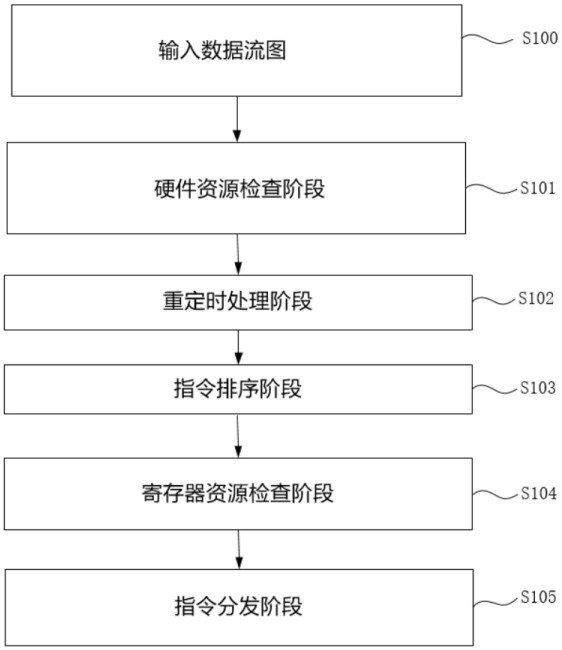

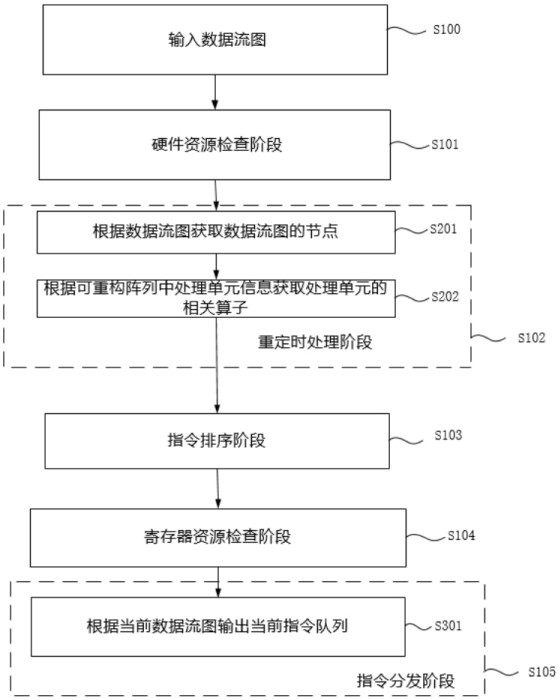

[0045] Such as Figure 1-3 As shown, the present invention provides an instruction scheduling method for a reconfigurable array processor, comprising:

[0046] Step S101, hardware resource checking stage.

[0047] In this step, it is judged whether the fan-out number of the nodes in the data flow graph is smaller than t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More