Memory access interface device

An interface device, memory technology, applied in information storage, static memory, read-only memory, etc., can solve the problem of unable to achieve speed requirements, insufficient use, etc., to achieve the effect of phase adjustment

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

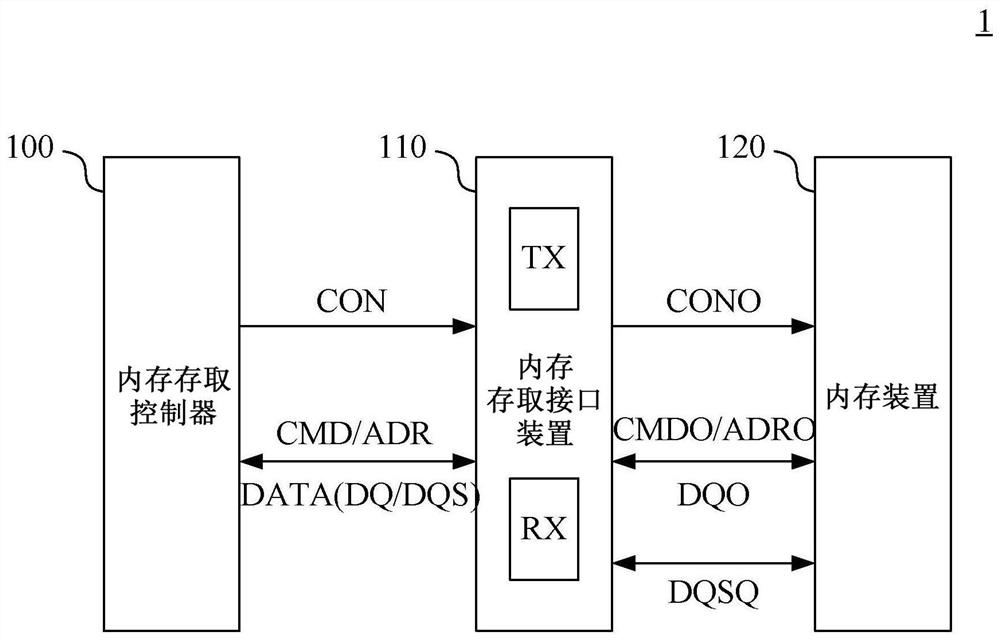

[0014] Please refer to figure 1 . figure 1 It is a block diagram of a memory 1 in an embodiment of the present invention. The memory 1 includes: a memory access controller 100 , a memory access interface device 110 and a memory device 120 .

[0015] The memory 1 can be electrically coupled with other modules through, for example, but not limited to, a system bus (not shown). For example, the memory 1 can be electrically coupled to a processor (not shown) through the system bus, so that the processor can access the memory 1 .

[0016] Among them, external access information, such as access information from the processor, can be received by the memory access controller 100 and sent to the memory access interface device 110, and then the memory access interface device 110 transmits the access information. The information is accessed in the memory device 120 .

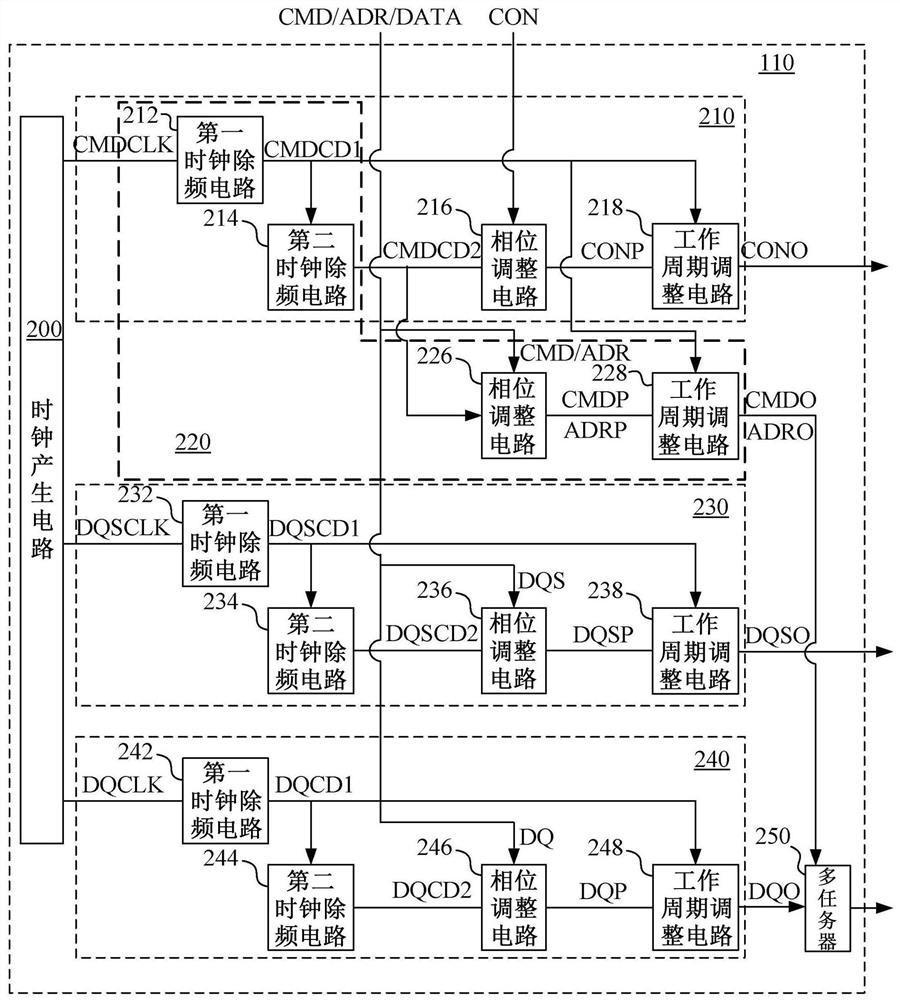

[0017] In more detail, in one embodiment, the memory access controller 100 can receive and transmit access informati...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More